正在加载图片...

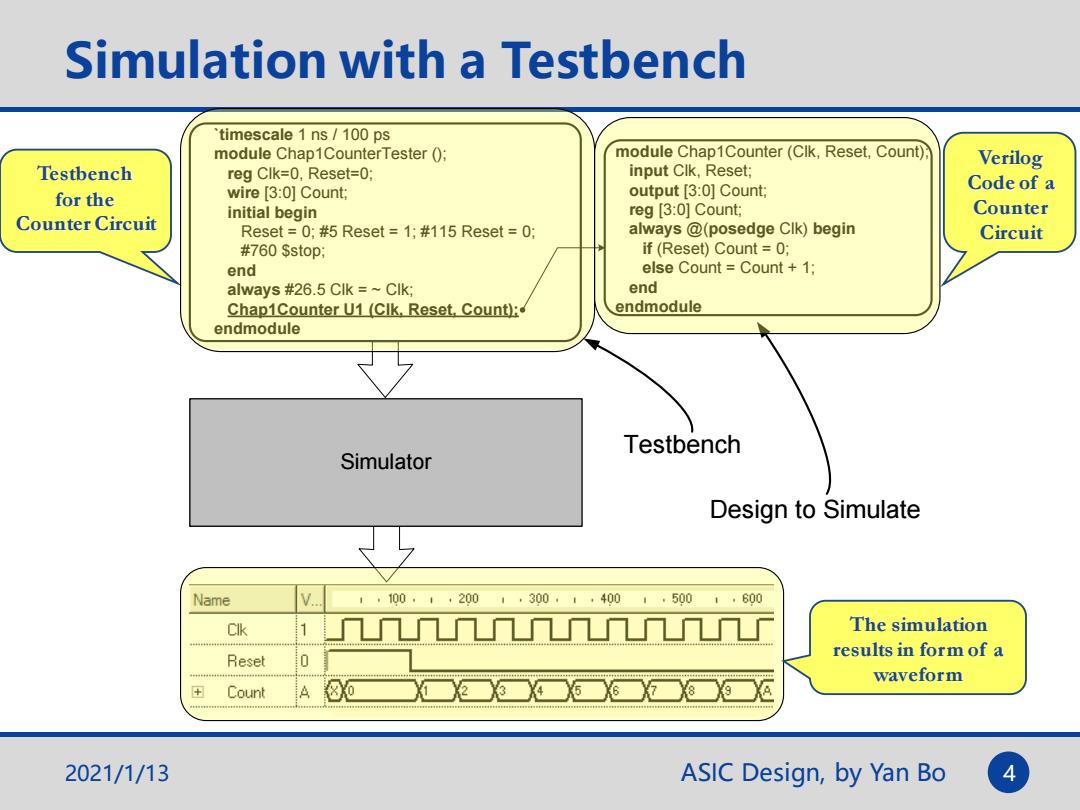

Simulation with a Testbench timescale 1 ns/100 ps module Chap1CounterTester ( module Chap1Counter(Clk,Reset,Count): input Clk,Reset: Verilog Testbench reg Clk=0,Reset=0; wire [3:0]Count; output [3:0]Count; Code of a for the Counter Circuit initial begin reg [3:0]Count; Counter Reset=0;#5 Reset=1;#115 Reset=0; always @(posedge Clk)begin Circuit #760 Sstop; if (Reset)Count 0; end else CountCount +1; always #26.5 Clk =Clk: end Chap1Counter U1 (CIk,Reset,Count); endmodule endmodule Testbench Simulator Design to Simulate Name 1,100.1·2001,300·1,4001.5001·600 Clk The simulation Reset results in form of a 0 waveform Count 80 3 2021/1/13 ASIC Design,by Yan Bo 4ASIC Design, by Yan Bo Simulation with a Testbench Testbench for the Counter Circuit Verilog Code of a Counter Circuit `timescale 1 ns / 100 ps module Chap1CounterTester (); reg Clk=0, Reset=0; wire [3:0] Count; initial begin Reset = 0; #5 Reset = 1; #115 Reset = 0; #760 $stop; end always #26.5 Clk = ~ Clk; Chap1Counter U1 (Clk, Reset, Count); endmodule module Chap1Counter (Clk, Reset, Count); input Clk, Reset; output [3:0] Count; reg [3:0] Count; always @(posedge Clk) begin if (Reset) Count = 0; else Count = Count + 1; end endmodule Simulator Testbench Design to Simulate The simulation results in form of a waveform 2021/1/13 4