正在加载图片...

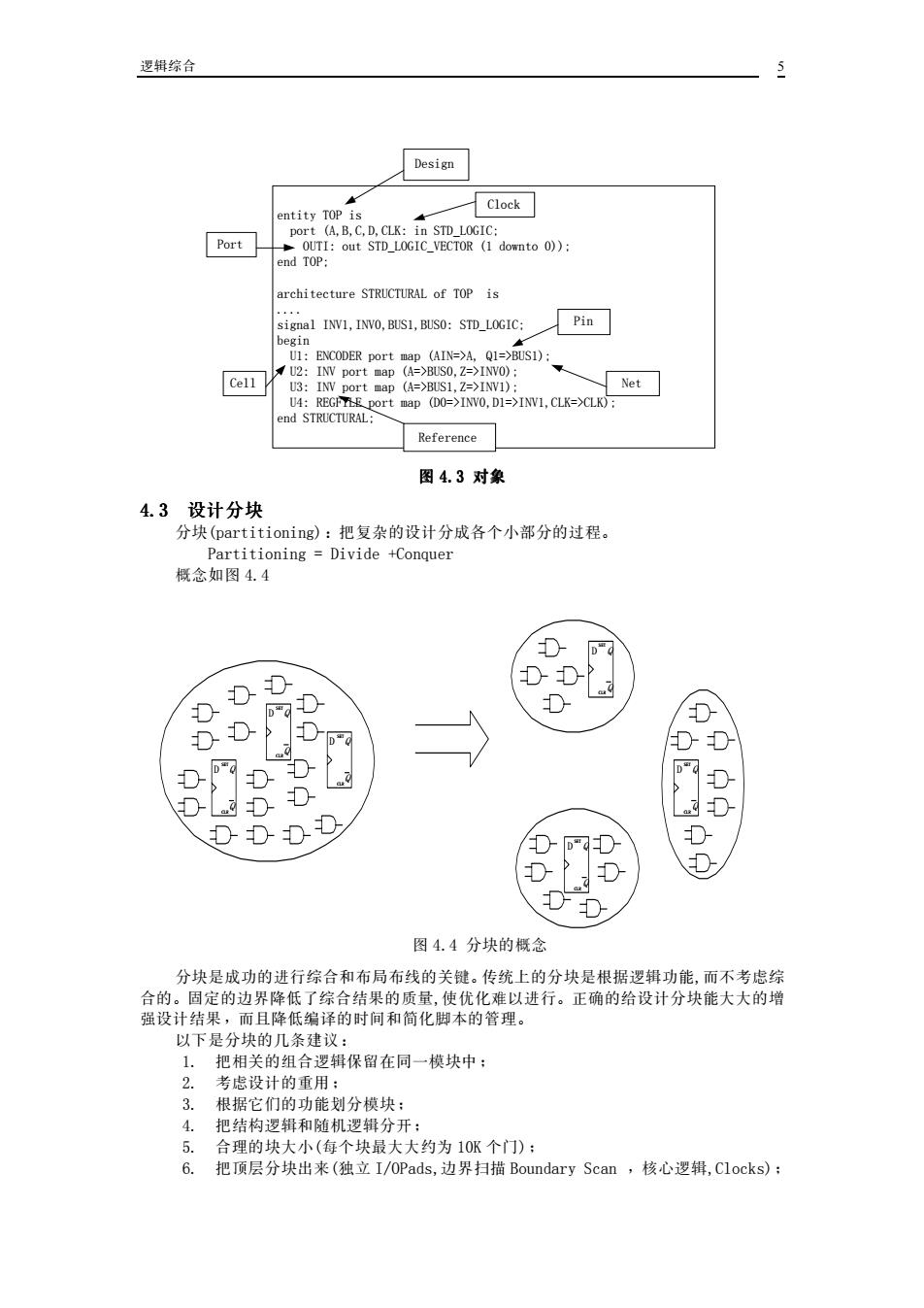

逻辑综合 5 Design Clock entity TOP is port (A,B,C,D,CLK:in STD_LOGIC: Port OUTI:out STD LOGIC_VECTOR (1 downto 0)); end TOP; architecture STRUCTURAL of TOP is signal INV1,INVO,BUS1,BUSO:STD_LOGIC: Pin begin U1:ENCODER port map (AIN=>A,Q1=>BUS1): U2:INV port map (A=>BUSO,Z=>INVO) Cell U3:INV port map (A=>BUS1,Z=>INV1); Net U4:REGFTLE port map (DO=>INVO,D1=>INV1,CLK=>CLK): end STRUCTURAL: Reference 图4.3对象 4.3设计分块 分块(partitioning):把复杂的设计分成各个小部分的过程。 Partitioning Divide +Conquer 概念如图4.4 D D D D D D D D"C D D D D D 0.0 D D 图4.4分块的概念 分块是成功的进行综合和布局布线的关键。传统上的分块是根据逻辑功能,而不考虑综 合的。固定的边界降低了综合结果的质量,使优化难以进行。正确的给设计分块能大大的增 强设计结果,而且降低编译的时间和简化脚本的管理。 以下是分块的几条建议: 1. 把相关的组合逻辑保留在同一模块中: 2.考虑设计的重用: 3. 根据它们的功能划分模块: 4. 把结构逻辑和随机逻辑分开: 5. 合理的块大小(每个块最大大约为10K个门): 6.把顶层分块出来(独立I/OPads,边界扫描Boundary Scan,核心逻辑,Clocks):逻辑综合 5 图 4.3 对象 4.3 设计分块 分块(partitioning):把复杂的设计分成各个小部分的过程。 Partitioning = Divide +Conquer 概念如图 4.4 图 4.4 分块的概念 分块是成功的进行综合和布局布线的关键。传统上的分块是根据逻辑功能,而不考虑综 合的。固定的边界降低了综合结果的质量,使优化难以进行。正确的给设计分块能大大的增 强设计结果,而且降低编译的时间和简化脚本的管理。 以下是分块的几条建议: 1. 把相关的组合逻辑保留在同一模块中; 2. 考虑设计的重用; 3. 根据它们的功能划分模块; 4. 把结构逻辑和随机逻辑分开; 5. 合理的块大小(每个块最大大约为 10K 个门); 6. 把顶层分块出来(独立 I/OPads,边界扫描 Boundary Scan ,核心逻辑,Clocks); entity TOP is port (A,B,C,D,CLK: in STD_LOGIC; OUTI: out STD_LOGIC_VECTOR (1 downto 0)); end TOP; architecture STRUCTURAL of TOP is .... signal INV1,INV0,BUS1,BUS0: STD_LOGIC; begin U1: ENCODER port map (AIN=>A, Q1=>BUS1); U2: INV port map (A=>BUS0,Z=>INV0); U3: INV port map (A=>BUS1,Z=>INV1); U4: REGFILE port map (D0=>INV0,D1=>INV1,CLK=>CLK); end STRUCTURAL; Design Clock Port Cell Reference Pin Net D Q Q SET CLR D Q Q SET CLR D Q Q SET CLR D Q Q SET CLR D Q Q SET CLR D Q Q SET CLR