正在加载图片...

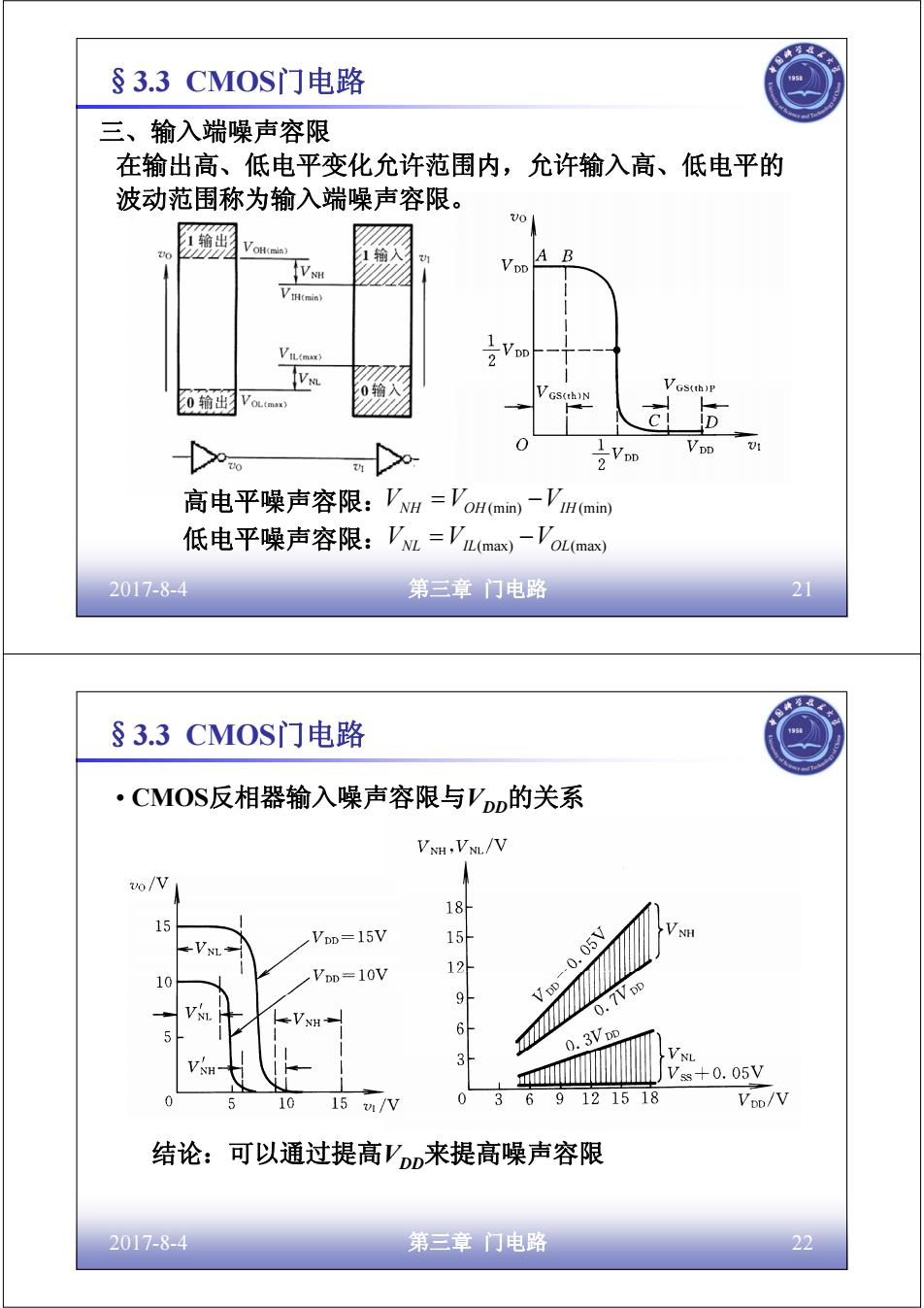

§3.3CMOS门电路 三、输入端噪声容限 在输出高、低电平变化允许范围内,允许输入高、低电平的 波动范围称为输入端噪声容限。 1输出 OH(min) 1输入 VoD VIL(mae) 0输出 0输入 VGs(th)N Vostth)P VoL(max) VDD 2 高电平噪声容限:V=(min-VHmm 低电平噪声容限:'z='umax-Vom 2017-8-4 第三章门电路 21 §3.3 CMOS门电路 ·CMOS反相器输入噪声容限与VoD的关系 VNH,VNL/V vo/V 18 15 VNL VDD=15V 15 10 Vpp=10V 12 9 Vm-0.05V 0.7VpD VNH- 6 0.3V pD 3 VNL Vss+0.05V 10 15/V 0 3 6 9 121518 VoD/V 结论:可以通过提高VoD来提高噪声容限 2017-8-4 第三章门电路 222017-8-4 第三章 门电路 21 三、输入端噪声容限 VNH =VOH (min) −VIH (min) §3.3 CMOS门电路 在输出高、低电平变化允许范围内,允许输入高、低电平的 波动范围称为输入端噪声容限。 VNL =VIL(max) −VOL(max) 高电平噪声容限: 低电平噪声容限: 2017-8-4 第三章 门电路 22 结论:可以通过提高VDD来提高噪声容限 §3.3 CMOS门电路 • CMOS反相器输入噪声容限与VDD的关系