中国绅学我术大学 University of Science and Technology of China 第三章门电路 本章目录 >3.1概述 >3.2半导体二极管门电路 >3.3CMOS门电路 >3.4TTL门电路 >3.5*ECL集成电路 >3.6Bi-CM0S电路 >3.7不同类型数字集成电路间的接口 2017-8-4 第三章门电路 §3.1概述 一、基本概念 门电路:实现基本逻辑运算和复合逻辑运算的单元电路。 常用的门电路:与门、或门、非门、与非门、或非门、 与或非门和异或门。 电子电路中用高、低电平分别表示二值逻辑的1和0两种逻辑 状态。 2017-8-4 第三章门电路

2017-8-4 第三章 门电路 1 第三章 门电路 第三章 门电路 本章目录 ¾3.1 概述 ¾3.2 半导体二极管门电路 ¾3.3 CMOS门电路 ¾3.4 TTL门电路 ¾3.5* ECL集成电路 ¾3.6 Bi-CMOS电路 ¾3.7 不同类型数字集成电路间的接口 2017-8-4 第三章 门电路 2 §3.1 概述 门电路:实现基本逻辑运算和复合逻辑运算的单元电路。 一、基本概念 电子电路中用高、低电平分别表示二值逻辑的1和0两种逻辑 状态。 常用的门电路:与门、或门、非门、与非门、或非门、 与或非门和异或门

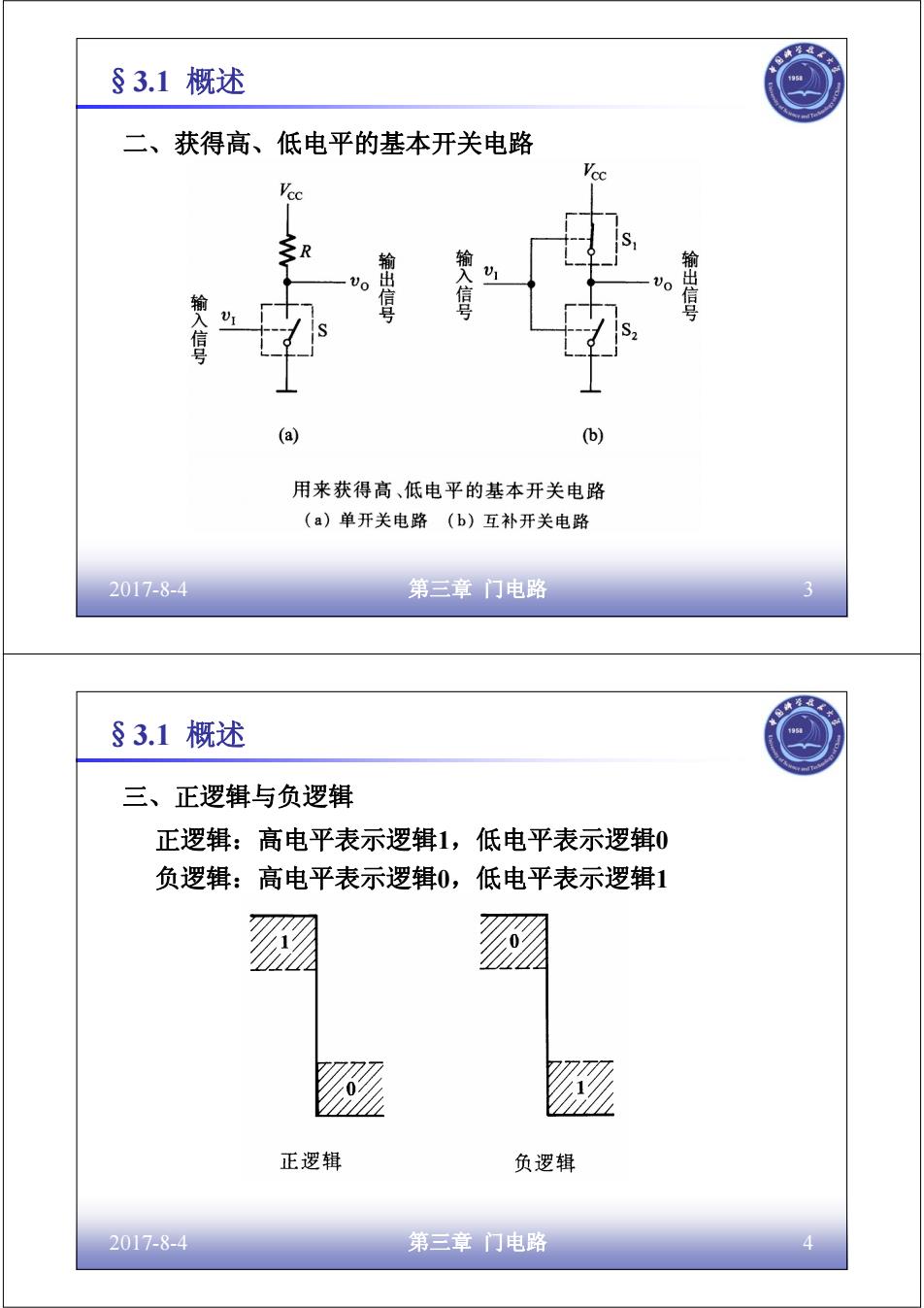

§3.1概述 二、获得高、低电平的基本开关电路 Vcc Vcc 输出信号 输入信号 00 输出信号 输入信号 (a) (b) 用来获得高、低电平的基本开关电路 (a)单开关电路(b)互补开关电路 2017-8-4 第三章门电路 §3.1概述 三、正逻辑与负逻辑 正逻辑:高电平表示逻辑1,低电平表示逻辑0 负逻辑:高电平表示逻辑0, 低电平表示逻辑1 正逻辑 负逻辑 2017-8-4 第三章门电路

2017-8-4 第三章 门电路 3 §3.1 概述 二、获得高、低电平的基本开关电路 2017-8-4 第三章 门电路 4 §3.1 概述 三、正逻辑与负逻辑 正逻辑:高电平表示逻辑1,低电平表示逻辑0 负逻辑:高电平表示逻辑0,低电平表示逻辑1

§3.1概述 四、数字集成电路的分类 1按集成度的高、低分类 小规模集成电路(小于10个门电路) 中规模集成电路(10~100个门电路) 大规模集成电路(100~10000个门电路) 超大规模集成电路(大于10000个门电路) 2按制造工艺分类 双极型、单极型、混合型 3按逻辑功能特点分类 标准化系列逻辑器件 专用集成电路 可编程逻辑器件(PLD) 2017-8-4 第三章门电路 §3.2半导体二极管门电路 3.2.1半导体二极管的开关特性 一、二极管的开关电路 设输入高电平:VIH-VcC 输入低电平:V=0 二极管D为理想开关 D yFVa D截止,vo=Vcc=VoI v=Vu D导通,vo=0=VoL 2017-8-4 第三章门电路 6

2017-8-4 第三章 门电路 5 §3.1 概述 四、数字集成电路的分类 2 按制造工艺分类 双极型、单极型、混合型 1 按集成度的高、低分类 小规模集成电路(小于10个门电路) 中规模集成电路(10~100个门电路) 大规模集成电路(100~10000个门电路) 超大规模集成电路(大于10000个门电路) 3 按逻辑功能特点分类 标准化系列逻辑器件 专用集成电路 可编程逻辑器件(PLD) 2017-8-4 第三章 门电路 6 • vI=VIH D截止,vO=VCC=VOH • vI=VIL D导通,vO=0=VOL §3.2 半导体二极管门电路 3.2.1 半导体二极管的开关特性 设输入高电平:VIH=VCC 输入低电平:VIL=0 二极管D为理想开关 一、二极管的开关电路

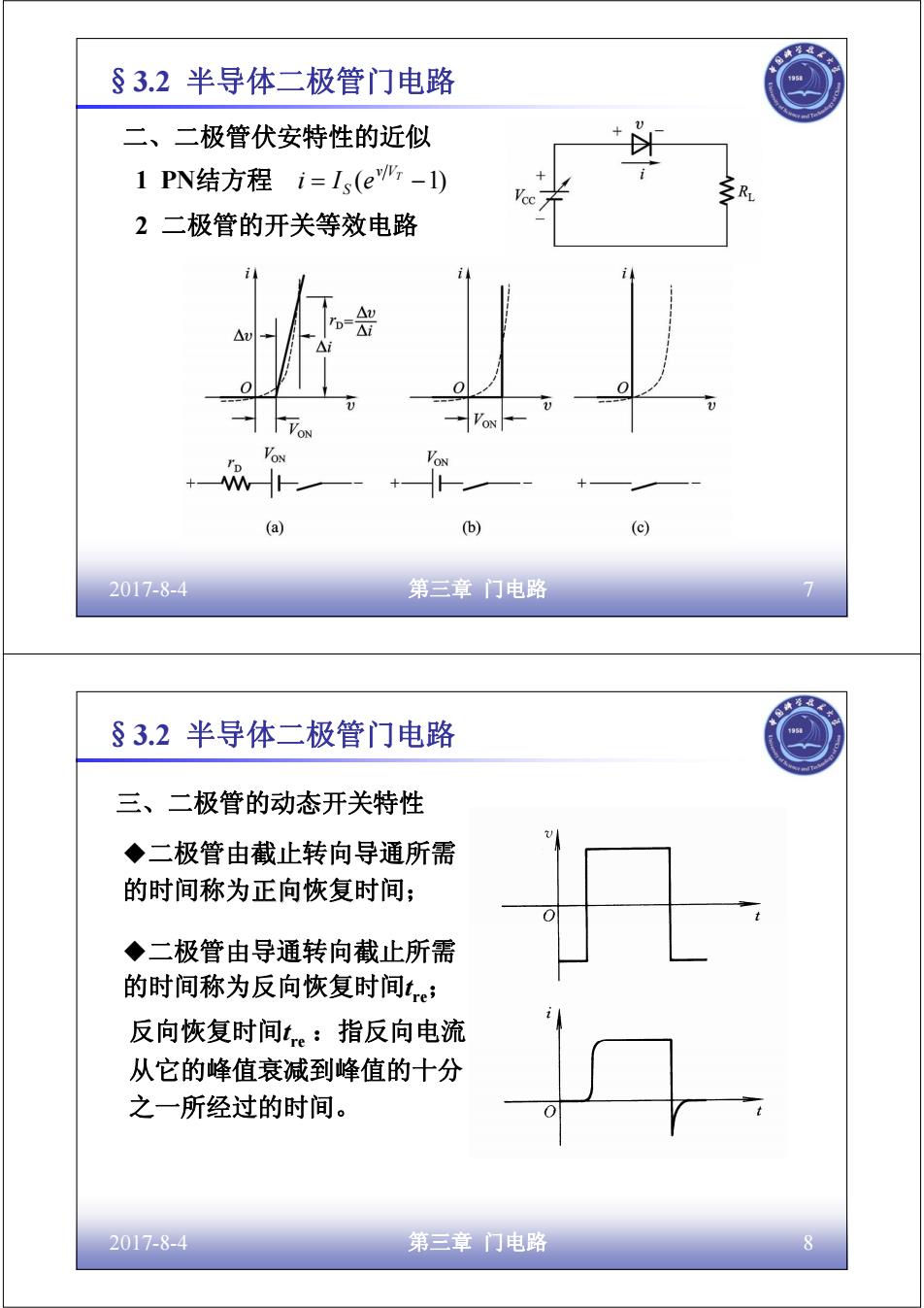

§3.2半导体二极管门电路 二、二极管伏安特性的近似 1PN结方程i=Is(e%-1) 2二极管的开关等效电路 △ VON + (a) (b) (c) 2017-8-4 第三章门电路 §3.2半导体二极管门电路 三、二极管的动态开关特性 ◆二极管由截止转向导通所需 的时间称为正向恢复时间; ◆二极管由导通转向截止所需 的时间称为反向恢复时间te: 反向恢复时间t。:指反向电流 从它的峰值衰减到峰值的十分 之一所经过的时间。 2017-8-4 第三章门电路 8

2017-8-4 第三章 门电路 7 §3.2 半导体二极管门电路 二、二极管伏安特性的近似 1 PN结方程 = ( −1) VT v S i I e 2 二极管的开关等效电路 2017-8-4 第三章 门电路 8 §3.2 半导体二极管门电路 三、二极管的动态开关特性 二极管由导通转向截止所需 的时间称为反向恢复时间tre; 二极管由截止转向导通所需 的时间称为正向恢复时间; 正向 反向恢复时间tre :指反向电流 从它的峰值衰减到峰值的十分 之一所经过的时间

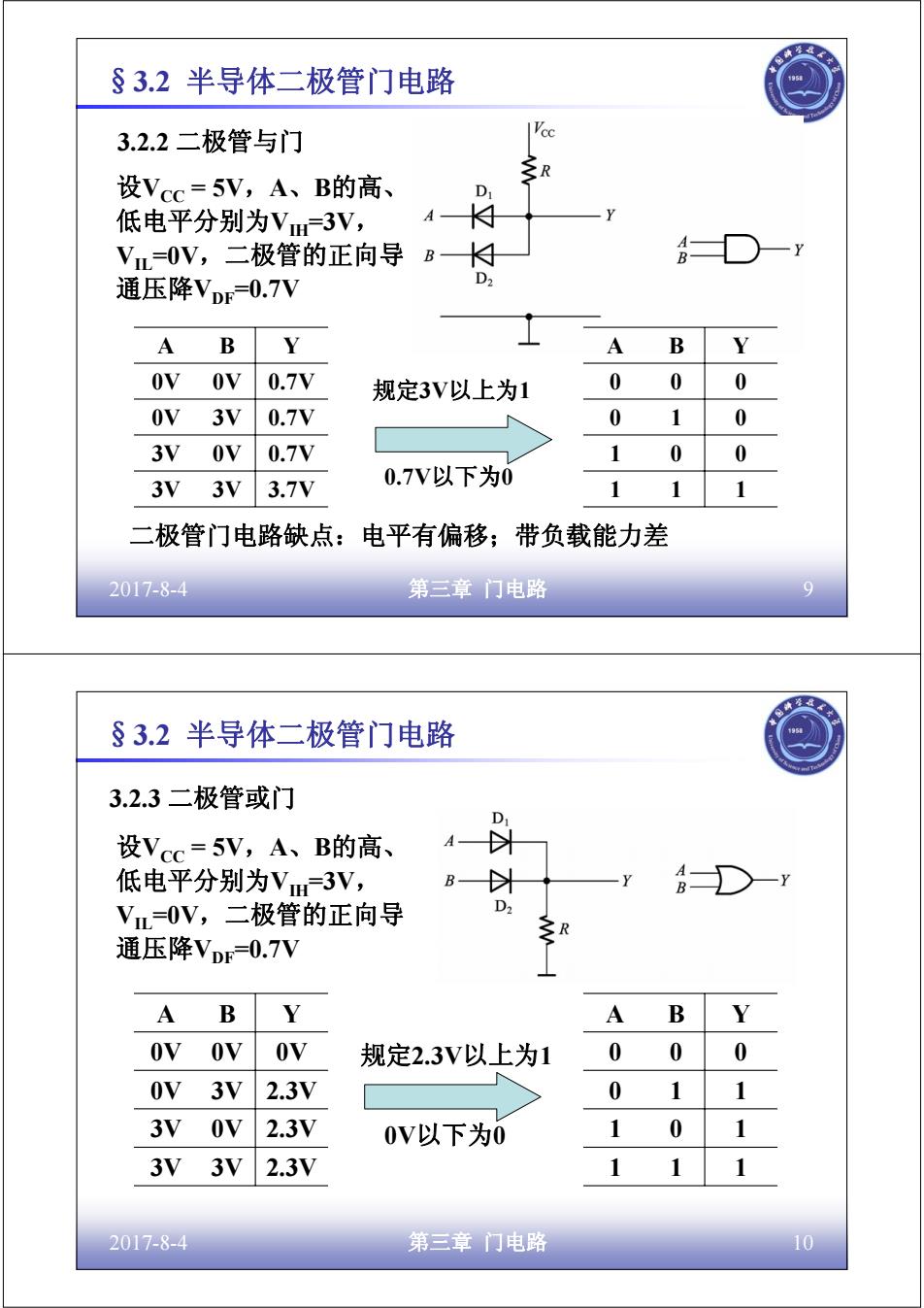

§3.2半导体二极管门电路 3.2.2二极管与门 设Vcc=5V,A、B的高、 R D 低电平分别为Vm3V, A Vm=OV,二极管的正向导 D 通压降VDr=0.7V D2 A B Y A B Y Ov Ov 0.7V 规定3V以上为1 0 0 0 OV 3V 0.7V 0 1 0 3V 0V 0.7V 0 0 3V 3V 3.7V 0.7V以下为0 1 二极管门电路缺点:电平有偏移;带负载能力差 2017-8-4 第三章门电路 9 §3.2半导体二极管门电路 3.2.3二极管或门 设Vcc=5V,A、B的高、 A 低电平分别为Vm3V, B V=0V,二极管的正向导 D2 通压降Vo=0.7V A B Y A B Y Ov Ov ov 规定2.3V以上为1 0 0 0 OV 3V 2.3V 0 1 1 3V Ov 2.3V 0V以下为0 1 0 1 3V 3V 2.3V 2017-8-4 第三章门电路 10

2017-8-4 第三章 门电路 9 3V 3V 3.7V 3V 0V 0.7V 0V 3V 0.7V 0V 0V 0.7V A B Y 1 1 1 1 0 0 0 1 0 0 0 0 A B Y 规定3V以上为1 0.7V以下为0 §3.2 半导体二极管门电路 3.2.2 二极管与门 设VCC = 5V,A、B的高、 低电平分别为VIH=3V, VIL=0V,二极管的正向导 通压降VDF=0.7V 二极管门电路缺点:电平有偏移;带负载能力差 2017-8-4 第三章 门电路 10 3.2.3 二极管或门 3V 3V 2.3V 3V 0V 2.3V 0V 3V 2.3V 0V 0V 0V A B Y 1 1 1 1 0 1 0 1 1 0 0 0 A B Y 规定2.3V以上为1 0V以下为0 §3.2 半导体二极管门电路 设VCC = 5V,A、B的高、 低电平分别为VIH=3V, VIL=0V,二极管的正向导 通压降VDF=0.7V

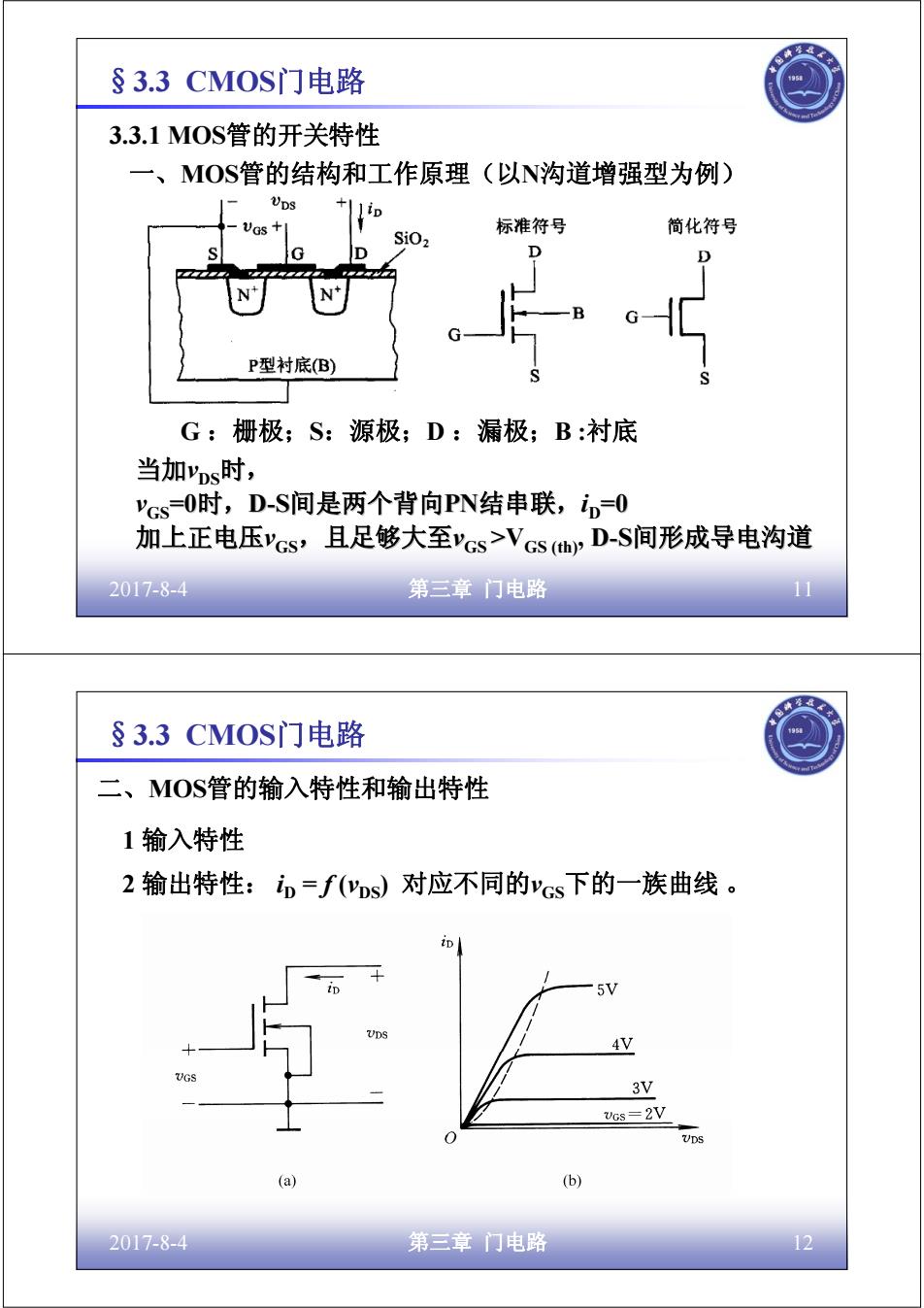

§3.3 CMOS门电路 3.3.1M0S管的开关特性 一、 MOS管的结构和工作原理(以N沟道增强型为例) UDS 标准符号 简化符号 SiO2 G D P型衬底(B) G:栅极;S:源极;D:漏极;B:衬底 当加yDs时, vcs=0时,D-S间是两个背向PN结串联,iD=0 加上正电压ycs,且足够大至vcs>Vcs,D-S间形成导电沟道 2017-8-4 第三章门电路 §3.3 CMOS门电路 二、MOS管的输入特性和输出特性 1输入特性 2输出特性:iD=f(Ds)对应不同的vcs下的一族曲线。 iD ip 5V UDS AV 3V VGs=2V VDS (a) (b) 2017-8-4 第三章门电路 12

2017-8-4 第三章 门电路 11 §3.3 CMOS门电路 3.3.1 MOS管的开关特性 G :栅极;S:源极;D :漏极;B :衬底 一、MOS管的结构和工作原理(以N沟道增强型为例) 当加vDS时, vGS=0时,D-S间是两个背向PN结串联,iD=0 加上正电压vGS,且足够大至vGS >VGS (th), D-S间形成导电沟道 2017-8-4 第三章 门电路 12 §3.3 CMOS门电路 二、MOS管的输入特性和输出特性 1 输入特性 2 输出特性: iD = f (vDS) 对应不同的vGS下的一族曲线

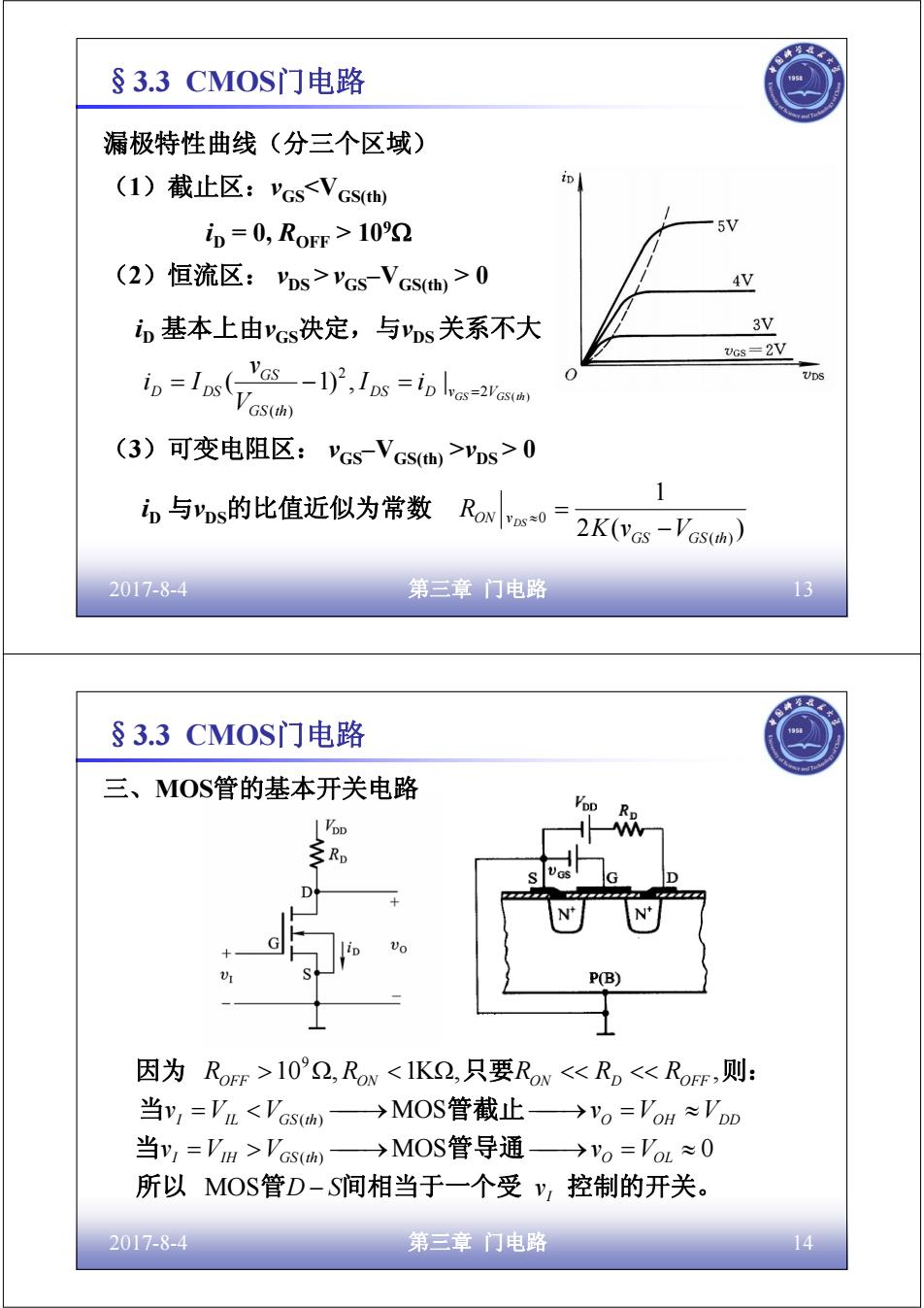

§3.3CMOS门电路 漏极特性曲线(分三个区域) (1)截止区:'cs'Gs-VGs>0 4V iD基本上由vcs决定,与yns关系不大 3V VGs=2V ip=Ins(Ys1),ps=ip VDS Vas(h) (3)可变电阻区:'Gs-Vcsh>vDs>0 ,与ns的比值近似为常数Rvs0 2K(Vcs-VGs(h) 2017-8-4 第三章门电路 13 §3.3CMOS门电路 三、MOS管的基本开关电路 Rp D P(B) 因为RoFF>102,RoNVsw→MOS管导通→vo=VL≈0 所以MOS管D-S间相当于一个受y,控制的开关。 2017-8-4 第三章门电路 14

2017-8-4 第三章 门电路 13 §3.3 CMOS门电路 漏极特性曲线(分三个区域) (1)截止区:vGS vGS–VGS(th) > 0 2 ( ) 2 ( ) ( 1) , | GS VGS th DS D v GS th GS D DS I i V v i I = − = = iD = 0, ROFF > 109Ω iD 基本上由vGS决定,与vDS关系不大 (3)可变电阻区: vGS–VGS(th) >vDS > 0 2 ( ) 1 ( ) 0 GS GS th ON v K v V R DS − i ≈ = D 与vDS的比值近似为常数 2017-8-4 第三章 门电路 14 因为 ROFF >109 Ω, RON VGS (th) ⎯⎯→MOS管导通 ⎯⎯→vO =VOL ≈ 0 所以 MOS管D − S间相当于一个受 vI 控制的开关

§3.3CMOS门电路 四、MOS管的开关等效电路 D G (a) 6) 截止状态 导通状态 五、MOS管的四种类型 N沟道增强型、P沟道增强型、N沟道耗尽型、P沟道耗尽型 2017-8-4 第三章门电路 15 §3.3 CMOS门电路 ◆P沟道增强型 PMOS管的结构和工作原理 UDS 标准符号 简化符号 0 N型衬底B) 当加yos时, vGs=0时,D-S间是两个背向PN结串联,iD=0 加上负电压Gs,且足够大至vcs>VGs (th)l,D-S间形成导电沟道 2017-8-4 第三章门电路 16

2017-8-4 第三章 门电路 15 截止状态 导通状态 §3.3 CMOS门电路 四、 MOS管的开关等效电路 五、MOS管的四种类型 N沟道增强型、P沟道增强型、N沟道耗尽型、P沟道耗尽型 2017-8-4 第三章 门电路 16 §3.3 CMOS门电路 P沟道增强型 当加vDS时, vGS=0时,D-S间是两个背向PN结串联,iD=0 加上负电压vGS,且足够大至| vGS | >|VGS (th) |,D-S间形成导电沟道 PMOS管的结构和工作原理

§3.3CMOS门电路 3.3.2CMOS反相器的电路结构和工作原理 一、CMOS反相器的电路结构 o G2 D G p+ N P+ N P阱 N型衬底 (a)结构示意图 (b)电路图 2017-8-4 第三章门电路 §3.3 CMOS门电路 ●工作原理 设T和T的开启电压为Vsh)p和VGs(N VpD VasoN =Yas>asVasop T和I,具有相同的导通内阻RoN, T和T,具有相同的截止内阻RoF (I)y,='m='oo时 VGsI=0VGSuN T截止,T,导通,VoL≈0 (2)y,='L=0时 Y'GSI=VDD >VGsPYGS2 =0<VGsN T导通,T截止,VoH≈VD 2017-8-4 第三章门电路 18

2017-8-4 第三章 门电路 17 3.3.2 CMOS反相器的电路结构和工作原理 §3.3 CMOS门电路 一、CMOS反相器的电路结构 (a)结构示意图 (b)电路图 2017-8-4 第三章 门电路 18 OFF ON GS th N GS th P DD GS th N GS th P GS th P GS th N T T R T T R V V V V V T T V V 和 具有相同的截止内阻 和 具有相同的导通内阻 ,且 设 和 的开启电压为 和 , 1 2 1 2 ( ) ( ) ( ) ( ) 1 2 ( ) ( ) , = > + , §3.3 CMOS门电路 z工作原理 (2)vI =VIL = 0时 GS DD GS th P GS VGS th N v V V v 1 ( ) 2 0 ( ) = > , = 0 T1截止,T2导通,VOL ≈

§3.3 CMOS门电路 二、电压传输特性和电流传输特性 1电压传输特性 输出电压随输入电压变化的曲线。Vm A B *AB段:y,'op-VGsamP VGstthiP I,导通,T截止→'o=VoL≈0 *BC段:VGstN'o-VcsomP VGs(th)P T,导通,T截止→io≈0 VGs(th)N C D *BC段:'Gshw<y,<VoD-VcscP VDD 2 T,T,同时导通,有电流in流过T和T, 2017-8-4 第三章门电路 20

2017-8-4 第三章 门电路 19 O OH DD I GS th N T T v V V AB v V ⇒ = ≈ ∗ − O OL I DD GS th P T T v V CD v V V 导通, 截止 段: GS th N I VDD VGS th P BC V v ∗ 段: ( ) − D I DD GS th P T T i CD v V V 导通, 截止 段: GS th N I VDD VGS th P BC V v ( ) < < − ( ) ∗ 段: 1 2 1 2 T ,T 同时导通,有电流iD流过T和T