中国绅学我术大学 University of Science and Technology of China 第11章常用的VLSI象统部件 本章目录 11.1多路选择器 11.2二进制译码器 11.3相等检测器和比较器 ÷11.4优先权编码器 11.5移位和循环操作 11.6锁存器 11.7D触发器 11.8寄存器 g11.9 综合的作用 2018-9-5 第11章常用的VLSI系统部件 组合逻辑电路与时序逻辑电路 组合 In 组合 Out In 逻辑电路 Out 逻辑电路 状态 组合逻辑电路 时序逻辑电路 Out=f(In) Out=f(In,Previous In) 2018-9-5 第11章常用的VLSI系统部件

2018-9-5 第11章 常用的VLSI系统部件 1 第 11 章 常用的 VLSI系统部件 本章目录 11.1 多路选择器 11.2 二进制译码器 11.3 相等检测器和比较器 11.4 优先权编码器 11.5 移位和循环操作 11.6 锁存器 11.7 D触发器 11.8 寄存器 11.9 综合的作用 2018-9-5 第11章 常用的VLSI系统部件 2 组合逻辑电路 时序逻辑电路 Out = f (In) Out = f (In,Previous In) 组合 In 逻辑电路 Out Out In 状态 组合 逻辑电路 组合逻辑电路与时序逻辑电路

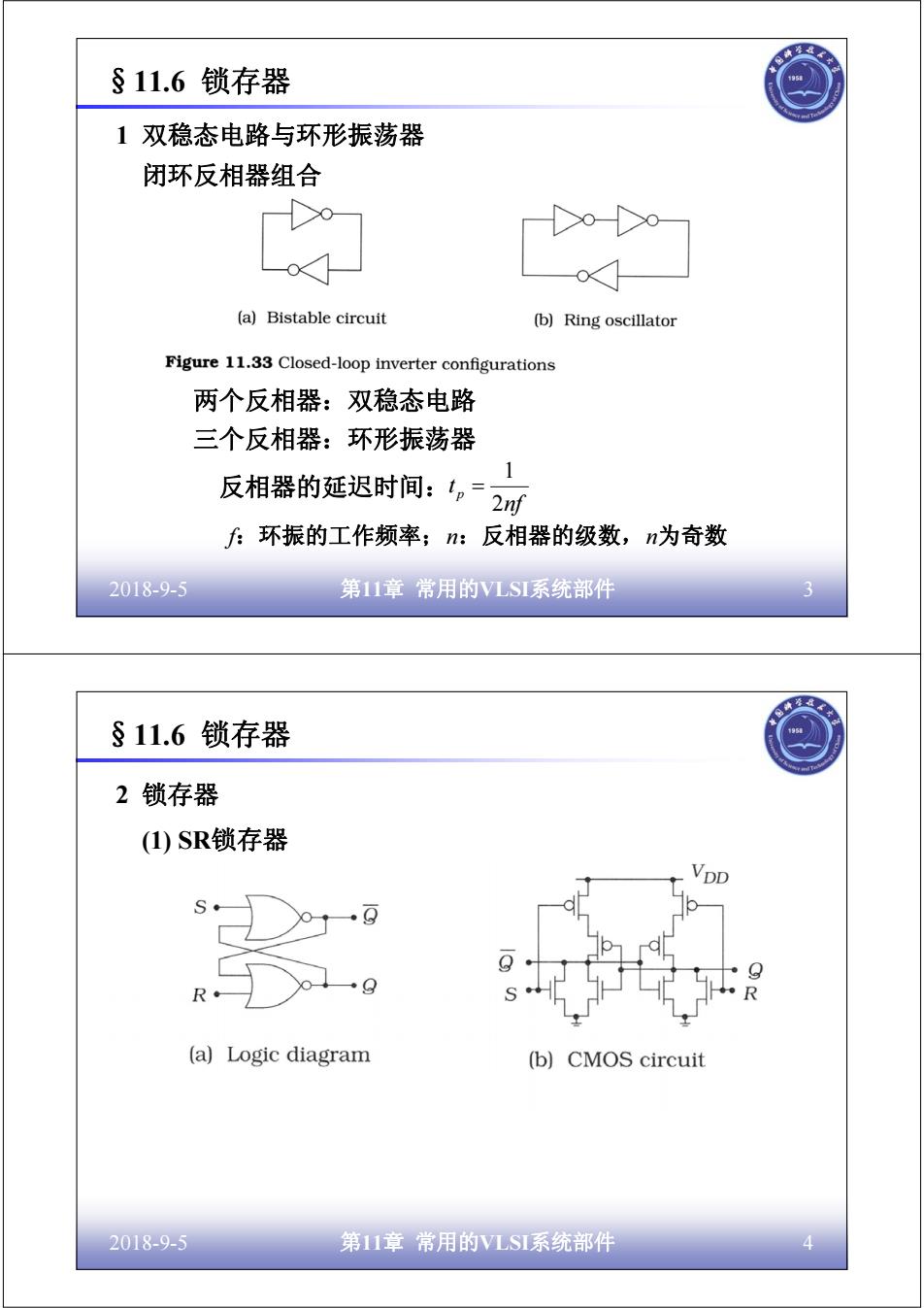

§11.6锁存器 © 1 双稳态电路与环形振荡器 闭环反相器组合 (a)Bistable circuit (b)Ring oscillator Figure 11.33 Closed-loop inverter configurations 两个反相器:双稳态电路 三个反相器:环形振荡器 反相器的延迟时间:。2m :环振的工作频率;:反相器的级数,n为奇数 2018-9-5 第11章常用的VLSI系统部件 §11.6锁存器 2锁存器 (1)SR锁存器 (a)Logic diagram (b)CMOS circuit 2018-9-5 第11章常用的VLSI系统部件

2018-9-5 第11章 常用的VLSI系统部件 3 §11.6 锁存器 1 双稳态电路与环形振荡器 闭环反相器组合 两个反相器:双稳态电路 三个反相器:环形振荡器 反相器的延迟时间: nf t p 2 1 = f:环振的工作频率;n:反相器的级数,n为奇数 2018-9-5 第11章 常用的VLSI系统部件 4 2 锁存器 (1) SR锁存器 1 §11.6 锁存器

§11.6锁存器 (2)钟控SR锁存器 (a)Logic diagram (b)CMOS circuit 2018-9-5 第11章常用的VLSI系统部件 §11.6锁存器 (3)钟控D锁存器 AOI D D D Q En p+9 En (a)Symbol (b)Logic diagram Figure 11.31 Gated D-latch with Enable control 2018-9-5 第11章常用的VLSI系统部件 6

2018-9-5 第11章 常用的VLSI系统部件 5 (2) 钟控SR锁存器 1 §11.6 锁存器 2018-9-5 第11章 常用的VLSI系统部件 6 §11.6 锁存器 (3) 钟控D锁存器

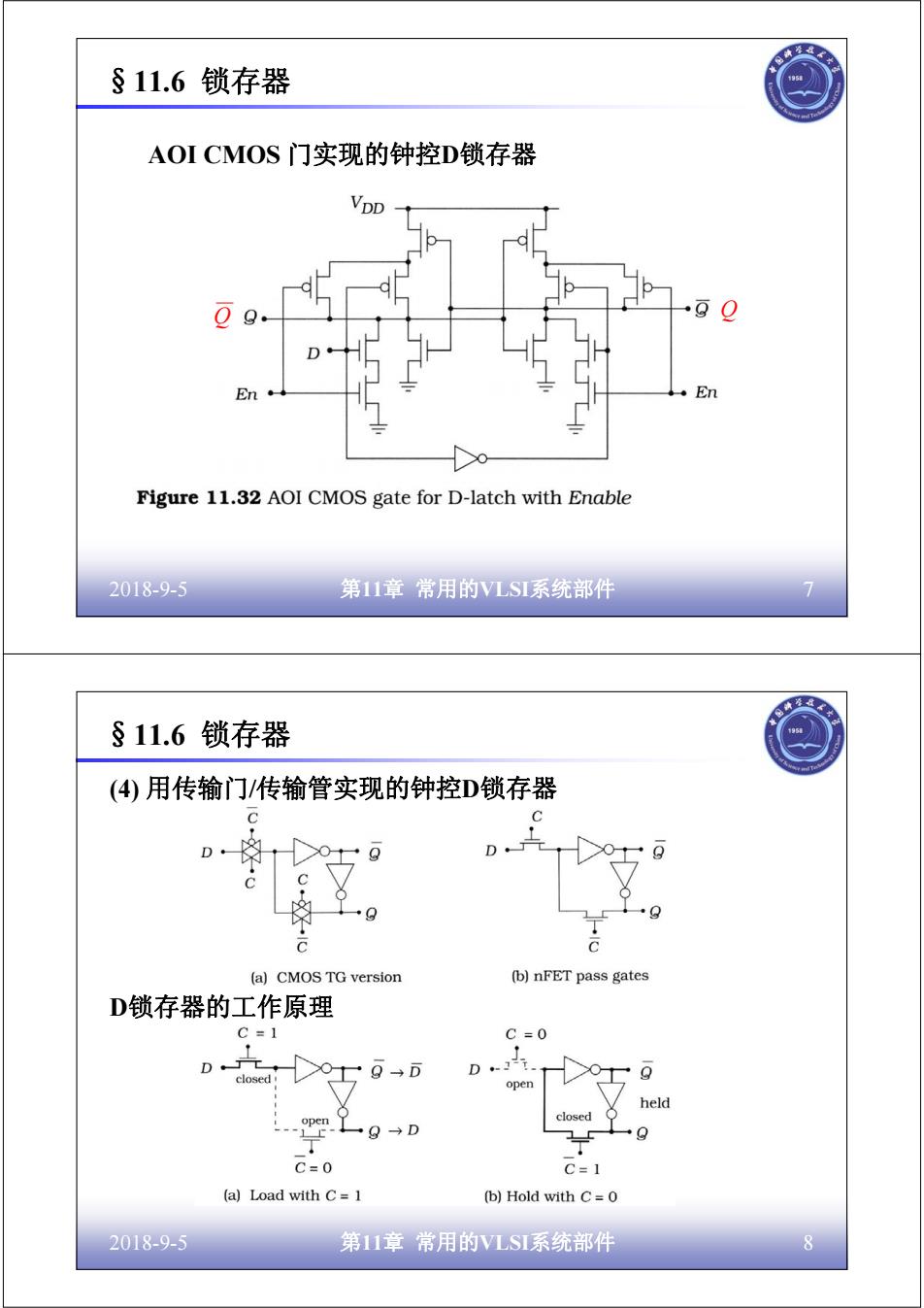

§11.6锁存器 AOI CMOS门实现的钟控D锁存器 VpD q。 .90 D En En Figure 11.32 AOI CMOS gate for D-latch with Enable 2018-9-5 第11章常用的VLSI系统部件 §11.6锁存器 (4)用传输门/传输管实现的钟控D锁存器 D (a)CMOS TG version (b)nFET pass gates D锁存器的工作原理 C=1 C=0 D无 closed open held p.g→D closed C=0 C=1 (a)Load with C=1 (b)Hold with C=0 2018-9-5 第11章常用的VLSI系统部件 8

2018-9-5 第11章 常用的VLSI系统部件 7 §11.6 锁存器 AOI CMOS 门实现的钟控D锁存器 Q Q 2018-9-5 第11章 常用的VLSI系统部件 8 §11.6 锁存器 (4) 用传输门/传输管实现的钟控D锁存器 D锁存器的工作原理

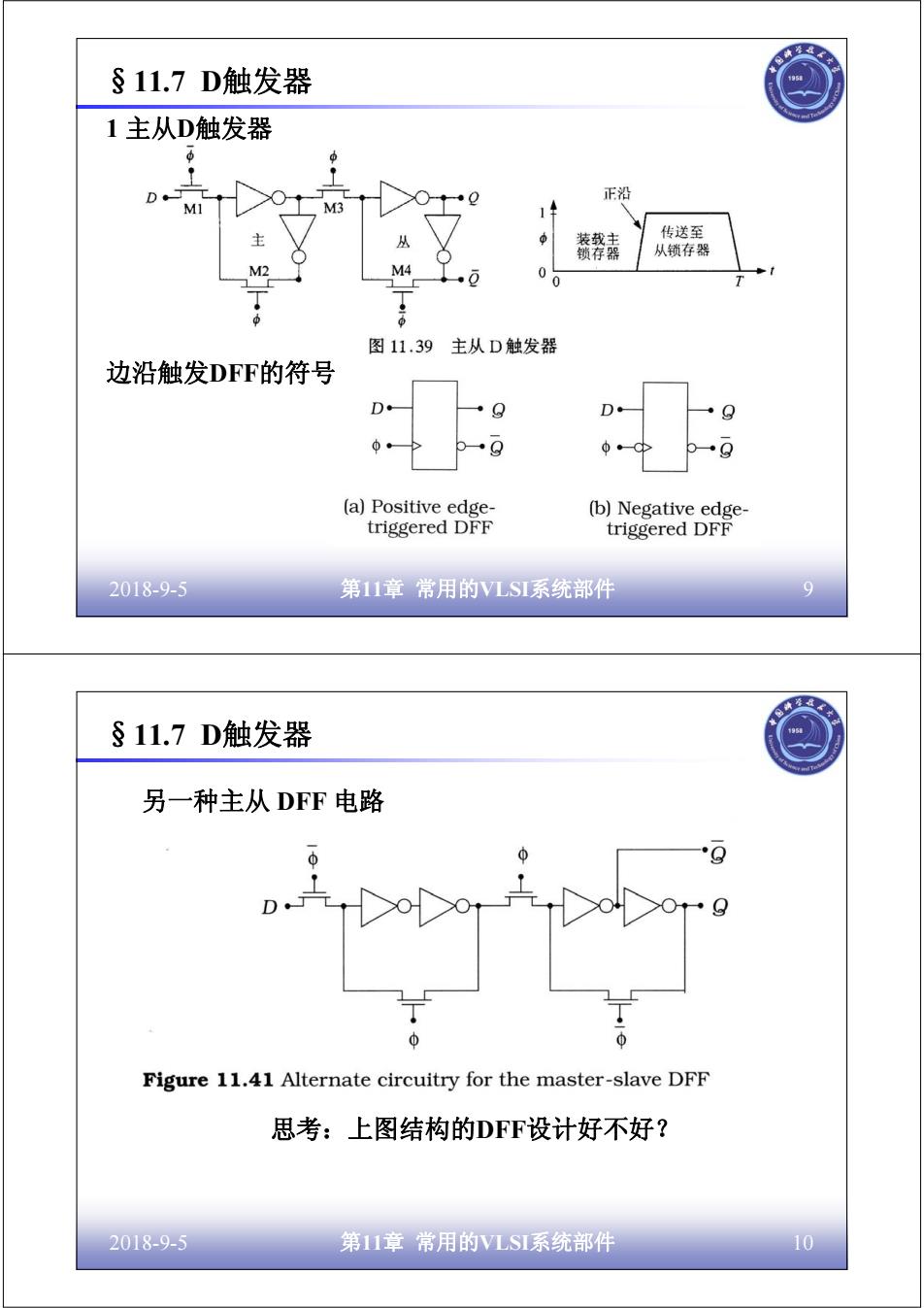

§11.7D触发器 1主从D触发器 D 正沿 1 装载主 传送至 锁存器 从锁存器 M4 0 0 图11.39主从D触发器 边沿触发DFF的符号 D D 9 0。 (a)Positive edge- (b)Negative edge- triggered DFF triggered DFF 2018-9-5 第11章常用的VLSI系统部件 §11.7D触发器 另一种主从DFF电路 0 Figure 11.41 Alternate circuitry for the master-slave DFF 思考:上图结构的DFF设计好不好? 2018-9-5 第11章常用的VLSI系统部件 10

2018-9-5 第11章 常用的VLSI系统部件 9 §11.7 D触发器 1 主从D触发器 边沿触发DFF的符号 2018-9-5 第11章 常用的VLSI系统部件 10 §11.7 D触发器 另一种主从 DFF 电路 思考:上图结构的DFF设计好不好?

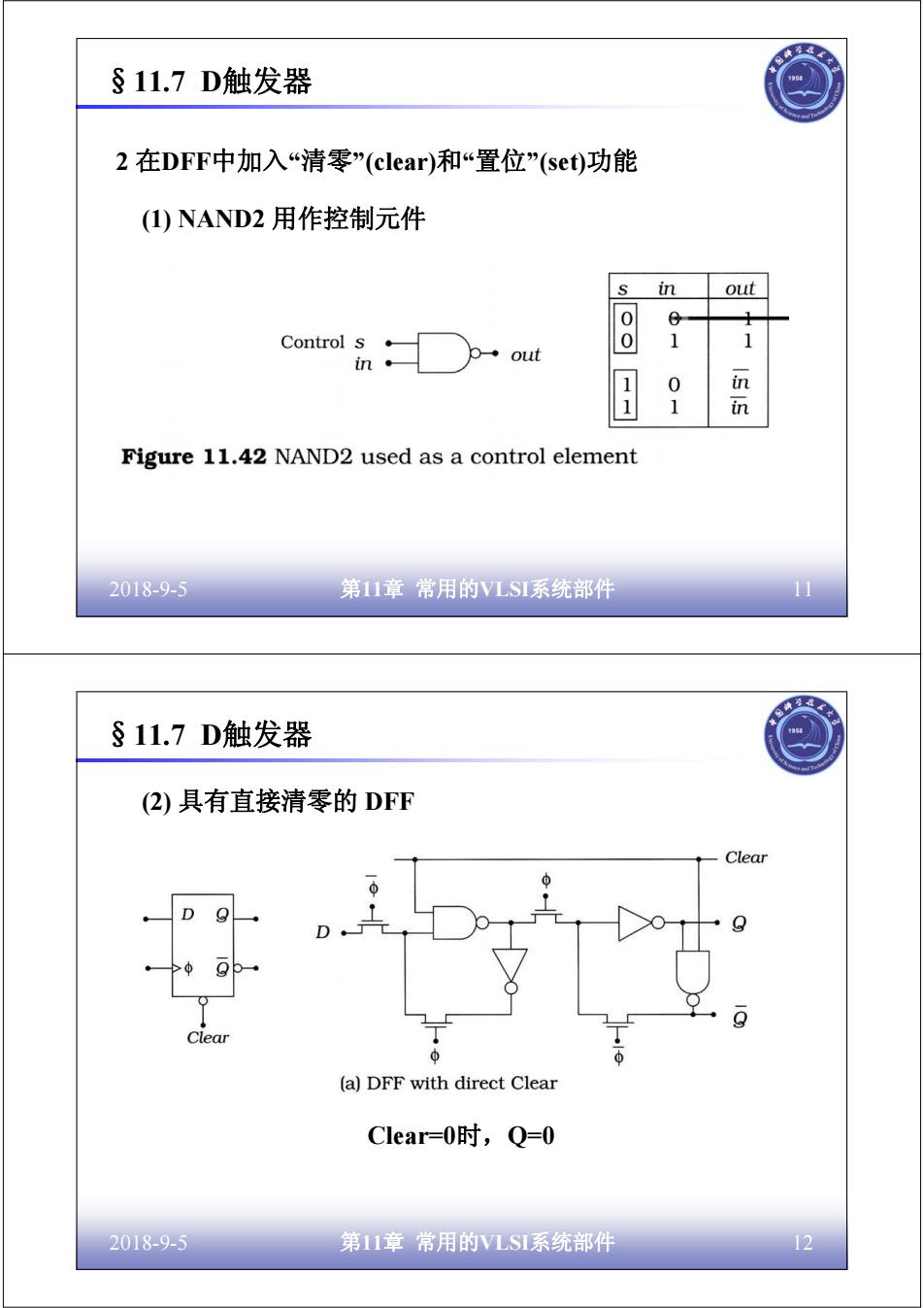

§11.7D触发器 2在DFF中加入“清零”(clear)和“置位”(set)功能 (1)NAND2用作控制元件 n out 0 6 Control s 1 1 n out 0 in i 1 Figure 11.42 NAND2 used as a control element 2018-9-5 第11章常用的VLSI系统部件 §11.7D触发器 (2)具有直接清零的DFF Clear Clear (a)DFF with direct Clear Clear-=O时,Q=0 2018-9-5 第11章常用的VLSI系统部件 12

2018-9-5 第11章 常用的VLSI系统部件 11 §11.7 D触发器 (1) NAND2 用作控制元件 2 在DFF中加入“清零”(clear)和“置位”(set)功能 2018-9-5 第11章 常用的VLSI系统部件 12 §11.7 D触发器 (2) 具有直接清零的 DFF Clear=0时,Q=0

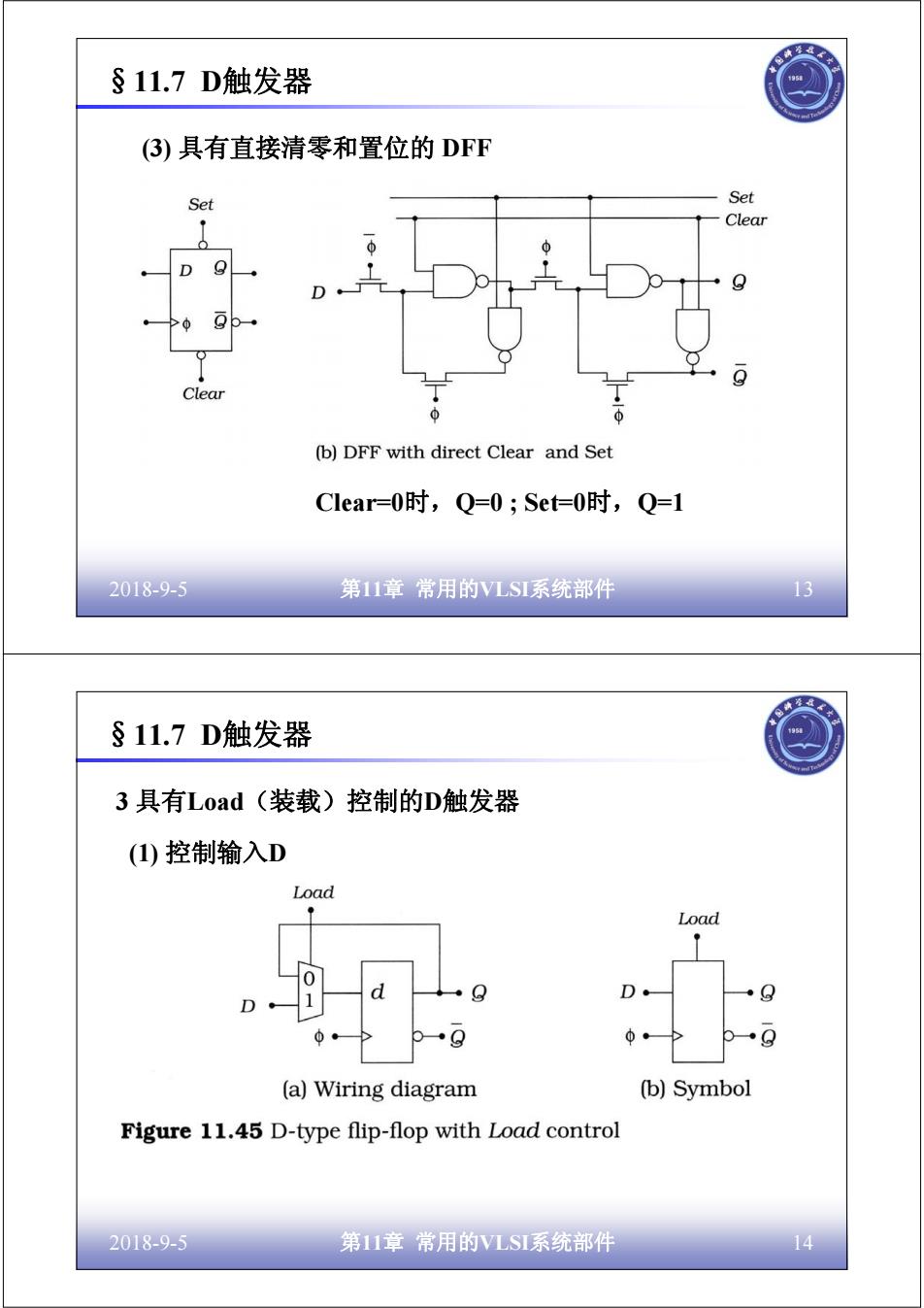

§11.7D触发器 (3)具有直接清零和置位的DF℉ Set Set Clear Clear (b)DFF with direct Clear and Set Clear=-0时,Q=0;Set=0时,Q=1 2018-9-5 第11章常用的VLSI系统部件 13 §11.7D触发器 3具有Load(装载)控制的D触发器 (1)控制输入D Load Load a (a)Wiring diagram (b)Symbol Figure 11.45 D-type flip-flop with Load control 2018-9-5 第11章常用的VLSI系统部件 14

2018-9-5 第11章 常用的VLSI系统部件 13 §11.7 D触发器 (3) 具有直接清零和置位的 DFF Clear=0时,Q=0 ; Set=0时,Q=1 2018-9-5 第11章 常用的VLSI系统部件 14 §11.7 D触发器 3 具有Load(装载)控制的D触发器 (1) 控制输入D

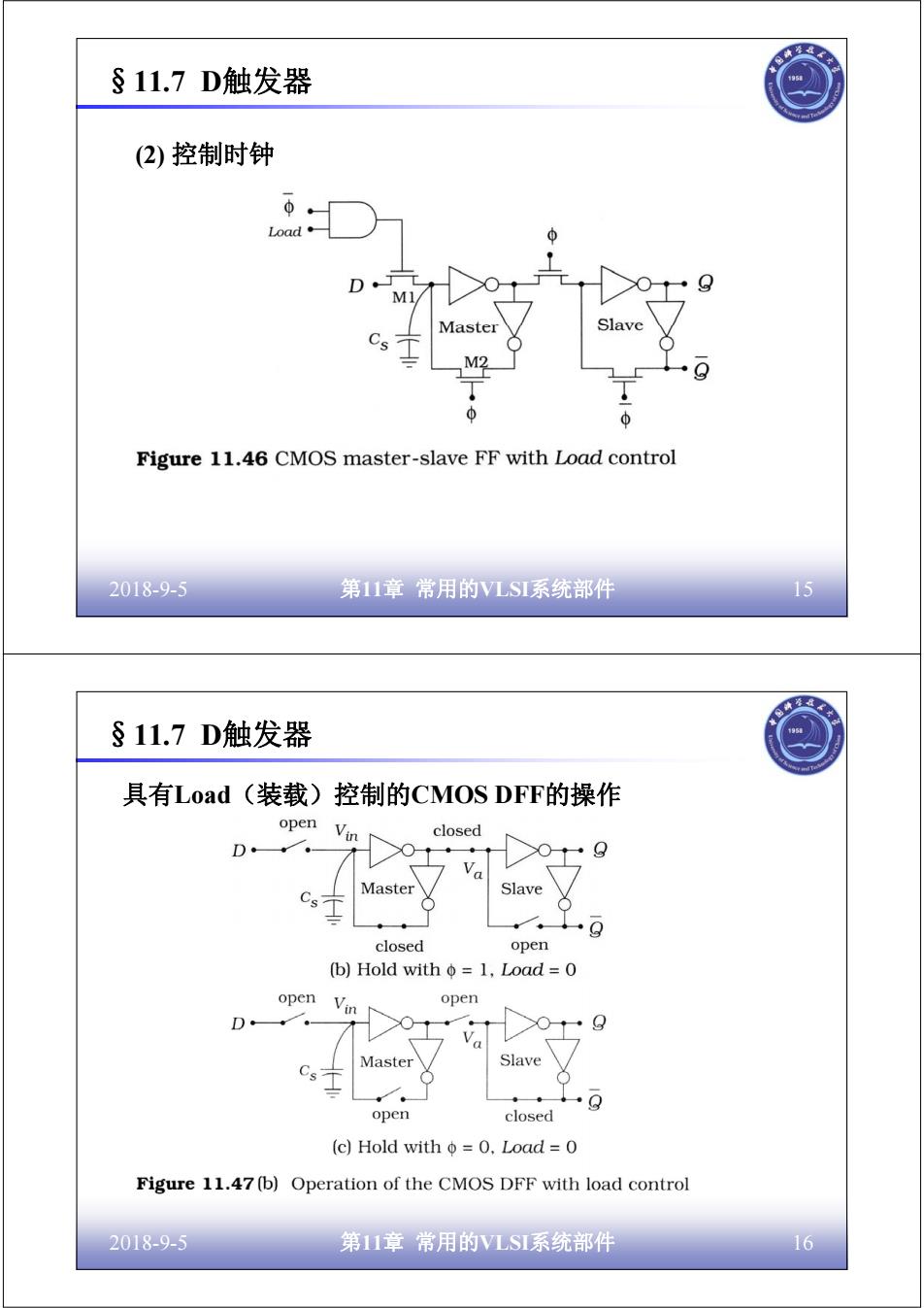

§11.7D触发器 (2)控制时钟 Load M2 Figure 11.46 CMOS master-slave FF with Load control 2018-9-5 第11章常用的VLSI系统部件 15 §11.7D触发器 具有Load(装载)控制的CMOS DFFI的操作 open closed D· Master Slave closed open (b)Hold with =1,Load=0 open Vin open D Cs Master Slave open closed (c)Hold with=0,Load=0 Figure 11.47(b)Operation of the CMOS DFF with load control 2018-9-5 第11章常用的VLSI系统部件 16

2018-9-5 第11章 常用的VLSI系统部件 15 §11.7 D触发器 (2) 控制时钟 2018-9-5 第11章 常用的VLSI系统部件 16 §11.7 D触发器 具有Load(装载)控制的CMOS DFF的操作

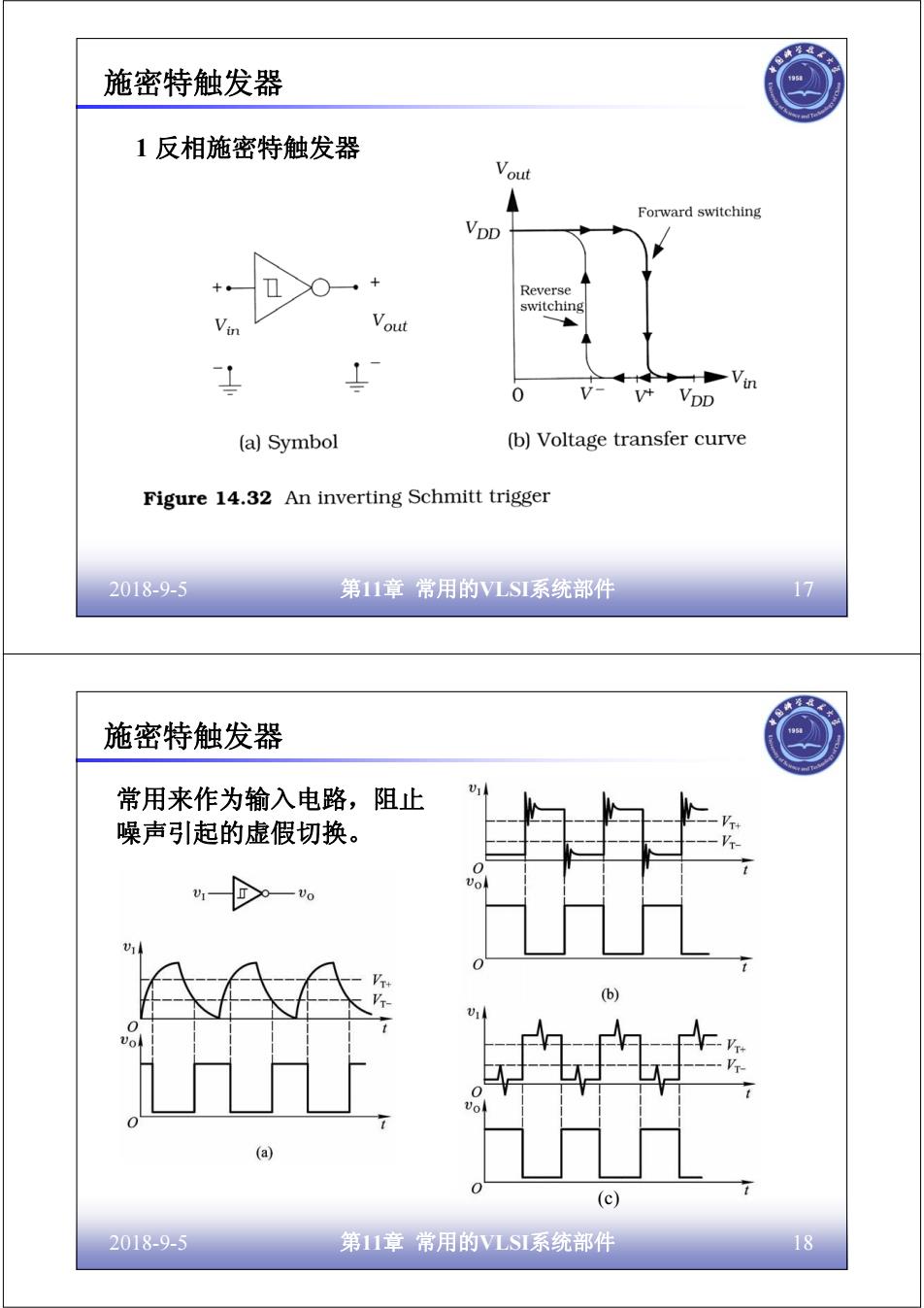

施密特触发器 1反相施密特触发器 Vout Forward switching VpD Reverse switching Vout Vin 0 V-v+VDD (a)Symbol (b)Voltage transfer curve Figure 14.32 An inverting Schmitt trigger 2018-9-5 第11章常用的VLSI系统部件 17 施密特触发器 常用来作为输入电路,阻止 噪声引起的虚假切换。 (b) (a) 0 (c) 2018-9-5 第11章常用的VLSI系统部件 18

2018-9-5 第11章 常用的VLSI系统部件 17 施密特触发器 1 反相施密特触发器 2018-9-5 第11章 常用的VLSI系统部件 18 (c) 施密特触发器 常用来作为输入电路,阻止 噪声引起的虚假切换

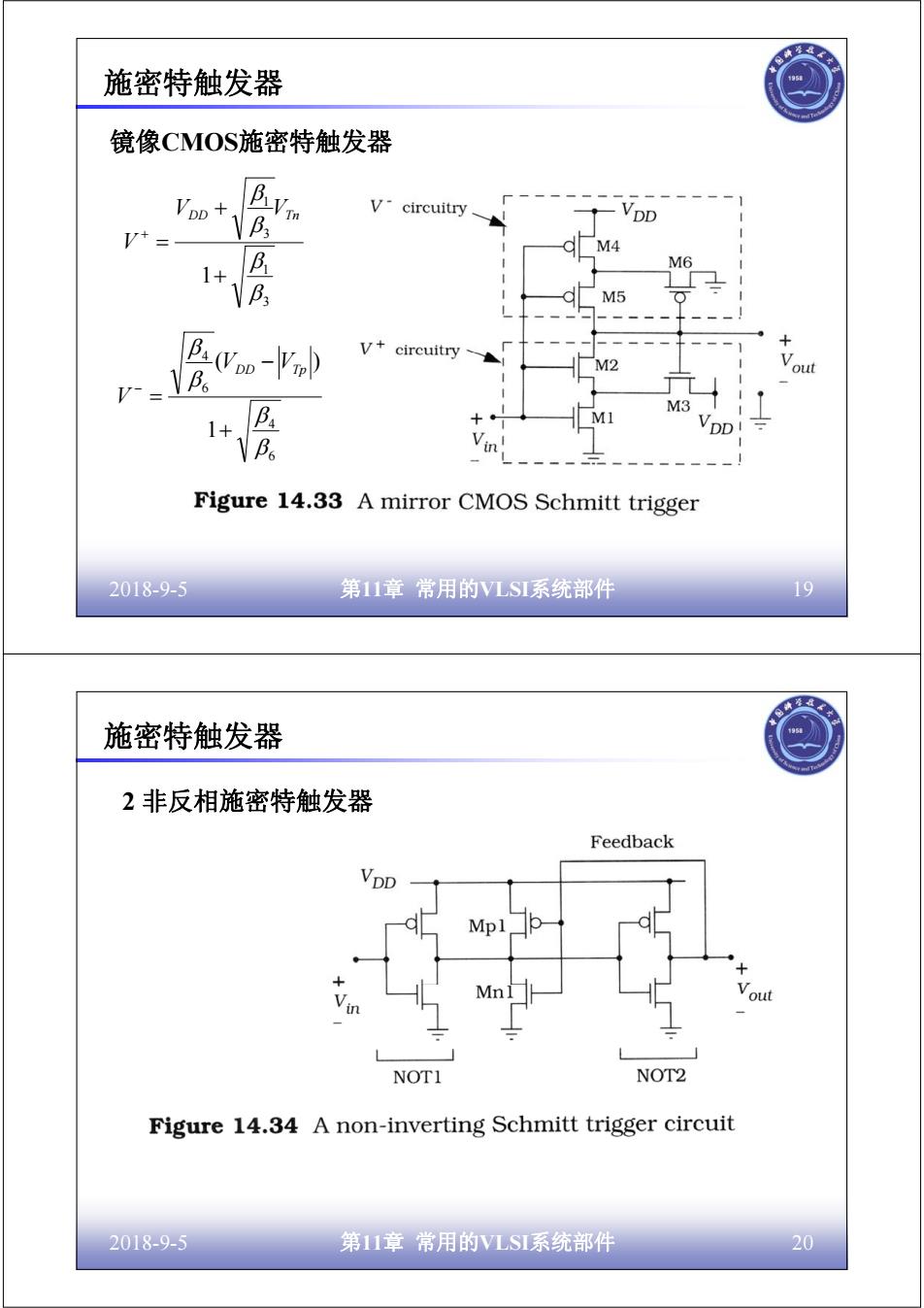

施密特触发器 镜像CMOS施密特触发器 V circuitry V+ 1+ M5 B(V ,-a V+ circuitry v-=V out B. M3 1+ DD VB。 Figure 14.33 A mirror CMOS Schmitt trigger 2018-9-5 第11章常用的VLSI系统部件 19 施密特触发器 2非反相施密特触发器 Feedback VpD Mpl_ V Mnl out n NOT1 NOT2 Figure 14.34 A non-inverting Schmitt trigger circuit 2018-9-5 第11章常用的VLSI系统部件 20

2018-9-5 第11章 常用的VLSI系统部件 19 3 1 3 1 1 β β β β + + =+ VDD VTn V 6 4 6 4 1 ( ) β β β β + − =− VDD VTp V 镜像CMOS施密特触发器 施密特触发器 2018-9-5 第11章 常用的VLSI系统部件 20 2 非反相施密特触发器 施密特触发器