中国绅学我术大学 University of Science and Technology of China 第8章高速CMOS逻辑电路设计 本章目录 >8.1门延时 >8.2驱动大电容负载 >8.3逻辑努力(Logical Effort) >8.4 BiCMOS驱动器 2018-9-5 第8章高速CMOS逻辑电路设计 §8.1门延时 CMOS逻辑门的开关时间 tr=tLH VDD C Gate 与=tH tro Vout o Gnd CL 0 Figure 8.1 Output switching times 上升时间:t,=to+0C2 下降时间:tr=to+anCL 2018-9-5 第8章高速CMOS逻辑电路设计 2

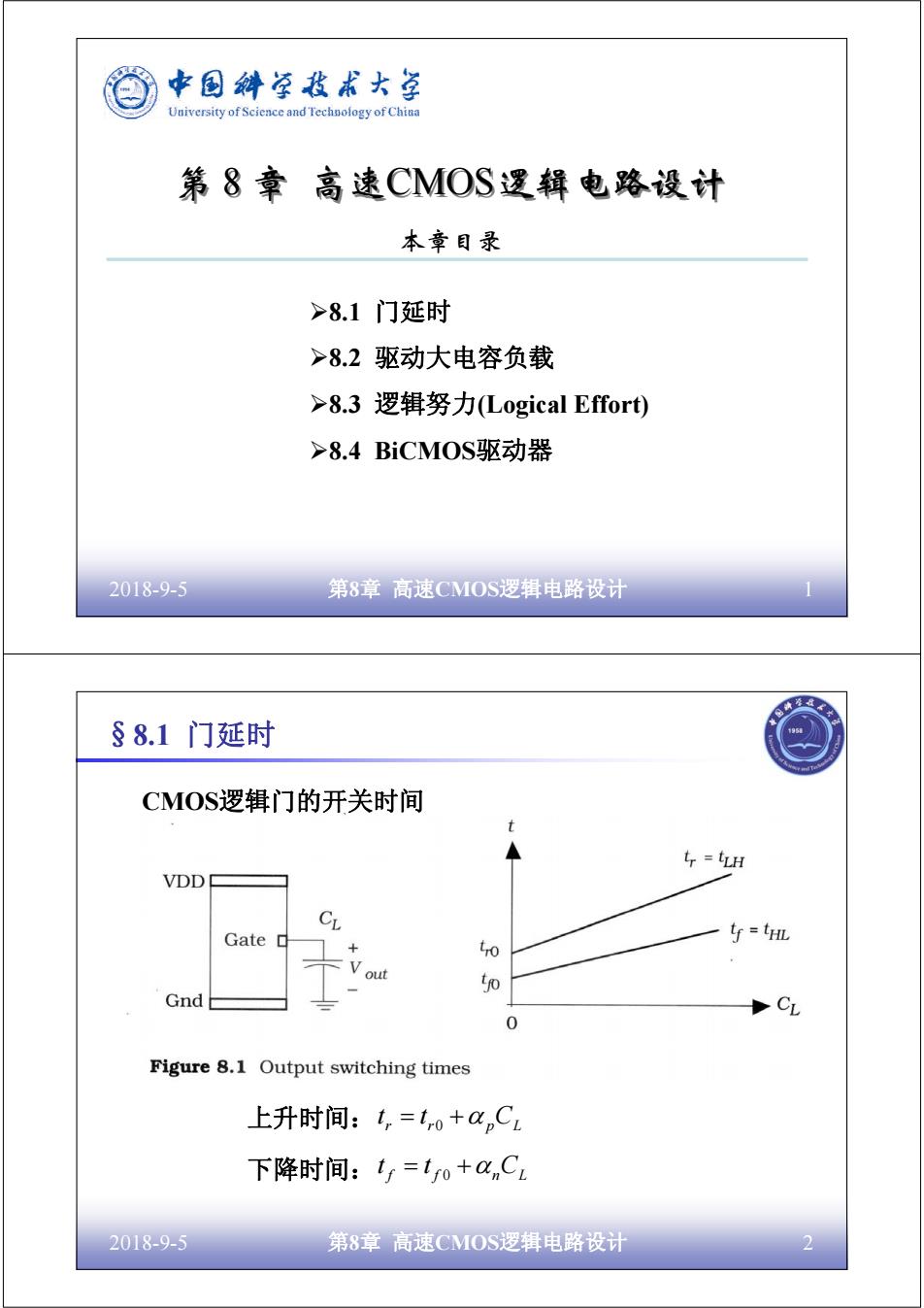

2018-9-5 第8章 高速CMOS逻辑电路设计 1 第 8 章 高速 CMOS逻辑电路设计 本章目录 ¾8.1 门延时 ¾8.2 驱动大电容负载 ¾8.3 逻辑努力(Logical Effort) ¾8.4 BiCMOS驱动器 2018-9-5 第8章 高速CMOS逻辑电路设计 2 §8.1 门延时 CMOS逻辑门的开关时间 r r pCL t = t 0 +α f f nCL t = t 0 +α 上升时间: 下降时间:

§8.1门延时 1参照晶体管 喝L4 Wmin W=3Wmin (a)Minimum-size (b)3X scaled FET Figure 8.2 Unit transistor reference 最小尺寸的MOSFET 1 CGu=Co (WL) R Cpu=(CGD+CpB)u (Vpp-V) Csu=(CGs+CsB)u 2018-9-5 第8章高速CMOS逻辑电路设计 §8.1门延时 L W=3Wmin (a)Minimum-size (b)3X scaled FET Figure 8.2 Unit transistor reference 放大m倍的MOSFET R R= m Ccm=mCGm,Com≈mCu,Csn≈mCsm RnCm=R,Cn=常数 2018-9-5 第8章高速CMOS逻辑电路设计

2018-9-5 第8章 高速CMOS逻辑电路设计 3 §8.1 门延时 1 参照晶体管 ( ) 1 ' DD T u u V V L W k R ⎟ − ⎠ ⎞ ⎜ ⎝ ⎛ = Su GS SB u Du GD DB u Gu ox u C C C C C C C C WL ( ) ( ) ( ) = + = + = 最小尺寸的MOSFET 2018-9-5 第8章 高速CMOS逻辑电路设计 4 §8.1 门延时 m L u W m L W ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ ⎟ = ⎠ ⎞ ⎜ ⎝ ⎛ 放大m倍的MOSFET m R R u m = CGm = mCGu CDm ≈ mCDu CSm ≈ mCSu , , RmCm = RuCu = 常数

§8.1门延时 2反相器 DD ●最小尺寸的反相器 上升时间:trw=tro+puCL 下降时间:t=tfo+amCL 中点电压: h,-'o-+ 1+vr Gnd (a)Unit Inverter 输入电容:Cm=2Cu=Cmin 2018-9-5 第8章高速CMOS逻辑电路设计 §8.1门延时 放大3倍:m=3 VDD 上升时间:t,3=tro+ 3 下降时间:tr3=to+ 3 中点电压不变: VM= DD-Vm+FVm Gnd 1+vr (b)m=3 输入电容: Ci=3Cmin 2018-9-5 第8章高速CMOS逻辑电路设计 6

2018-9-5 第8章 高速CMOS逻辑电路设计 5 §8.1 门延时 2 反相器 z最小尺寸的反相器 ru r puCL t = t 0 +α fu f nuCL t = t 0 +α 上升时间: 下降时间: r V V rV V DD Tp Tn M + − + = 1 中点电压: min 输入电容:Cin = 2Cu = C 2018-9-5 第8章 高速CMOS逻辑电路设计 6 §8.1 门延时 放大3倍:m=3 L pu tr tr C 3 3 0 α = + L nu t f t f C 3 3 0 α = + 上升时间: 下降时间: r V V rV V DD Tp Tn M + − + = 1 中点电压不变: 输入电容: Cin = 3Cmin

§8.1门延时 3与非门 VDD 最小尺寸的NAND2 3 上升时间:4=2w+aC 下降时间:tr=3tro+2 CL 输入电容:Cm=Cmim Gnd (a)Unit transistors 2018-9-5 第8章高速CMOS逻辑电路设计 §8.1门延时 放大3倍:m=3 VDD 3 上升时间:t,=一t,o+ 2 3 ■■ 2 下降时间:ty=3tro+2auCL 输入电容:Cn=3Cmin N输入放大m倍尺寸的与非门 上升时间:(=V+。+ 2 Iro+- m Gnd (b)m=3 circuit 下降时间:t,NON+l),NouC 2 -tro+ m 输入电容:Cm=mCmn 2018-9-5 第8章高速CMOS逻辑电路设计 8

2018-9-5 第8章 高速CMOS逻辑电路设计 7 §8.1 门延时 3 与非门 最小尺寸的NAND2 r r puCL t = t 0 +α 2 3 f f nuCL t = 3t 0 + 2α 上升时间: 下降时间: 输入电容: Cin = Cmin 2018-9-5 第8章 高速CMOS逻辑电路设计 8 §8.1 门延时 放大3倍:m=3 L pu tr tr C 2 3 3 0 α = + f f nuCL t t α 3 2 = 3 0 + 上升时间: 下降时间: 输入电容:Cin = 3Cmin N输入放大m倍尺寸的与非门 L pu r r C m t N t α + + = 0 2 1 L nu f f C m N t N N t α + + = 0 2 ( 1) 上升时间: 下降时间: 输入电容:Cin = mCmin

§8.1门延时 4或非门 VDD 最小尺寸的NOR2 上升时间:t,=3t,+2amC 下降时间:ty= 3 输入电容: Cn=Cmin Gnd (a)Unit transistors 2018-9-5 第8章高速CMOS逻辑电路设计 §8.1门延时 放大3倍:m=3 VDD 上升时间:t,=3t,o+ ■■ 下降时间: t=+ 2 3 输入电容:( Cn =3Cmin N输入放大m倍尺寸的或非门 上升时间:(=NW+ tro+- Na puCL 2 m Gnd W+1 下降时间:t,= (b)m=3 circuit m 输入电容:Cn=mCmn 2018-9-5 第8章高速CMOS逻辑电路设计 10

2018-9-5 第8章 高速CMOS逻辑电路设计 9 §8.1 门延时 4 或非门 最小尺寸的NOR2 r r puCL t = 3t 0 + 2α f f nuCL t = t 0 +α 2 3 上升时间: 下降时间: 输入电容: Cin = Cmin 2018-9-5 第8章 高速CMOS逻辑电路设计 10 §8.1 门延时 放大3倍:m=3 L pu tr tr C 3 2 3 0 α = + L nu t f t f C 2 3 3 0 α = + 上升时间: 下降时间: 输入电容:Cin = 3Cmin N输入放大m倍尺寸的或非门 L pu r r C m N t N N t α + + = 0 2 ( 1) L nu f f C m t N t α + + = 0 2 1 上升时间: 下降时间: 输入电容:Cin = mCmin

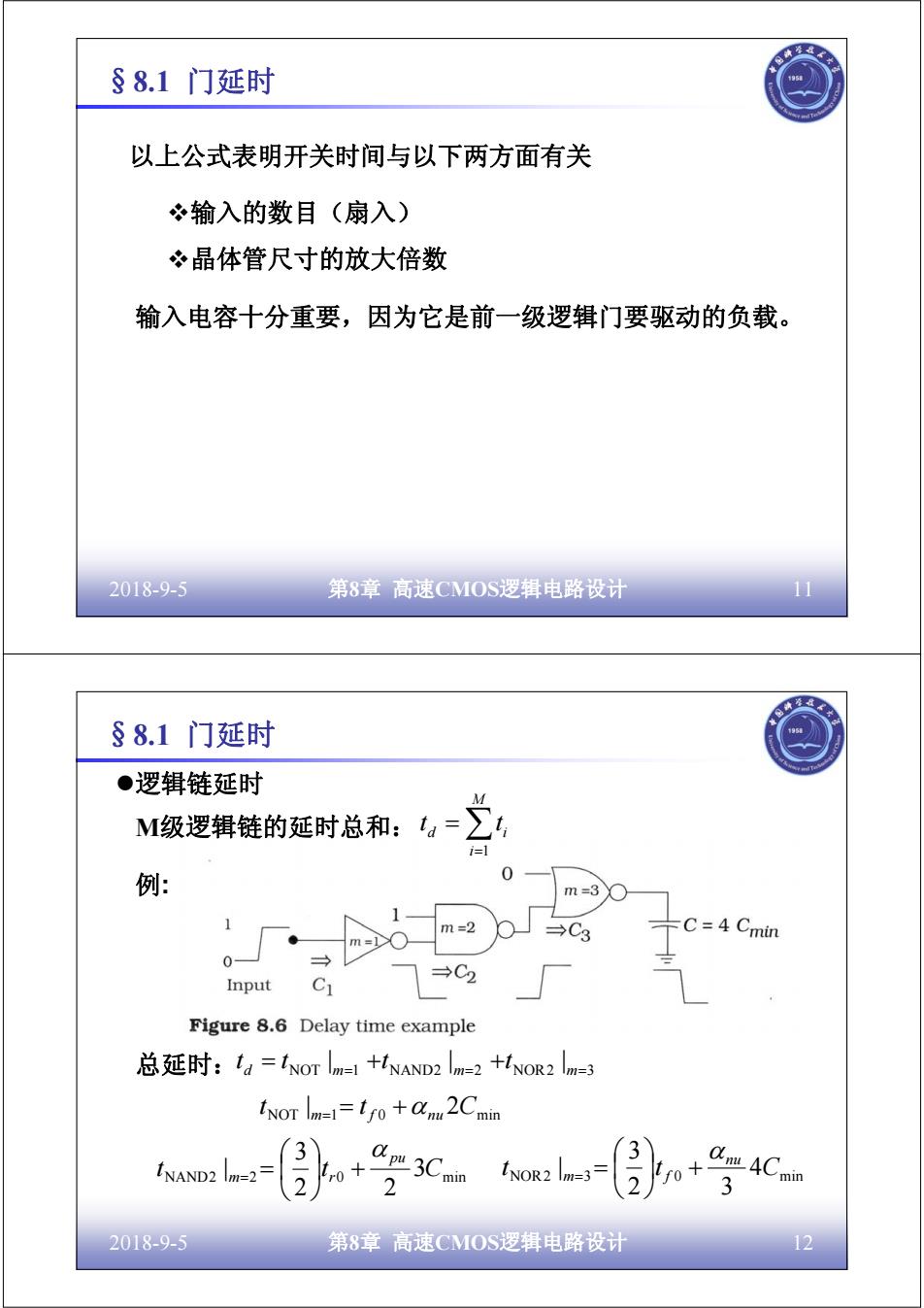

§8.1门延时 以上公式表明开关时间与以下两方面有关 输入的数目(扇入) 晶体管尺寸的放大倍数 输入电容十分重要,因为它是前一级逻辑门要驱动的负载。 2018-9-5 第8章高速CMOS逻辑电路设计 §8.1门延时 ●逻辑链延时 M级逻辑链的延时总和:ta= 例: 0 m=3○ m=2 m=10 →C3 C=4 Cmin 0 → Input C1 →C2 Figure 8.6 Delay time example 总延时:ta=orlm1+NAND2lm=2+OR2m3 INOT fo+mu2Cmin 3 INAND2 m=2 2 ,oR2lm3= 3 2018-9-5 第8章高速CMOS逻辑电路设计 12

2018-9-5 第8章 高速CMOS逻辑电路设计 11 §8.1 门延时 以上公式表明开关时间与以下两方面有关 输入的数目(扇入) 晶体管尺寸的放大倍数 输入电容十分重要,因为它是前一级逻辑门要驱动的负载。 2018-9-5 第8章 高速CMOS逻辑电路设计 12 §8.1 门延时 NOT 1 NAND2 2 NOR2 3 | | | d = m= + m= + m= t t t t NOT 1 0 2 min t | m= = t f +α nu C NAND2 2 0 min 3 2 2 3 t | t C pu m r α ⎟ + ⎠ ⎞ ⎜ ⎝ ⎛ = = NOR2 3 0 4 min 2 3 3 t | t C nu m f α ⎟ + ⎠ ⎞ ⎜ ⎝ ⎛ = = 总延时: z逻辑链延时 M级逻辑链的延时总和: ∑= = M i d i t t 1 例:

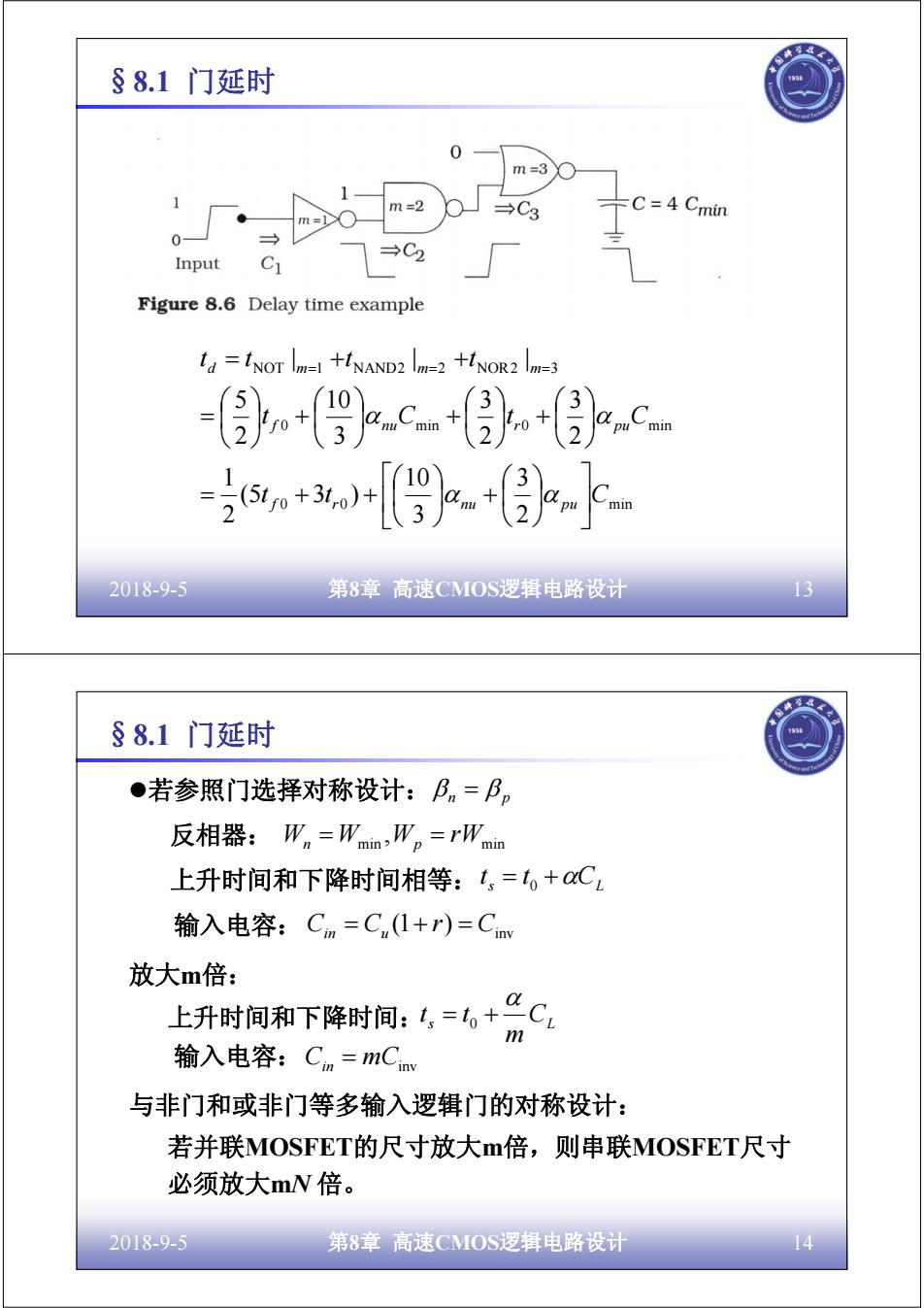

§8.1门延时 0 m=3X○ m-1 m=2 →C3 -C=4 Cmin Input Cl →C2 Figure 8.6 Delay time example Id =INOT Im=1 +INAND2 Im=2 +INOR2 Im=3 (n.c+}+}c =6w+[g+ 2018-9-5 第8章高速CMOS逻辑电路设计 13 §8.1门延时 ●若参照门选择对称设计:阝n=B。 反相器:Wn=Wmn,W。=rWin 上升时间和下降时间相等:t,=,+aC 输入电容:Cm=C(I+r)=Cnv 放大m倍: 上升时间和下降时间:1,=+CC, 输入电容:Cn=nCa 与非门和或非门等多输入逻辑门的对称设计: 若并联MOSFET的尺寸放大m倍,则串联MOSFET尺寸 必须放大mN倍。 2018-9-5 第8章高速CMOS逻辑电路设计 14

2018-9-5 第8章 高速CMOS逻辑电路设计 13 §8.1 门延时 0 0 min 0 min 0 min NOT 1 NAND2 2 NOR2 3 2 3 3 10 (5 3 ) 2 1 2 3 2 3 3 10 2 5 | | | t t C t C t C t t t t f r nu pu f nu r pu d m m m ⎥ ⎦ ⎤ ⎢ ⎣ ⎡ ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ ⎟ + ⎠ ⎞ ⎜ ⎝ ⎛ = + + ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ ⎟ + ⎠ ⎞ ⎜ ⎝ ⎛ ⎟ + ⎠ ⎞ ⎜ ⎝ ⎛ ⎟ + ⎠ ⎞ ⎜ ⎝ ⎛ = = = + = + = α α α α 2018-9-5 第8章 高速CMOS逻辑电路设计 14 §8.1 门延时 z若参照门选择对称设计:β n = β p min min 反相器: Wn =W ,Wp = rW 上升时间和下降时间相等: s CL t = t0 +α inv 输入电容: Cin = Cu (1+ r) = C 放大m倍: s CL m t t α = 0 + Cin = mCinv 上升时间和下降时间: 输入电容: 与非门和或非门等多输入逻辑门的对称设计: 若并联MOSFET的尺寸放大m倍,则串联MOSFET尺寸 必须放大mN 倍

§8.1门延时 ●实验法估计逻辑链的延时 N=1时:t4=(A+Bn)rmn Imin =RminCmin n= N=4 min N=3 A,B,tmin:实验中测定 N=2 W>1时: N=1 tdN =x(A+Bn)Tmin CL 0 若从N=1到N=2每个输入引起的 延时增加17%,意味着:x1=1.17 2018-9-5 第8章高速CMOS逻辑电路设计 15 §8.1门延时 ●实验法估计逻辑链的延时 N>1时: taN=x(4+Bn)tmin N=4 N=3 尺寸放大m倍: N=2 B ta.N =x(A+n)tmin m N=1 复杂N输入逻辑门: CL 0 B taw=(A+n)tmin m x2>1 2018-9-5 第8章高速CMOS逻辑电路设计 16

2018-9-5 第8章 高速CMOS逻辑电路设计 15 §8.1 门延时 min t (A Bn)τ d = + min 1 , 1 t x (A Bn)τ N d N = + − z实验法估计逻辑链的延时 N=1时: min = RminCmin τ A, B,τ min:实验中测定 Cmin C n L = N>1时: 若从N=1到N=2每个输入引起的 延时增加17%,意味着:x1=1.17 2018-9-5 第8章 高速CMOS逻辑电路设计 16 §8.1 门延时 min 1 , 1 ( n)τ m B t x A m N d N = + − min 1 , 2 1 ( n)τ m B t x x A m N d N = + − z实验法估计逻辑链的延时 尺寸放大m倍: min 1 , 1 t x (A Bn)τ N d N = + − N>1时: 复杂N输入逻辑门: 1 x2 >

§8.1门延时 m=3○ m=1 m=2 →C3 C=4 Cmin →C2 Input C Figure 8.6 Delay time example 例8.1:orlm=(A+Bx2)rnt 如果x=1.17 4=3.34A+5.3B Imin 2018-9-5 第8章高速CMOS逻辑电路设计 17 §8.2驱动大电容负载 对称设计:Bn=B。=B VpD - External load r=4= 2>1 out 设Vm=Pn=, in Rn=R。=R= B(VDD-VI) ts to +acL acR= B(VDD-VI) 输入电容:Cm=CGm+CGp=Cax(An+An) =CoL(W,+Wp)=(1+r)CoLW,=(1+r)Con 2018-9-5 第8章高速CMOS逻辑电路设计 18

2018-9-5 第8章 高速CMOS逻辑电路设计 17 §8.1 门延时 x A x B td ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ = + + + 2 6 17 (2 1) 1 1 min τ NOT 1 min | = ( + ×2)τ t m= A B NAND2 2 1 3 min 2 | ⎟τ ⎠ ⎞ ⎜ ⎝ ⎛ = = + × B t m x A NOR2 3 1 4 min 3 | ⎟τ ⎠ ⎞ ⎜ ⎝ ⎛ = = + × B t m x A 例8.1: A B td 3.34 5.3 min = + τ 1.17 如果x1 = 2018-9-5 第8章 高速CMOS逻辑电路设计 18 §8.2 驱动大电容负载 p L n W r L W ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ ⎟ = ⎠ ⎞ ⎜ ⎝ ⎛ 1 ' ' = = > p n p n k k r μ μ ( ) 1 DD T n p V V R R R − = = = β VTn = VTp =VT β n = β p = β s CL t = t0 +α ( ) 1 VDD VT R − ∝ = β α ox n p ox n Gn in Gn Gp ox Gn Gp C L W W r C LW r C C C C C A A ( ) (1 ) (1 ) ( ) = + = + = + = + = + 对称设计: 设 输入电容:

§8.2驱动大电容负载 在反相器链中使延时最小: Reference … B2 B3 Figure 8.11 Inverter chain analysis 选择第一级反相器作为参照门: 输入电容:C,=C FET电阻:R=R 参照时间常数:t,=RC 2018-9-5 第8章高速CMOS逻辑电路设计 19 §8.2驱动大电容负载 在反相器链中使延时最小: Reference B2 B3 Figure 8.11 Inverter chain analysis 设计步骤: 级数:N=h C 总的时间常数:ta=NSt, 2018-9-5 第8章高速CMOS逻辑电路设计 20

2018-9-5 第8章 高速CMOS逻辑电路设计 19 §8.2 驱动大电容负载 参照时间常数: r = R1C1 τ 选择第一级反相器作为参照门: 输入电容:Ci = C1 FET电阻:Ri = R1 在反相器链中使延时最小: 2018-9-5 第8章 高速CMOS逻辑电路设计 20 §8.2 驱动大电容负载 N L C C S 1 1 ⎟ ⎟ ⎠ ⎞ ⎜ ⎜ ⎝ ⎛ 放大因子: = 1 ln C C N L 级数: = d NS r 总的时间常数:τ = τ 在反相器链中使延时最小: 设计步骤: