中国绅学我术大学 University of Science and Technology of China 第7章CMOS逻辑门电子学分桥 本章目录 7.1CMOS反相器的直流特性 7.2反相器的开关特性 7.3功耗 7.4DC特性:与非门和或非门 7.5与非门和或非门的暂态响应 7.6复合逻辑门的分析 7.7逻辑门过渡特性设计 7.8传输门和传输管 7.9关于SPICE模拟 2018-9-5 第7章CMOS逻辑门电子学分析 §7.1CMOS反相器的直流特性 1逻辑摆幅V, VSGp=VDD VDD VpD On Vin =0 off Vout =VDD On Vin =VDD Vout=0 (a)Low input voltage (b)High input voltage Figure 7.2 VoH and VoL for the inverter circuit 输出高电压:VoH,max=Vop输出低电压:'oL,min=0V 逻辑摆幅:'=VoH,max一VoL,min=Vop 逻辑摆幅等于全部电源电压值,称为全轨输出。 全轨输出:full-rail output或rail to rail output 2018-9-5 第7章CMOS逻辑门电子学分析 2

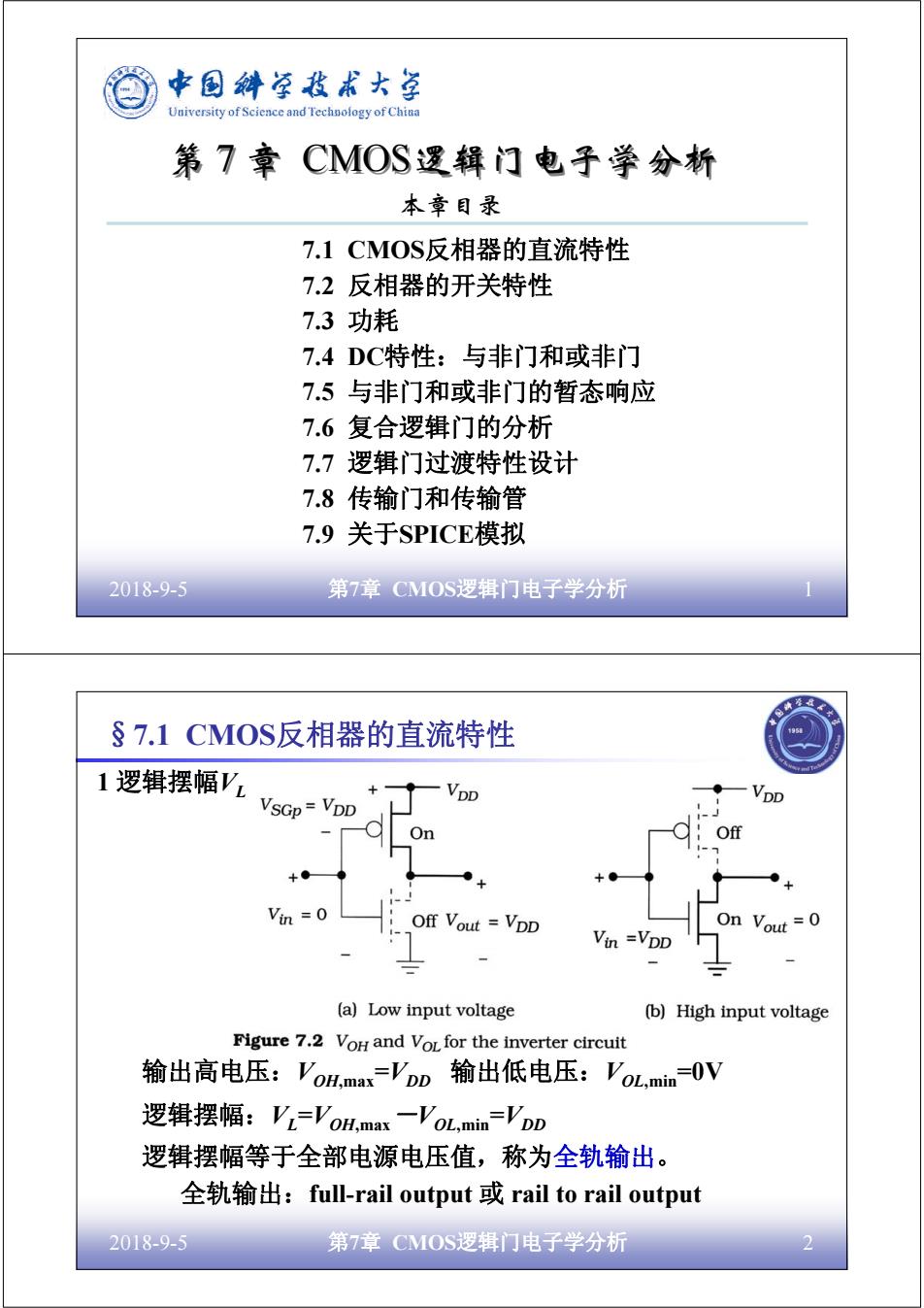

2018-9-5 第7章 CMOS逻辑门电子学分析 1 第 7 章 CMOS逻辑门电子学分析 逻辑门电子学分析 本章目录 7.1 CMOS反相器的直流特性 7.2 反相器的开关特性 7.3 功耗 7.4 DC特性:与非门和或非门 7.5 与非门和或非门的暂态响应 7.6 复合逻辑门的分析 7.7 逻辑门过渡特性设计 7.8 传输门和传输管 7.9 关于SPICE模拟 2018-9-5 第7章 CMOS逻辑门电子学分析 2 §7.1 CMOS反相器的直流特性 1 逻辑摆幅VL 输出高电压:VOH,max=VDD 输出低电压:VOL,min=0V 逻辑摆幅:VL=VOH,max-VOL,min=VDD 逻辑摆幅等于全部电源电压值,称为全轨输出。 全轨输出:full-rail output 或 rail to rail output

§7.1CMOS反相器的直流特性 2电压传输特性曲线(VTC) Vout Mp on Mn off VDD VOH=V DD 日 VsGp + Vout=V in Mp VM +● ●十 Mn on Mp off Mn Vout VGSn VoH=0寸 Vin '00o 1"VDD L VIH Figure 7.3 Voltage transfer curve for the NOT gate 2018-9-5 第7章CMOS逻辑门电子学分析 §7.1CMOS反相器的直流特性 2电压传输特性曲线(VTC) 可分为5个区域 A区,0≤Vm<'n: Vout Mp on NMOS截止,PMOS导通; Mn off VOH=V DD B区,Vn<Vn<'om-Vp: Vout=V in NMOS饱和,PMOS非饱和; VM C区,Voa-|n<Vn<'ou+Vn: Mn on NMOS饱和,PMOS饱和; 6 Mp off VOH=0 Vin D区,Vom+'n<Vn<'p-|'nf 'oL-00"o 1"VDD NMOS非饱和,PMOS饱和; VLL VIH E区,Voo-Vp<Vn≤Vo NMOS导通,PMOS截止。 2018-9-5 第7章CMOS逻辑门电子学分析

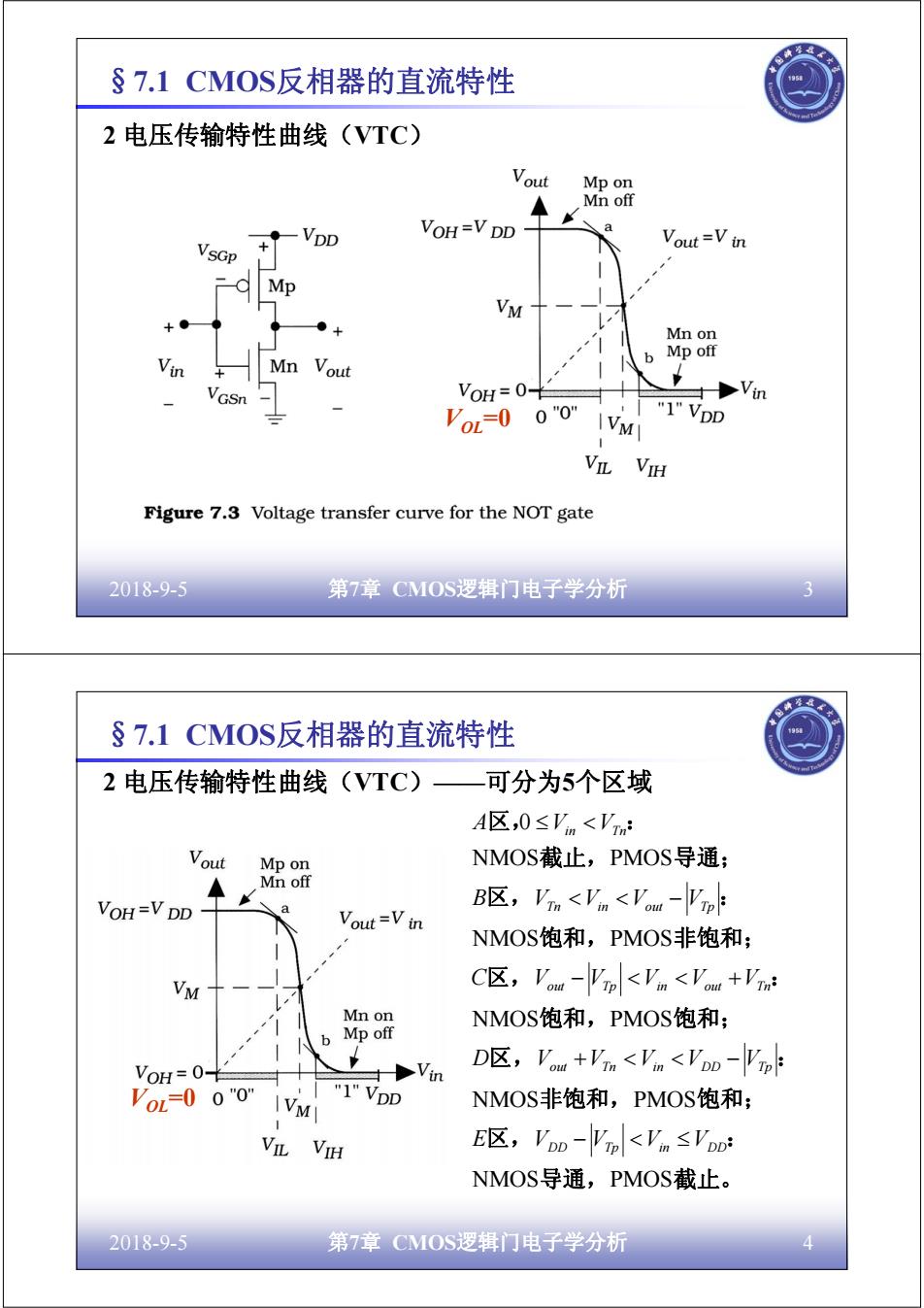

2018-9-5 第7章 CMOS逻辑门电子学分析 3 §7.1 CMOS反相器的直流特性 2 电压传输特性曲线(VTC) VOL=0 2018-9-5 第7章 CMOS逻辑门电子学分析 4 §7.1 CMOS反相器的直流特性 2 电压传输特性曲线(VTC)——可分为5个区域 VOL=0 导通, 截止。 区, : 非饱和, 饱和; 区, : 饱和, 饱和; 区, : 饱和, 非饱和; 区, : 截止, 导通; 区, : NMOS PMOS NMOS PMOS NMOS PMOS NMOS PMOS NMOS PMOS 0 DD Tp in DD out Tn in DD Tp out Tp in out Tn Tn in out Tp in Tn E V V V V D V V V V V C V V V V V B V V V V A V V − < ≤ + < < − − < < + < < − ≤ <

§7.1CMOS反相器的直流特性 2电压传输特性曲线(VTC) Vout (1)输入低电压和输入高电压 Mp on Mn off VOH=V DD 、a Vow=f(Vun) Vout=V in dy o=-1 VM d Mn on 逻辑0的输入电压范围: 6 Mp off VOH=0 Vin 0≤'m≤'Vu VoL=0 0"o" 1"VPD 逻辑1的输入电压范围: VLL VIH VH≤'m≤'oD 2018-9-5 第7章CMOS逻辑门电子学分析 §7.1CMOS反相器的直流特性 2电压传输特性曲线(VTC) a点坐标: R化-广-2cao--中kwm-)-e月 0+会--是。 dy dVin B。 b点坐标: B2g-L-E1,e。-r 能-1儿0+是=2+层w-.小 2018-9-5 第7章CMOS逻辑门电子学分析 6

2018-9-5 第7章 CMOS逻辑门电子学分析 5 §7.1 CMOS反相器的直流特性 2 电压传输特性曲线(VTC) VOL=0 (1)输入低电压和输入高电压 ( ) out Vin V = f 1 d d = − in out V V 令 逻辑0的输入电压范围: 0 ≤Vin ≤VIL 逻辑1的输入电压范围: VIH ≤Vin ≤VDD 2018-9-5 第7章 CMOS逻辑门电子学分析 6 §7.1 CMOS反相器的直流特性 2 电压传输特性曲线(VTC) a点坐标: b点坐标: [2( )( ) ( ) ] 2 1 ( ) 2 1 2 2 β n Vin −VTn = β p VDD −Vin − VTp VDD −Vout − VDD −Vout Tn p n out DD Tp p n in in out V V V V V V V β β β β = −1⇒ (1+ ) = 2 − − + d d 2 2 ( ) 2 1 [2( ) ] 2 1 β n Vin −VTn Vout −Vout = β p VDD −Vin − VTp 1 (1 ) 2 ( ) d d DD Tp n p out Tn n p in in out V V V V V V V = − ⇒ + = + + − β β β β

§7.1CMOS反相器的直流特性 2电压传输特性曲线(VTC) (2)噪声容限 Vout Mp on Mn off 高电平噪声容限: VOH=V DD 、a Vout=V in VNMH=VOH.min-VIH.min -- 低电平噪声容限: VM Mn on VNML=VIL.ma -VoL.ma 6 Mp off VOH=0 Vin (3) 中点电压VM 'o=00o 1"VDD 定义:VTC曲线与直线 VLL VIH Vou'n的交点 2018-9-5 第7章CMOS逻辑门电子学分析 §7.1CMOS反相器的直流特性 中点电压VM的计算: :Ipn=Ipp A-广=ww--小 VDD Vop-IVml+ :.VM= 1+ VM VB。 Figure 7.4 Inverter voltages for Vy calculation 2018-9-5 第7章CMOS逻辑门电子学分析 8

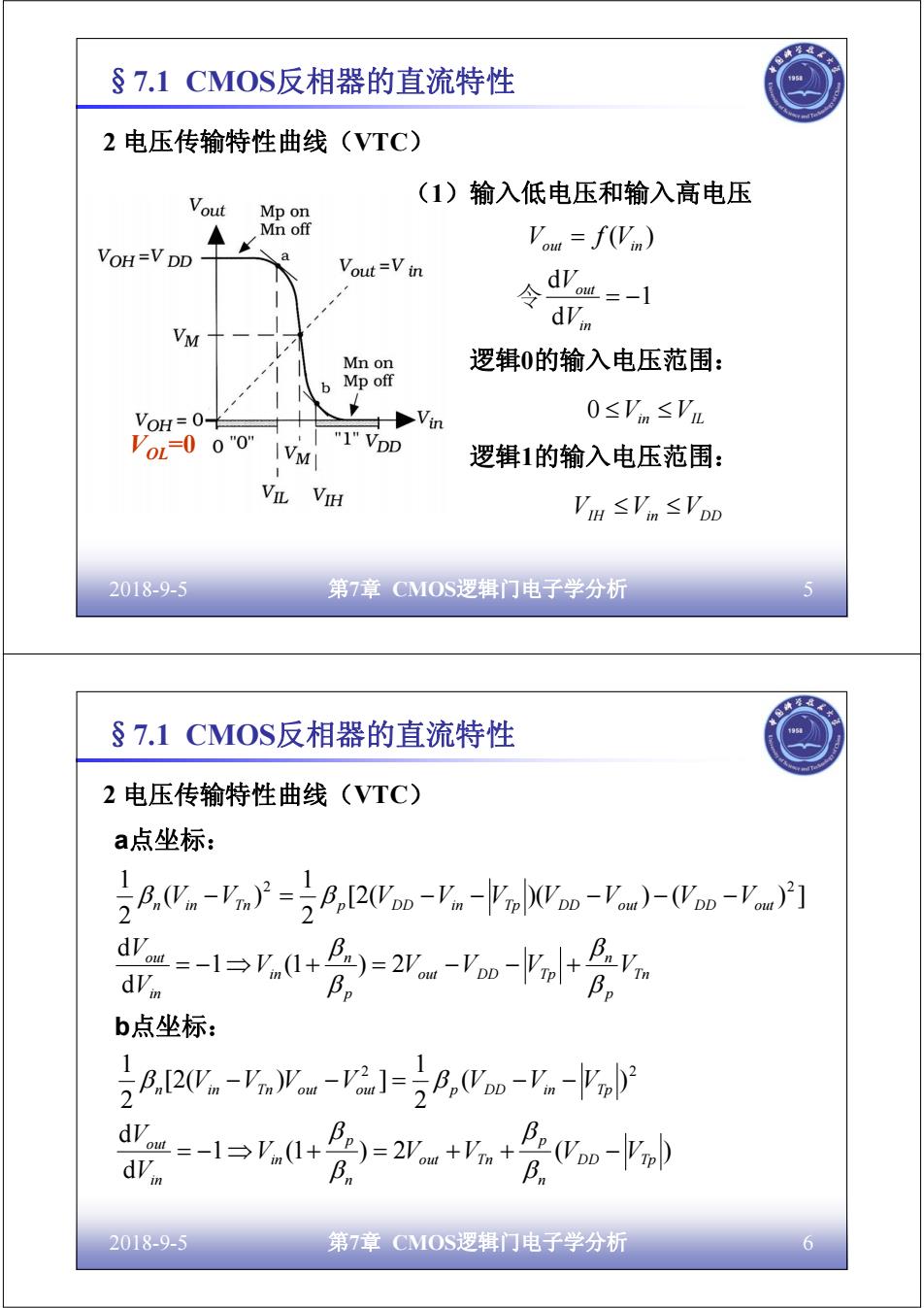

2018-9-5 第7章 CMOS逻辑门电子学分析 7 §7.1 CMOS反相器的直流特性 2 电压传输特性曲线(VTC) VOL=0 (2)噪声容限 高电平噪声容限: VNMH =VOH ,min −VIH ,min 低电平噪声容限: VNML =VIL,max −VOL,max (3)中点电压VM 定义:VTC曲线与直线 Vout=Vin的交点 2018-9-5 第7章 CMOS逻辑门电子学分析 8 §7.1 CMOS反相器的直流特性 Dn Dp QI = I 2 2 ( ) 2 1 ( ) 2 1 ∴ β n VM −VTn = β p VDD −VM − VTp p n Tn p n DD Tp M β β V β β V |V | V + − + ∴ = 1 中点电压VM 的计算:

§7.1CMOS反相器的直流特性 对称反相器:VM=一Voo VpD-IVidl+ B. Tn V= 2 1+ 若Vm=V则Bn=B。 2018-9-5 第7章CMOS逻辑门电子学分析 §7.1CMOS反相器的直流特性 例7.1一个CMOS工艺具有下列参数:电源电压Voo=3.0V kn=140AN2,'m=0.70V,k2=60A/V2,'p=-0.70V ①对称设计Bn=Pp VDD -IVTpl+ Tn VM= 3-0.7+1x0.7=l.5V 1+V1 1+ B. Bp 是-2 2018-9-5 第7章CMOS逻辑门电子学分析 10

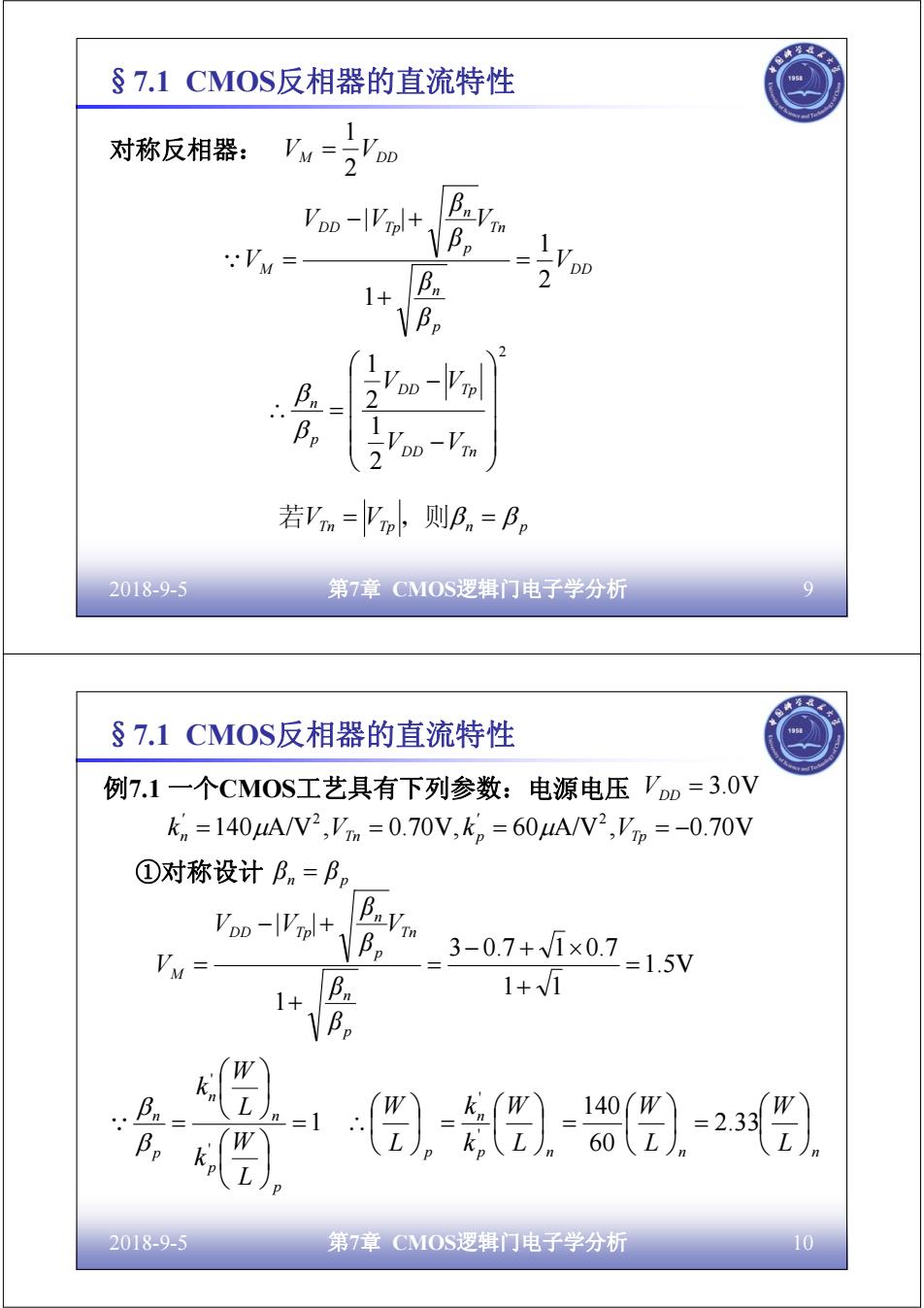

2018-9-5 第7章 CMOS逻辑门电子学分析 9 §7.1 CMOS反相器的直流特性 对称反相器: VM VDD 2 1 = DD p n Tn p n DD Tp M V β β V β β V |V | V 2 1 1 = + − + Q = 2 2 1 2 1 ⎟ ⎟ ⎟ ⎟ ⎠ ⎞ ⎜ ⎜ ⎜ ⎜ ⎝ ⎛ − − ∴ = DD Tn DD Tp p n V V V V β β 若VTn = VTp,则β n = β p 2018-9-5 第7章 CMOS逻辑门电子学分析 10 例7.1 一个CMOS工艺具有下列参数: 140 A/V , 0.70V, 60 A/V , 0.70V 2 2 = = = Tp = − ' Tn p ' kn μ V k μ V 电源电压 VDD = 3.0V ①对称设计 n p β = β 1.5V 1 1 3 0.7 1 0.7 1 = + − + × = + − + = p n Tn p n DD Tp M β β V β β V |V | V 1 ' ' = ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ = p p n n p n L W k L W k β β Q p n n n n p L W L W L W k k L W ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ ⎟ = ⎠ ⎞ ⎜ ⎝ ⎛ ⎟ = ⎠ ⎞ ⎜ ⎝ ⎛ ⎟ = ⎠ ⎞ ⎜ ⎝ ⎛ ∴ 2.33 60 140 ' ' §7.1 CMOS反相器的直流特性

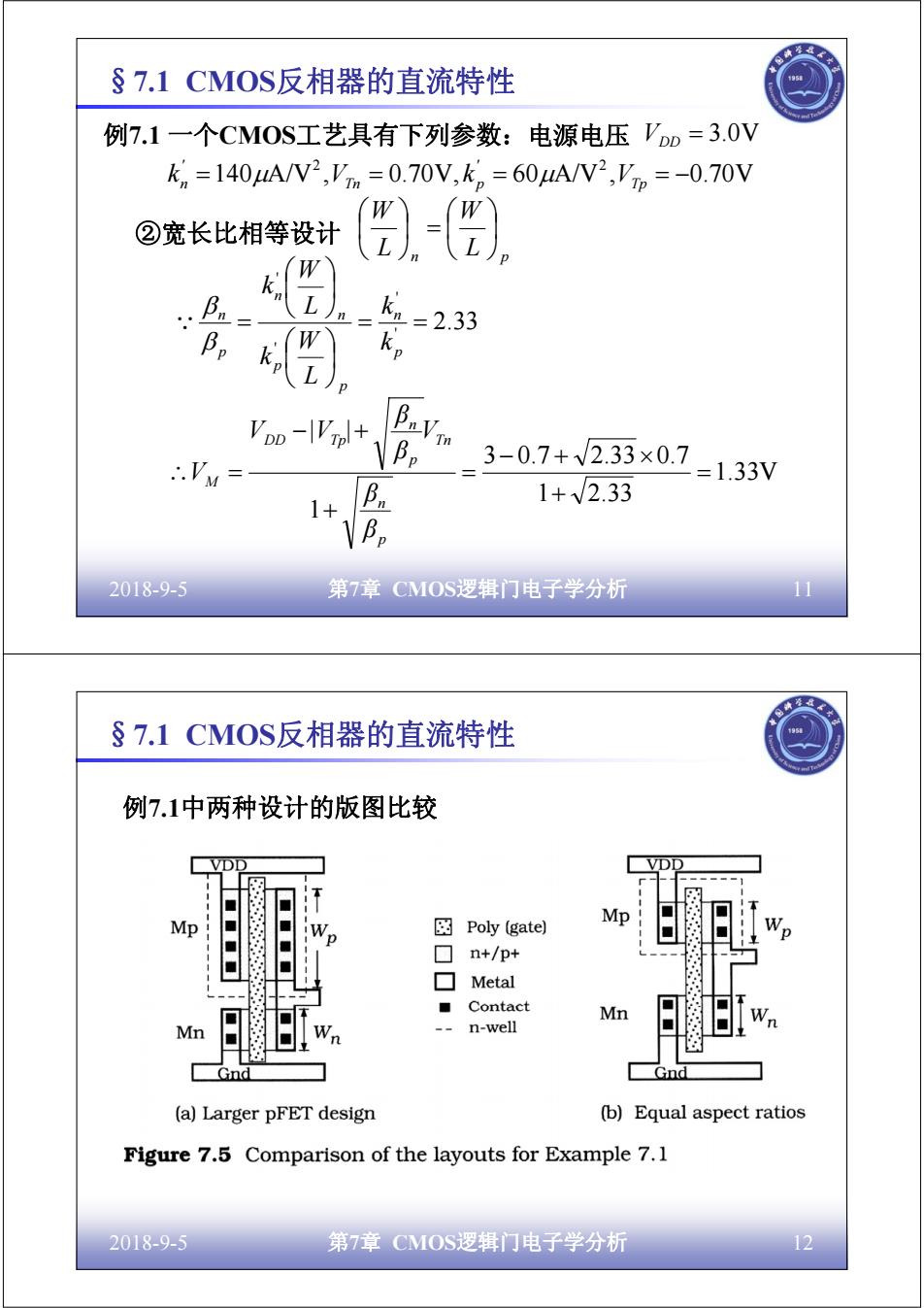

§7.1CMOS反相器的直流特性 例7.1一个CMOS工艺具有下列参数:电源电压'oo=3.0V k,=140AV2,'m=0.70V,k。=60AV2,'p=-0.70V ②宽长比相等设计 W B. L W K=2.33 kp L)P VDD-IVipl+ m :.Vx 3-0.7+√2.33×0.7 =1.33 1+√2.33 1+ E. 2018-9-5 第7章CMOS逻辑门电子学分析 §7.1CMOS反相器的直流特性 例7.1中两种设计的版图比较 VDD VDD Mp ☒ Poly (gate) Mp n+/p+ ■ 口 Metal ■ Contact Mn n-well Gnd Gnd (a)Larger pFET design (b)Equal aspect ratios Figure 7.5 Comparison of the layouts for Example 7.1 2018-9-5 第7章CMOS逻辑门电子学分析 12

2018-9-5 第7章 CMOS逻辑门电子学分析 11 ②宽长比相等设计 n L p W L W ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ ⎟ = ⎠ ⎞ ⎜ ⎝ ⎛ 2.33 ' ' ' ' = = ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ = p n p p n n p n k k L W k L W k β β Q 1.33V 1 2.33 3 0.7 2.33 0.7 1 = + − + × = + − + ∴ = p n Tn p n DD Tp M β β V β β V |V | V 例7.1 一个CMOS工艺具有下列参数: 140 A/V , 0.70V, 60 A/V , 0.70V 2 2 = = = Tp = − ' Tn p ' kn μ V k μ V 电源电压 VDD = 3.0V §7.1 CMOS反相器的直流特性 2018-9-5 第7章 CMOS逻辑门电子学分析 12 §7.1 CMOS反相器的直流特性 例7.1中两种设计的版图比较

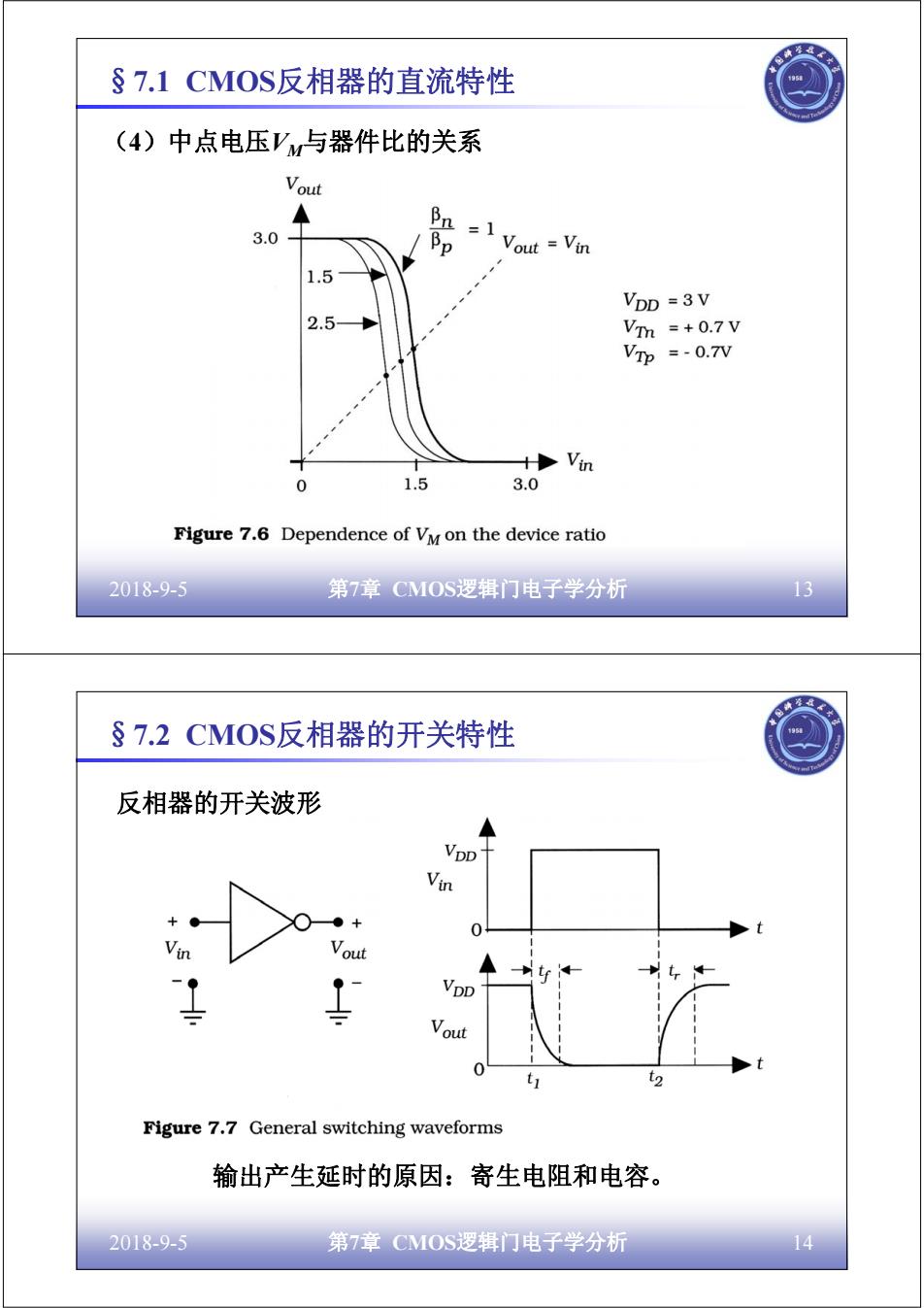

§7.1CMOS反相器的直流特性 (4)中点电压VM与器件比的关系 Vout 3.0 1 Vout Vin 1.5 VDD =3V 2.5 Vm=+0.7V Vp=-0.7V 十D Vin 0 1.5 3.0 Figure 7.6 Dependence of Vm on the device ratio 2018-9-5 第7章CMOS逻辑门电子学分析 3 §7.2CMOS反相器的开关特性 反相器的开关波形 VpD Vin 一●+ 0 Vout 其 VpD Vout t2 Figure 7.7 General switching waveforms 输出产生延时的原因:寄生电阻和电容。 2018-9-5 第7章CMOS逻辑门电子学分析 14

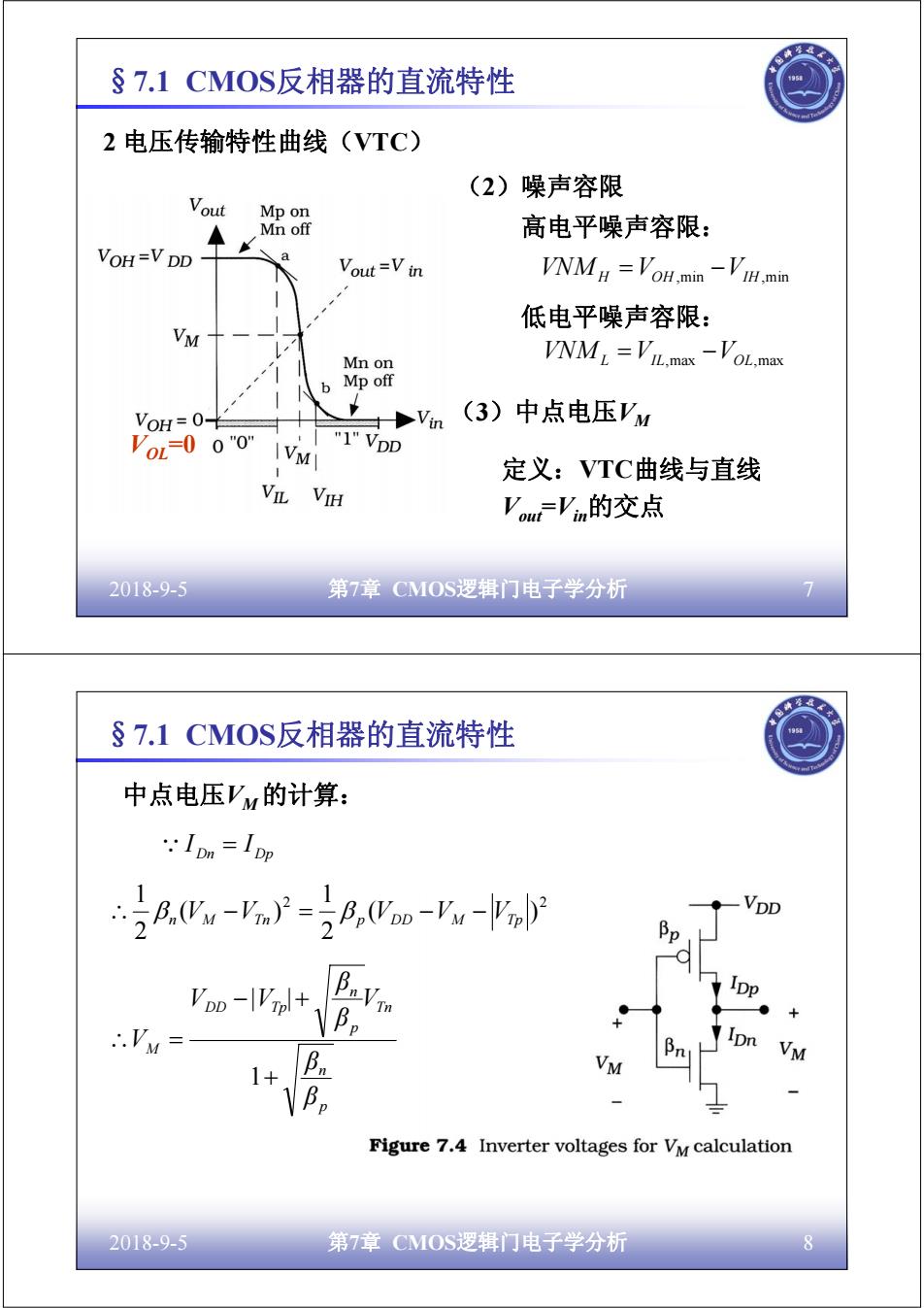

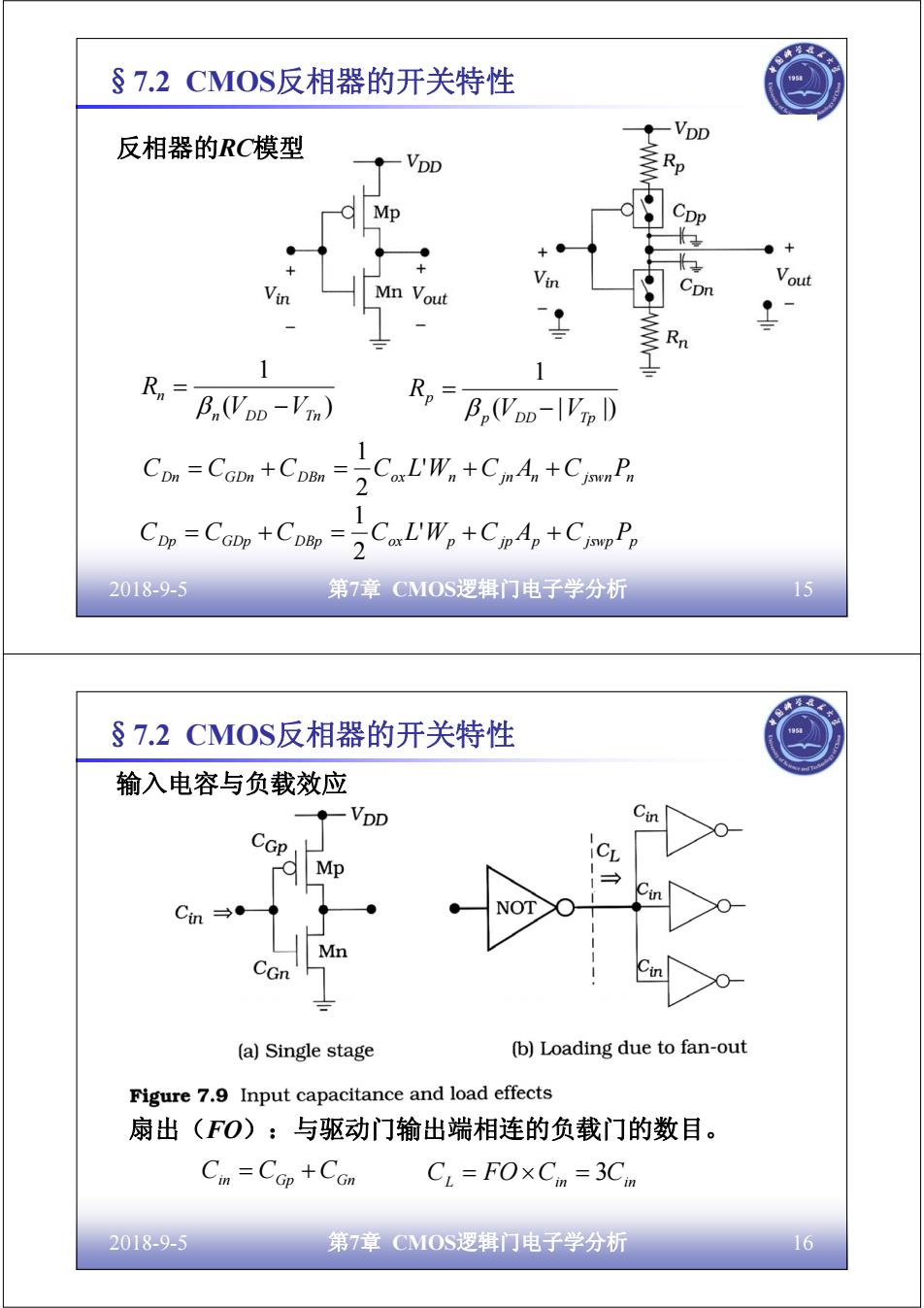

2018-9-5 第7章 CMOS逻辑门电子学分析 13 §7.1 CMOS反相器的直流特性 (4)中点电压VM与器件比的关系 2018-9-5 第7章 CMOS逻辑门电子学分析 14 §7.2 CMOS反相器的开关特性 反相器的开关波形 输出产生延时的原因:寄生电阻和电容

§7.2CMOS反相器的开关特性 反相器的RC模型 VDD VDD Mp Cpp 术2 + Mn Vout Cpn Vout R。=B.nWo-V) Rp=- Bp(VDD-IVI D Cpa=CGDn+CpBn=CoL'Wn+CmAn+Chwn Pu 2 1 CDp CGDp+CDp=CoL'Wp+CpAp+Cjap Pp 2018-9-5 第7章CMOS逻辑门电子学分析 §7.2CMOS反相器的开关特性 输入电容与负载效应 VDD CGp CL Mp in Cin →● Mn CGn in (a)Single stage (b)Loading due to fan-out Figure 7.9 Input capacitance and load effects 扇出(FO):与驱动门输出端相连的负载门的数目。 Cm=CGp+CGn CL=FO×Cm=3Cm 2018-9-5 第7章CMOS逻辑门电子学分析 16

2018-9-5 第7章 CMOS逻辑门电子学分析 15 a §7.2 CMOS反相器的开关特性 ( ) 1 n DD Tn n V V R − = β ( | |) 1 p DD Tp p V V R − = β 反相器的RC模型 CDn = CGDn +CDBn = CoxL Wn +CjnAn +CjswnPn ' 2 1 CDp = CGDp +CDBp = CoxL Wp +Cjp Ap +CjswpPp ' 2 1 2018-9-5 第7章 CMOS逻辑门电子学分析 16 §7.2 CMOS反相器的开关特性 输入电容与负载效应 Cin = CGp +CGn CL FO Cin Cin = × = 3 扇出(FO):与驱动门输出端相连的负载门的数目

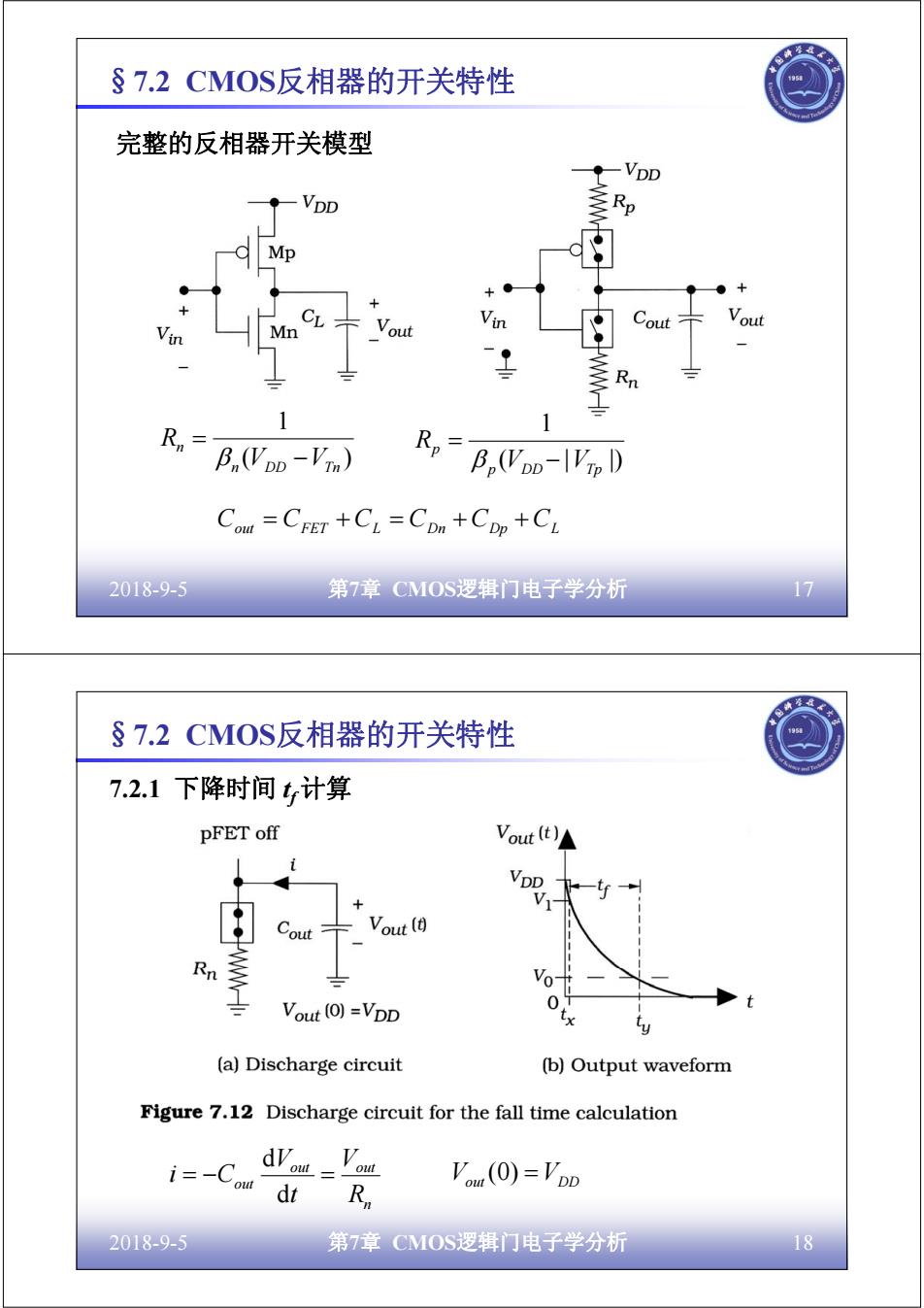

§7.2CMOS反相器的开关特性 完整的反相器开关模型 ◆-VDD VDD p Mp M Vout Cout Vout Rn B(VDD-Vma) R=B(Vpo-IVmD Cou=CFET+CL=Con+CDp+CL 2018-9-5 第7章CMOS逻辑门电子学分析 §7.2CMOS反相器的开关特性 7.2.1下降时间t计算 pFET off Vout (t) VDD. Cout Vout( Rn W-i 0 Vout (0)=VDD (a)Discharge circuit (b)Output waveform Figure 7.12 Discharge circuit for the fall time calculation i=-C out Vou()=VDD dt R 2018-9-5 第7章CMOS逻辑门电子学分析 18

2018-9-5 第7章 CMOS逻辑门电子学分析 17 §7.2 CMOS反相器的开关特性 完整的反相器开关模型 ( ) 1 n DD Tn n V V R − = β ( | |) 1 p DD Tp p V V R − = β Cout = CFET +CL = CDn +CDp +CL 2018-9-5 第7章 CMOS逻辑门电子学分析 18 §7.2 CMOS反相器的开关特性 7.2.1 下降时间 tf计算 n out out out R V t V i = −C = d d Vout =VDD (0)

§7.2CMOS反相器的开关特性 i=-Cou out Vout (t) dt R Vou()=VDp VpD Vou(t)=VpDen=RCoM 下降时间t定义: 0 从0.9VoD到0.1Voo的时间间隔。 out 0=ln9rn≈2.2t.=tm 1 ..t=ty-tx =Tn In10-t In 2018-9-5 第7章CMOS逻辑门电子学分析 19 §7.2CMOS反相器的开关特性 19 7.2.2上升时间t,计算 Rp Vout(t) VpD t Cout Vout( nFET off 0 Vout (0)=0V u (a)Charge circuit (b)Output waveform Figure 7.13 Rise time calculation i=Cou dvamVpp-Vam 'om(0)=0 dt Rp 2018-9-5 第7章CMOS逻辑门电子学分析 20

2018-9-5 第7章 CMOS逻辑门电子学分析 19 §7.2 CMOS反相器的开关特性 n out out out R V t V i = −C = d d Vout =VDD (0) n n out t ∴Vout t =VDDe n = R C − τ τ ( ) , 下降时间 tf定义: 从0.9VDD到0.1VDD的时间间隔。 DD n out t V V τ ln = − out DD n V V ∴t =τ ln f y x n n n n HL ∴t = t − t =τ −τ = ln 9τ ≈ 2.2τ = t 9 10 ln10 ln 2018-9-5 第7章 CMOS逻辑门电子学分析 20 §7.2 CMOS反相器的开关特性 p out DD out out R V V t V i C − = = d d Vout(0) = 0 7.2.2 上升时间 tr计算