第9章TMS320C54x硬件设计及接口技术 DSP硬件设计是DSP应用系统设计的基础。 一个DSP最小系统是由内部硬件资源如CPU、 片内外设、存储器(ROM、RAM或FLASH) 和最基本的外围辅助电路(电源、时钟晶振、 复位电路和仿真接口JTAG)组成。 般的实际应用系统是由最小系统和输入输 出接口、通信接口、人机交互接口、外部程 序存储器或数据存储器等外围扩展电路组成。 山东大学生物医学工程刘忠国 1

第9章 TMS320C54x硬件设计及接口技术 • DSP硬件设计是DSP应用系统设计的基础。 • 一个DSP最小系统是由内部硬件资源如CPU、 片内外设、存储器(ROM、RAM或FLASH) 和最基本的外围辅助电路(电源、时钟晶振、 复位电路和仿真接口JTAG)组成。 • 一般的实际应用系统是由最小系统和输入输 出接口、通信接口、人机交互接口、外部程 序存储器或数据存储器等外围扩展电路组成。 山东大学生物医学工程刘忠国 1

第9章TMS320C54x硬件设计及接口技术 目录 9.1基于C54x的DSP最小系统设计 9.2C54x外部总线结构 9.3存储器扩展 9.4AD、DIA与DSP的接口技术 9.5 Bootloader功能的实现 9.6C54x系统设计实例 9.7DSP系统的调试与抗干扰措施 山东大学生物医学工程刘忠国

第9章 TMS320C54x硬件设计及接口技术 目录 9.1 基于C54x的DSP最小系统设计 9.2 C54x外部总线结构 9.3 存储器扩展 9.4 A/D、D/A与DSP的接口技术 9.5 Bootloader功能的实现 9.6 C54x系统设计实例 9.7 DSP系统的调试与抗干扰措施 山东大学生物医学工程刘忠国 2

9.1基于C54x的DSP最小系统设计 >DSP最小系统就是指没有输入扩展、输出扩展、 除了片内通信通道也没有通信扩展的基本独立的、 功能极其有限的DSP系统。仅在DSP芯片基础上 增加了电源、时钟晶振、复位电路和仿真接口 JTAG. >最小系统是DSP系统硬件设计的基础。 >DSP最小系统的设计与DSP芯片结合的最紧密。 >最小系统正常工作是整个DSP硬件系统正常工作 的基础。 山东大学生物医学工程刘忠国 3

9.1 基于C54x的DSP最小系统设计 ➢ DSP最小系统就是指没有输入扩展、输出扩展、 除了片内通信通道也没有通信扩展的基本独立的、 功能极其有限的DSP系统。仅在DSP芯片基础上 增加了电源、时钟晶振、复位电路和仿真接口 JTAG。 ➢ 最小系统是DSP系统硬件设计的基础。 ➢ DSP最小系统的设计与DSP芯片结合的最紧密。 ➢ 最小系统正常工作是整个DSP硬件系统正常工作 的基础。 山东大学生物医学工程刘忠国 3

9.1基于C54x的DSP最小 U2 2 W FBPG 9.1.1DSP电源电路设计 1.单3.3V电源输出的电源管理芯片 函丽 out TPS7133,7233,7333,TPS75733 其引脚功能如表9.1所示。 0 TPS75733 引脚号 引脚名称 VO特性 引脚功能 1 EN I 输入使能 2 N I 输入电压 3 GND 地 4 OUTPUT 输出电压 5 FB/PG(power good) IO FB反馈输入PG输出 电压输出可调节的TPS75701是FB 4

4 OUTPUT O 输出电压 5 FB/PG(power good) I/O FB反馈输入/PG 输出 9.1 基于C54x的DSP最小系统设计 1.单3.3V电源输出的电源管理芯片 TPS7133,7233,7333, TPS75733 引脚号 引脚名称 I/O特性 引脚功能 1 EN I 输入使能 2 IN I 输入电压 3 GND 地 4 其引脚功能如表9.1所示。 9.1.1 DSP电源电路设计 电压输出可调节的TPS75701是FB

9.1.1DSP电源电路设计 1.单3.3V电源输出的电源管理芯片TPS7133,7233,7333 TPS75733应用电路 Rl 1K +5W g +3.3W 2 5 N EP的 +1 心2 1 47F 0.1F OUT C3 C4 10uF TP75733 0.1nF 亚 山东大学生物医学工程刘忠国 5

9.1.1 DSP电源电路设计 1.单3.3V电源输出的电源管理芯片TPS7133,7233,7333 TPS75733应用电路 山东大学生物医学工程刘忠国 5

9.1.1DSP电源电路设计 1.单3.3V电源输出的电源管理芯片TPS75733 ·TPS75733有两种封装形式(5针的T0-220封装和 T0-263表面贴封装),如图9.2所示 TO-220(KC)PACKAGE T0-263KTT))PACKAGE (TOP VIEW) (TOP VIEW) 形经7 IN C 2 3 4 GND 3 5 OUTPUT 4 PG 5 山东大学生物医学工程刘忠国 6

9.1.1 DSP电源电路设计 1. 单3.3V电源输出的电源管理芯片TPS75733 • TPS75733有两种封装形式(5针的TO–220封装 和 TO–263表面贴封装),如图9.2所示 山东大学生物医学工程刘忠国 6

9.1.1DSP电源电路设计 2.单1.8V电源输出的电源管理芯片:TPS75718(引脚用法 同TPS75733);TPS76818的典型电路如图9.3所示: 1 GND 8 RI GND PG IK 丽 +1.8W C2 FBANC 47uF 0.1mf 6 N OUT C4 C3 +5W 5 N out 10uF h.m时 TPS76818 GND 山东大学生物医学工程刘忠国 7

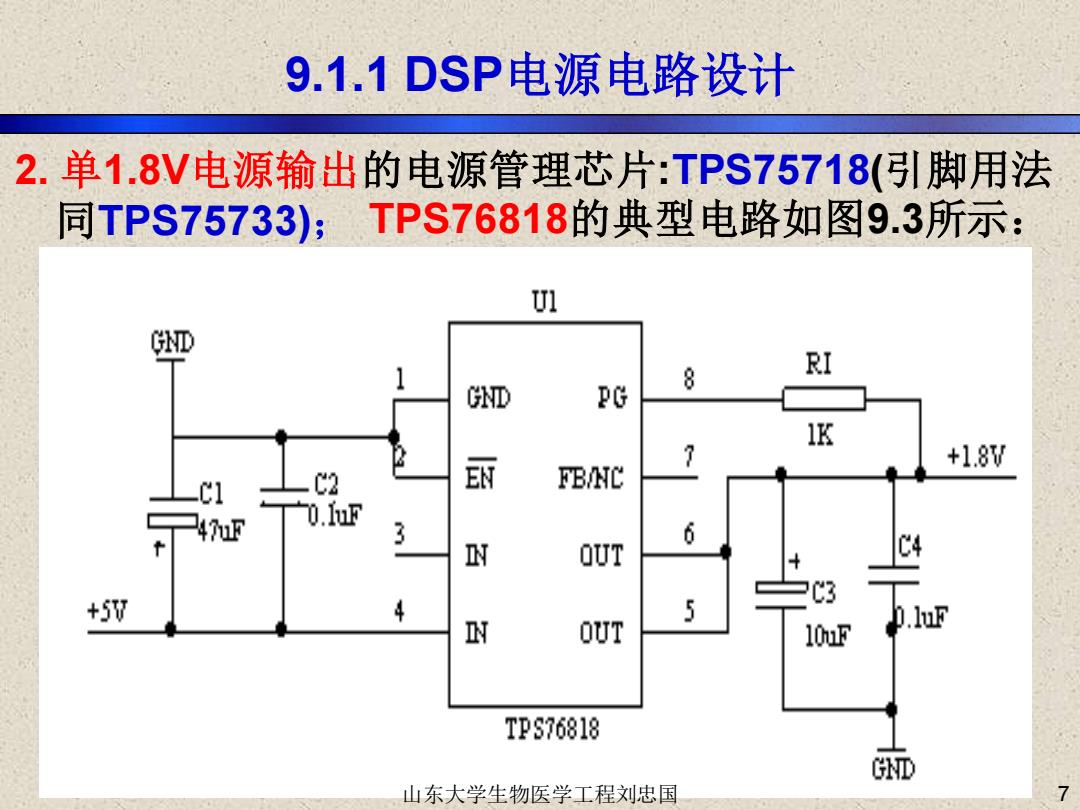

9.1.1 DSP电源电路设计 2. 单1.8V电源输出的电源管理芯片:TPS75718(引脚用法 同TPS75733); 山东大学生物医学工程刘忠国 7 TPS76818的典型电路如图9.3所示:

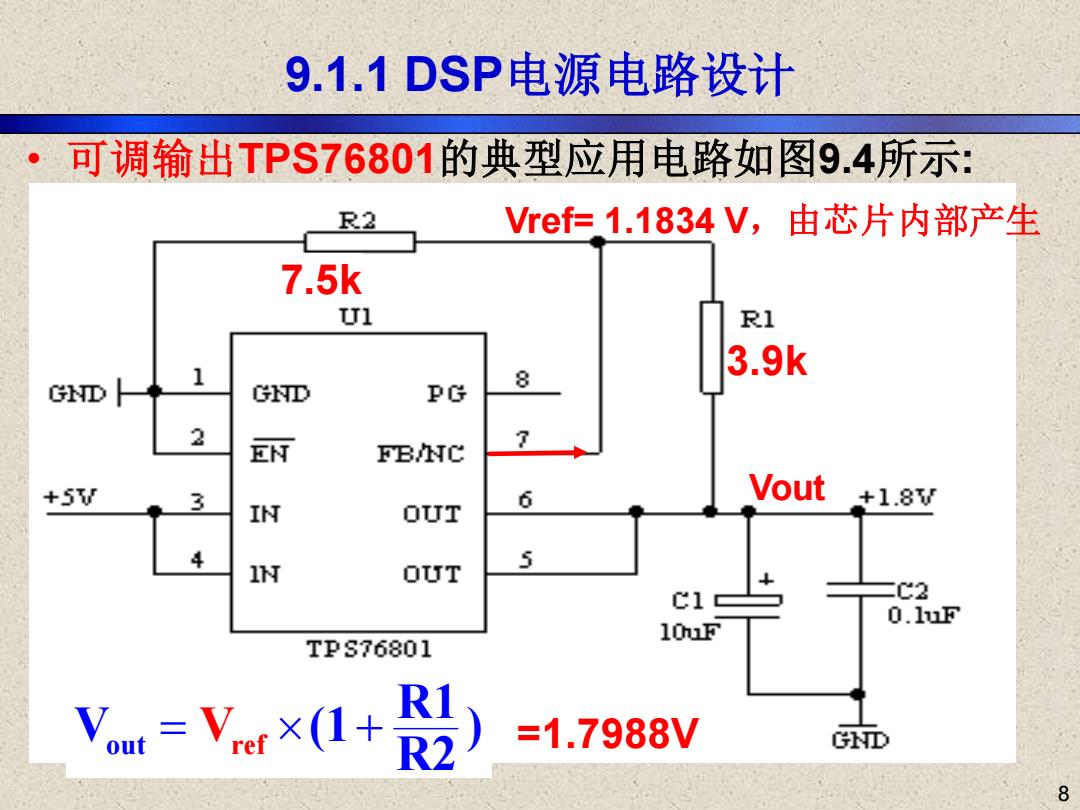

9.1.1DSP电源电路设计 可调输出TPS76801的典型应用电路如图9.4所示: R2 Vref=1.1834V,由芯片内部产生 7.5k Ul R1 1 3.9k 8 GND GND PG 2 EN FB/NC +5/ 3 6 Vout +18W IN OUT IN 5 OUT 二C2 0.1nF 10uF TPS76801 Va-Vax(l+) =1.7988V GND 8

9.1.1 DSP电源电路设计 out ref R1 V (1 ) 2 V R = + Vref= 1.1834 V,由芯片内部产生 • 可调输出TPS76801的典型应用电路如图9.4所示: 8 =1.7988V 7.5k 3.9k Vout

9.1.1DSP电源电路设计 TPS76801/TPS76818有两种封装形式(8-Pin SOIC封装和20-Pin TSSOP封装),如图9.5所示 PWP PACKAGE TOP VIEW) TSSOP GND/HSINK 1 20 GND:HSINK GND/HSINK 2 19 GND:HSINK SOIC GND 3 181 NC D PACKAGE 4 17 NC (TOP VIE仍 5 15 PG 0 6 15 FB/NC GND L 1 8 PG N 140 OUT EN 0 2 7 FB/NC NC 8 1310UT IN 3 6 GND/HSINK 0 9 12 GND/HSINK IN 2 4 5 OUT GND/HSINK 10 11 GND/HSINK NC-No internal connection 山东大学生物医学工程刘忠国 10

SOIC :Small Outline Integrated Circuit Package, 小外形集成电路封装 TSSOP就是Thin Shrink Small Outline Package的 缩写,(薄的缩小型SOP) 9.1.1 DSP电源电路设计 • TPS76801/TPS76818有两种封装形式(8-Pin SOIC 封装和20-Pin TSSOP封装),如图9.5所示 山东大学生物医学工程刘忠国 10 SOIC TSSOP

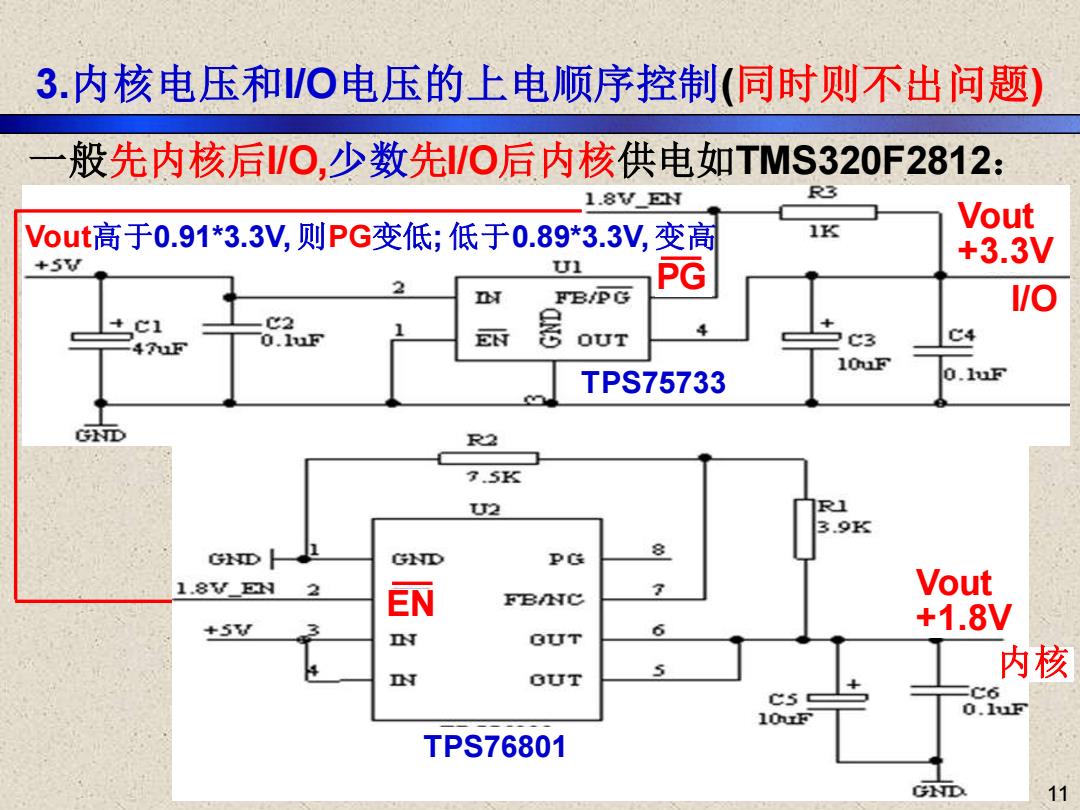

3.内核电压和O电压的上电顺序控制(同时则不出问题) 般先内核后VO,少数先l/O后内核供电如TMS320F2812: 1.8w_1N R3 Vout高于0.91*3.3V,则PG变低;低于0.89*3.3V,变高 1K Vout +5/ +3.3V Ul 2 PG n FB/PG 1/O C2 C4 47uF 0.1uF E OUT C3 10F TPS75733 0.1uF GND R2 了.5K U2 3.9K GND GND PG 8 1.8WN 2 EN Vout FB/TC +S/ +1.8V 3 I QUT 6 DT 5 内核 OUT C5 二C6 10uF 0.1uE TPS76801 GND 11

TPS75733 3.内核电压和I/O电压的上电顺序控制(同时则不出问题) 一般先内核后I/O,少数先I/O后内核供电如TMS320F2812: 11 TPS76801 Vout高于0.91*3.3V, 则PG变低; 低于0.89*3.3V, 变高 Vout +3.3V Vout +1.8V I/O 内核 PG EN