Cadence IC设计实瞼 实g验四、Diva Interactive Verification 实验目的:掌握DRC和LVS验证方法 版图绘制后要根据foundry厂的工艺要求进行DRC(Design Rule Checker)检查,编 辑好的版图必须通过LVS(Layout Versus Schematic)验证,检查是否与schematic电原理图 完全一致;版图中还可能存在一些悬空的器件和线网,通过电气规则检查ERC(Electrical Rule Check)可以发现这些错误。进行LVS和ERC之前,需要用Diva验证工具中的Extract 程序对版图进行器件提取:Extract还可以进行寄生参数提取,电路仿真程序可以调用这个 数据进行后仿真。 DIVA工具集包括以下部分: 1.设计规则检查(DRC) 2.提取Extractor::包括器件提取、版图寄生参数提取(LPE)、寄生电阻提取(PRE) 3.电气规则检查(ERC) 4.版图与线路图比较(LVS) 预备工作: cp /eva01/cdsmgr/ICDATA/DivaInt_5_0.tar tar -vxf Divalnt_5_0.tar cd diva 实验内容与步骤: 第一部分:DRC设计规则检查 一、进入DRC菜单: [1]、icfb [2]、在CIW窗口(icfb-Log:/…),点击Tools-Library Manager: [3]、Library列表框中点击design; Cell列表框中点击peakDetect: View列表框中双击layout::(或用鼠标右键open) (注:这是峰值检测器电路版图,你可以查看相应的schematic了解电路原理) [4]、在出现的Virtuoso Layout Editing窗口,点击Verify-->DRC…菜单。 出现下图DRC窗口:

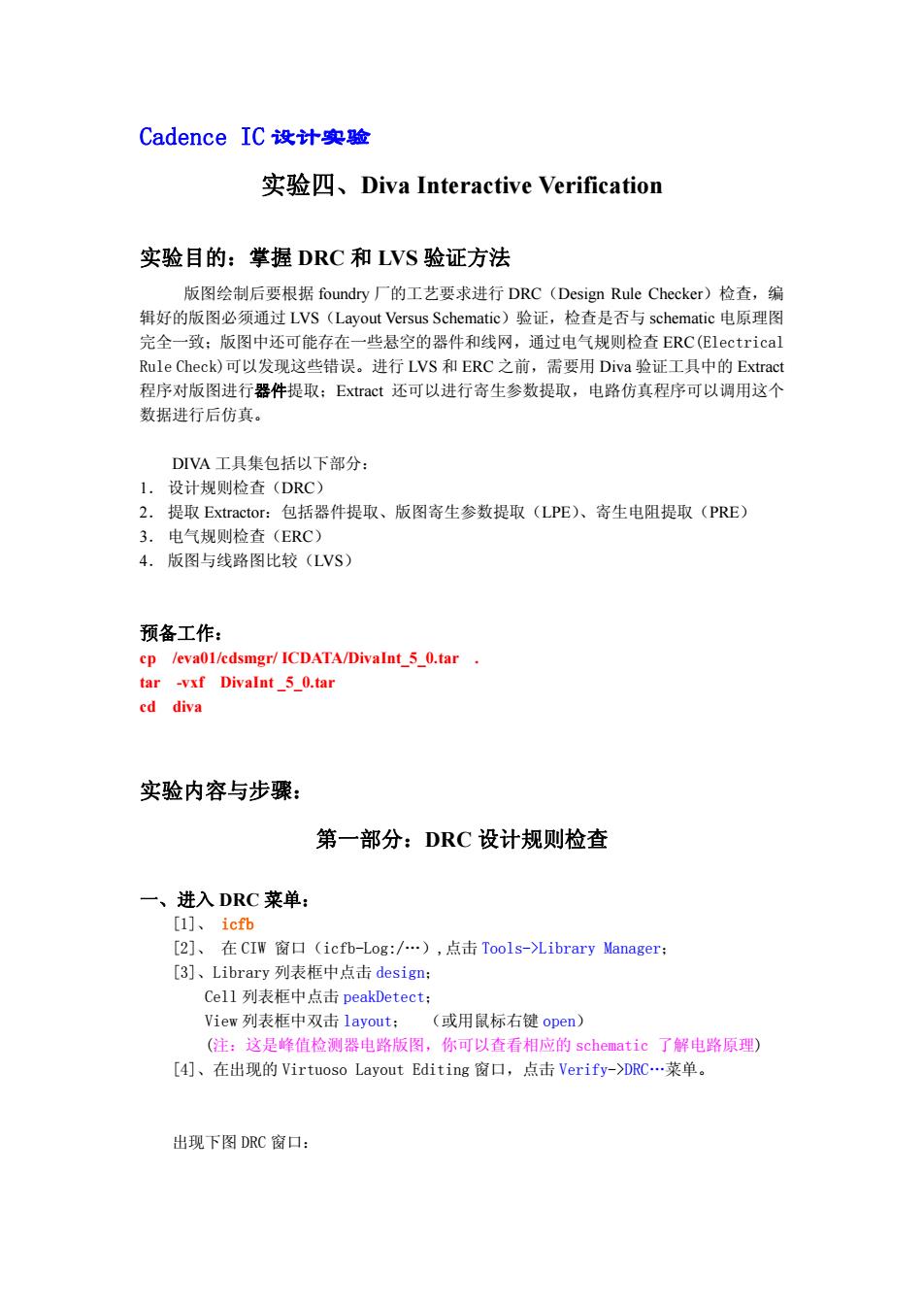

Cadence IC 设计实验 实验四、Diva Interactive Verification 实验目的:掌握 DRC 和 LVS 验证方法 版图绘制后要根据 foundry 厂的工艺要求进行 DRC(Design Rule Checker)检查,编 辑好的版图必须通过 LVS(Layout Versus Schematic)验证,检查是否与 schematic 电原理图 完全一致;版图中还可能存在一些悬空的器件和线网,通过电气规则检查 ERC(Electrical Rule Check)可以发现这些错误。进行 LVS 和 ERC 之前,需要用 Diva 验证工具中的 Extract 程序对版图进行器件提取;Extract 还可以进行寄生参数提取,电路仿真程序可以调用这个 数据进行后仿真。 DIVA 工具集包括以下部分: 1. 设计规则检查(DRC) 2. 提取 Extractor:包括器件提取、版图寄生参数提取(LPE)、寄生电阻提取(PRE) 3. 电气规则检查(ERC) 4. 版图与线路图比较(LVS) 预备工作: cp /eva01/cdsmgr/ ICDATA/DivaInt_5_0.tar . tar -vxf DivaInt _5_0.tar cd diva 实验内容与步骤: 第一部分:DRC 设计规则检查 一、进入 DRC 菜单: [1]、 icfb [2]、 在 CIW 窗口(icfb-Log:/…),点击 Tools->Library Manager; [3]、Library 列表框中点击 design; Cell 列表框中点击 peakDetect; View 列表框中双击 layout; (或用鼠标右键 open) (注:这是峰值检测器电路版图,你可以查看相应的 schematic 了解电路原理) [4]、在出现的 Virtuoso Layout Editing 窗口,点击 Verify->DRC…菜单。 出现下图 DRC 窗口:

DRC OK Cancel Defaults Apply Help Checking Method ◆flat◇hierarchical◇hier wfo optimization Checking Limit ◆ful◇incremental◇by area 《0a316 Sel by Cursor Switch Names Set Switches Run-Specific Command File Inclusion Limit 1000 Join Nets With Same Name Echo Commands ■ Rules File divaDRC.rul Rules Library ■desigr Machine ◆local◇emote Machine 二、查找某层(poly1层)DRC错误 [5]、在DRC窗口,点击右边的Set Switches按钮,在弹出列表中选择polyl,点击OK, 再点击DRC窗口OK。 在layout窗口中高亮闪烁显示polyl错误,你也可在CIW窗口查看DRC执行结果。 [6].在Virtuoso Layout Editing窗口,点击Verify->Markers-->Find…。弹出Find Marker框。 [7]、在Find Marker窗口置Zoom to Markers按纽有效,点击Next。 弹出marker text窗口显示错误信息,如果看不到错误形态,按下shift+f。 [8]、点击Virtuoso Layout Editing窗口左下方Ruler工具或k(按ESC取消工具), 测量高亮边框polyl宽度,比较marker text窗口显示的错误信息,按shift+-k取消 版图上的尺寸标记。 在Find Marker窗口: 点击Next寻找下一个错误f位置(Previous是查看前一个错误)。 连续点击Delete,.直到不显示错误为止(屏幕不再改变), 点击Cancel,f全屏,高亮闪烁的错误提示消失了。 注意:你并没改正版图错误,只是将错误提示delete掉了,若再次做DRC会发现错 误依旧。 三、另一种查找DRC错误的方法 [9]、选择Verify->DRC。 [10]、点击Set switchs按钮 在列表中选择allInterconnect,->OK,DRC窗口OK。 [Il]、DRC结束后(出现高亮闪烁的错误提示),选择Edit->search。 在Search窗口: 设置Zoom To Figure按纽有效

二、查找某层(poly1 层)DRC 错误 [5]、在 DRC 窗口,点击右边的 Set Switches 按钮,在弹出列表中选择 poly1,点击 OK, 再点击 DRC 窗口 OK。 在 layout 窗口中高亮闪烁显示 poly1 错误,你也可在 CIW 窗口查看 DRC 执行结果。 [6].在 Virtuoso Layout Editing 窗口,点击 Verify->Markers->Find…。弹出 Find Marker 框。 [7]、在 Find Marker 窗口置 Zoom to Markers 按纽有效,点击 Next。 弹出 marker text 窗口显示错误信息,如果看不到错误形态,按下 shift+f。 [8]、点击 Virtuoso Layout Editing 窗口左下方 Ruler 工具或 k(按 ESC 取消工具), 测量高亮边框 poly1 宽度,比较 marker text 窗口显示的错误信息,按 shift+k 取消 版图上的尺寸标记。 在 Find Marker 窗口: 点击 Next 寻找下一个错误 f 位置(Previous 是查看前一个错误)。 连续点击 Delete,直到不显示错误为止(屏幕不再改变), 点击 Cancel,f 全屏,高亮闪烁的错误提示消失了。 注意:你并没改正版图错误,只是将错误提示 delete 掉了,若再次做 DRC 会发现错 误依旧。 三、另一种查找 DRC 错误的方法 [9]、选择 Verify->DRC。 [10]、点击 Set switchs 按钮 在列表中选择 allInterconnect,->OK,DRC 窗口 OK。 [11]、DRC 结束后(出现高亮闪烁的错误提示),选择 Edit->search。 在 Search 窗口: 设置 Zoom To Figure 按纽有效

在Search for菜单:any shape,在in菜单:current cellView [l2]、点击Add Criteria,Search窗口中间出现一新选择行。 位于Search for下面最左边的选框内容改置为property,完成表格如下: property name:drcWhy =metall 点击Apply.屏幕将显示一个metall错误,由于你的设定,Search命令将只查找metal1 错误,总的错误数在Figure count栏显示。 [13]、点击几次Next [14]、点击Cancel,f全屏。 四、标注不进行DRC或Extracting的单元 [15]、在layout窗口找到单元fiducial(假设它是个测试基准单元) Ctrl+f(仅显示顶层Cell),在底部区域找到fiducial单元(不要与右边的fiduciald单元弄 混了) [l6]、点击选中fiducial单元,shift+x进入fiducial单元;(稍等) [l7、通过添加ivInclude Value性质阻止DRC对fiducial单元进行检查: A.在layout窗口中按下shift-+q,弹出Edit Cellview Properties窗口 B.置property按钮有效(黑) C.点击Edit Cellview Properties窗口中的左下方Add按钮 D. 在弹出的Add property表格设置如下: Name ivInclude Value Type Int Value 2 E.OK F.点击Edit Cellview Properties窗口中的OK: G.Save保存fiducial单元版图: H.shift-+b,返回到上一层版图。(稍等) [18]、在Layout Editing窗口,Verify-一>DRC: [19]、将DRC表中的Inclusion Limit设置为0。 [20、OK。 查看fiducial单元,不再有错误提示出现。 (注:fiducial单元是一个包含了许多不符合设计规则的测试单元,这个单元与电路没有 任何联系,在实际的芯片制造过程中,会有这样的单元存在,这样的单元的作用是 什么,你能想到吗?) 试一下f,Shift+f,Ctrl+f有什么区别? 五、改正DRC检查出来的错误 [21、根据前面介绍的第一种方法找到poly1的错误。 [22]、Ctrl+f(仅显示顶层Cell),找到control单元,点击选中control单元,shif+x进入control 单元。 (注:错误在in2和vcap中间的control单元中,必须进入control单元才能修改错误) [23]再次Verify->DRC,错误原因是什么? CIW中提示你有下列错误:

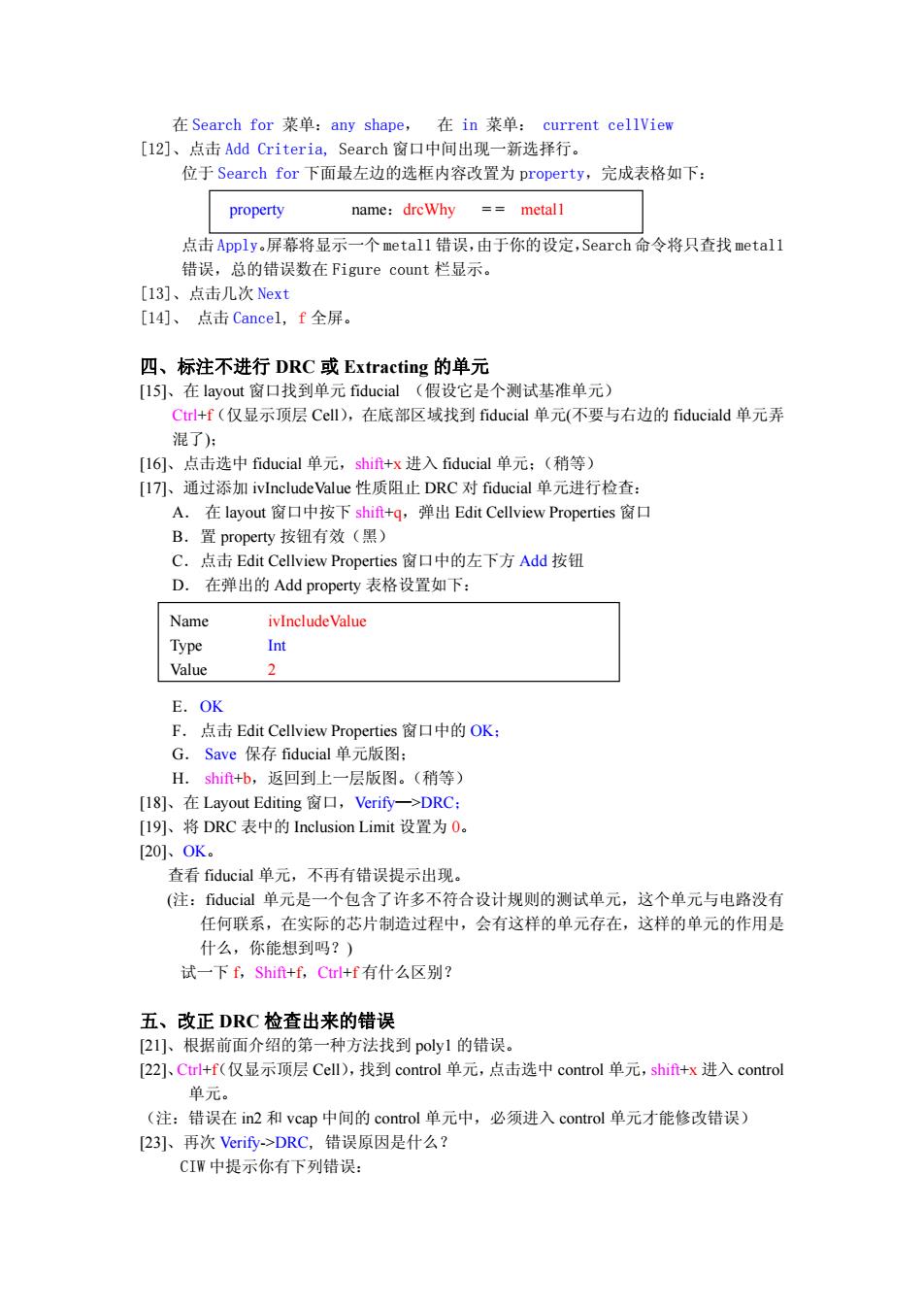

在 Search for 菜单:any shape, 在 in 菜单: current cellView [12]、点击 Add Criteria, Search 窗口中间出现一新选择行。 位于 Search for 下面最左边的选框内容改置为 property,完成表格如下: 点击 Apply。屏幕将显示一个 metal1 错误,由于你的设定,Search 命令将只查找 metal1 错误,总的错误数在 Figure count 栏显示。 [13]、点击几次 Next [14]、 点击 Cancel, f 全屏。 四、标注不进行 DRC 或 Extracting 的单元 [15]、在 layout 窗口找到单元 fiducial (假设它是个测试基准单元) Ctrl+f(仅显示顶层 Cell),在底部区域找到 fiducial 单元(不要与右边的 fiduciald 单元弄 混了); [16]、点击选中 fiducial 单元,shift+x 进入 fiducial 单元;(稍等) [17]、通过添加 ivIncludeValue 性质阻止 DRC 对 fiducial 单元进行检查: A. 在 layout 窗口中按下 shift+q,弹出 Edit Cellview Properties 窗口 B.置 property 按钮有效(黑) C.点击 Edit Cellview Properties 窗口中的左下方 Add 按钮 D. 在弹出的 Add property 表格设置如下: E.OK F.点击 Edit Cellview Properties 窗口中的 OK; G. Save 保存 fiducial 单元版图; H. shift+b,返回到上一层版图。(稍等) [18]、在 Layout Editing 窗口,Verify—>DRC; [19]、将 DRC 表中的 Inclusion Limit 设置为 0。 [20]、OK。 查看 fiducial 单元,不再有错误提示出现。 (注:fiducial 单元是一个包含了许多不符合设计规则的测试单元,这个单元与电路没有 任何联系,在实际的芯片制造过程中,会有这样的单元存在,这样的单元的作用是 什么,你能想到吗?) 试一下 f,Shift+f,Ctrl+f 有什么区别? 五、改正 DRC 检查出来的错误 [21]、根据前面介绍的第一种方法找到 poly1 的错误。 [22]、Ctrl+(仅显示顶层 f Cell),找到 control 单元,点击选中 control 单元,shift+x 进入 control 单元。 (注:错误在 in2 和 vcap 中间的 control 单元中,必须进入 control 单元才能修改错误) [23]、再次 Verify->DRC, 错误原因是什么? CIW 中提示你有下列错误: property name:drcWhy = = metal1 Name ivIncludeValue Type Int Value 2

Minimum poly1 width=0.6 (单位um) Minimum polylspacing=1.0 Poly1 extension past pdiff=0.4 用标尺量一下,错误原因是什么? [24]、鼠标左键选中高亮的poly1,q [25]、在Edit Path Properties窗口,将Width栏0.4(u)改为0.6。OK [26]Save [27小、CIW第3个错误提示是指,poly1超过pdif的最短露头应为0.4um,而NAND2单元 中左边poly 1超过pdiff的露头仅为0.3um,需要改正它。 这个错误出现在control单元中的NAND2单元中,所以必须进入NAND2单元修改。 I)。f全屏),然后Ctr+f(仅显示顶层Cell),找到NAND2单元,点击选中NAND2 单元,shift-+x进入NAND2单元。 2)。选中出错poly 1,q。在Edit Rectangle Properties窗口,将Top栏的数据增加O.I。 OK。 3)。用标尺(k)量一下poly1露头是否增加到0.4了。Shift+k取消标尺。 [28]、Save保存单元版图; [29]、shif+b,返回到上一层版图(control单元)。Shift+f。 [30、Verify-.>DRC,(仍然是查poly1),此时CIW只提示还有1个错误: Minimum polylspacing=1.0. 用标尺量一下出错处的两个poly1之间的间距仅有0.4。 [3l]、用标尺标出Path移动的位置,ESC,将出错poly1 Path中心线往上拉(s)到正确位置。 注意:选中心线是件不容易的事,你可以先将点击polyl drawing为LSW当前层,然 后点击NS置所有LSW层不能选,再用鼠标右键点击polyl drawing使其可选。在layout窗 口,shit+r,点击出错poy1直到它边沿变成粗橘红色(不是白色),s,移动鼠标到中心线 上就可以拖动了。 LSW中AS。 要特别当心,或许你会产生新的错误,比如移动了其它对象,就用ESC取消。 shift-+k(取消标尺)->Verify/Marker/Find/Delete(取消错误提示)->Save [32]、,shif+b回到顶层原理图,再对poly1进行DRC,CIW窗口提示:Total errors found:0 Save DIY 对metall和metal2进行DRC并改正错误。 (提示:metall有一个错误,metal22有两个错误)

Minimum poly1 width = 0.6 (单位 um) Minimum poly1spacing = 1.0 Poly1 extension past pdiff = 0.4 用标尺量一下,错误原因是什么? [24]、鼠标左键选中高亮的 poly1,q [25]、在 Edit Path Properties 窗口,将 Width 栏 0.4(u)改为 0.6。OK [26]、Save [27]、CIW 第 3 个错误提示是指,poly1 超过 pdiff 的最短露头应为 0.4u m,而 NAND2 单元 中左边 poly1 超过 pdiff 的露头仅为 0.3um,需要改正它。 这个错误出现在 control 单元中的 NAND2 单元中,所以必须进入 NAND2 单元修改。 1)。f(全屏),然后 Ctrl+f(仅显示顶层 Cell),找到 NAND2 单元,点击选中 NAND2 单元,shift+x 进入 NAND2 单元。 2)。选中出错 poly1,q。在 Edit Rectangle Properties 窗口,将 Top 栏的数据增加 0.1。 OK。 3)。用标尺(k)量一下 poly1 露头是否增加到 0.4 了。Shift+k 取消标尺。 [28]、Save 保存单元版图; [29]、shift+b,返回到上一层版图(control 单元)。Shift + f。 [30]、Verify->DRC,(仍然是查 poly1),此时 CIW 只提示还有 1 个错误: Minimum poly1spacing = 1.0。 用标尺量一下出错处的两个 poly1 之间的间距仅有 0.4。 [31]、用标尺标出 Path 移动的位置,ESC,将出错 poly1 Path 中心线往上拉(s)到正确位置。 注意:选中心线是件不容易的事,你可以先将点击 poly1 drawing 为 LSW 当前层,然 后点击 NS 置所有 LSW 层不能选,再用鼠标右键点击 poly1 drawing 使其可选。在 layout 窗 口,shift+r,点击出错 poly1 直到它边沿变成粗橘红色(不是白色),s,移动鼠标到中心线 上就可以拖动了。 LSW 中 AS。 要特别当心,或许你会产生新的错误,比如移动了其它对象,就用 ESC 取消。 shift+k(取消标尺)-> Verify/Marker/Find/Delete(取消错误提示)->Save [32]、,shift+b 回到顶层原理图,再对 poly1 进行 DRC,,CIW 窗口提示:Total errors found: 0 Save DIY 对 metal1 和 metal2 进行 DRC 并改正错误。 (提示:metal1 有一个错误,metal2 有两个错误)

第二部分: Extraction 一、运行extraction [1]、在peakDetect版图窗口选择Verify->Extract. [2]、设置Extractor表格: Extract Method flat [3引、点击OK。Extraction开始,在运行过程中你可以在CIW窗口看到运行情况, 你看到的最终信息为: Total errors found:0 生成peakDetect单元extracted View. [4]、将peakDetect版图窗口最小化,留作以后使用。 二、查看Extracted视图 [5]、打开peakDetect单元extracted视图 [6]、将in2和vcap压焊管脚(PN方块)之间的control单元放大,方法是用鼠标 右键按住拖出一长方区域,然后松开鼠标。你可以看到pmos,nmos器件符号,表 明设计己经被提取,进一步放大符号,可以看到器件的参数也已经被提取: [7、按下e[或Options->Display。.。] [8]、在Display Options表中,选中Display Control段的Nets,点击Apply 从器件引脚出发的飞线说明器件的连接也已经被提取 [9]、如果已经看到飞线,关掉刚才选中的Nts选项,点击OK [10]、f全屏 [ll]、选择Verify-->Probe.., 注意:只有Extracted和schematic视图可以进行probe 「121、用鼠标进行网络探测(方法一) l)。在弹出的Probing窗口中点击一下Add Net 2)。点击extracted视图中vinput压焊管脚,整个vinput网络被高亮显示出来 [13]、用名字进行网络探测(方法二): 1)。点击Add net 2)。在CIW窗口(icfb-log:/。。)键入“vdd!”(包括引号),Enter 整个vdd!网络被高亮显示出来 [14]、解释探测结果 a.选择OnCW选项进行解释,所有的解释将显示在CIW窗口 b.点击Probing窗口中左下方Explain c.点击vdd!压焊管脚 CIW窗口中显示网点的名称: Object type:net Object name:/vdd! [15]、删除探测结果 a.点击Probing窗口Remove Nets b.点击vdd!,所有关于vdd!的显示被取消 c.点击Remove all,所有的高亮显示被去除 [l6]、Probing窗口Cancel

第二部分: Extraction 一、运行 extraction [1]、在 peakDetect 版图窗口选择 Verify->Extract… [2]、设置 Extractor 表格: [3]、点击 OK。Extraction 开始,在运行过程中你可以在 CIW 窗口看到运行情况, 你看到的最终信息为: Total errors found : 0 生成 peakDetect 单元 extracted View。 [4]、将 peakDetect 版图窗口最小化,留作以后使用。 二、查看 Extracted 视图 [5]、打开 peakDetect 单元 extracted 视图 [6]、将 in2 和 vcap 压焊管脚(PIN 方块)之间的 control 单元放大,方法是用鼠标 右键按住拖出一长方区域,然后松开鼠标。你可以看到 pmos,nmos 器件符号,表 明设计已经被提取,进一步放大符号,可以看到器件的参数也已经被提取; [7]、按下 e [或 Options->Display。。。] [8]、在 Display Options 表中,选中 Display Control 段的 Nets,点击 Apply 从器件引脚出发的飞线说明器件的连接也已经被提取 [9]、如果已经看到飞线,关掉刚才选中的 Nets 选项,点击 OK [10]、f 全屏 [11]、选择 Verify->Probe…, 注意:只有 Extracted 和 schematic 视图可以进行 probe [12]、用鼠标进行网络探测(方法一) 1) 。在弹出的 Probing 窗口中点击一下 Add Net 2) 。点击 extracted 视图中 vinput 压焊管脚,整个 vinput 网络被高亮显示出来 [13]、用名字进行网络探测(方法二): 1)。点击 Add net 2)。在 CIW 窗口(icfb-log:/。。。)键入“vdd!”(包括引号),Enter 整个 vdd!网络被高亮显示出来 [14]、 解释探测结果 a.选择 On CIW 选项进行解释,所有的解释将显示在 CIW 窗口 b.点击 Probing 窗口中左下方 Explain c.点击 vdd!压焊管脚 CIW 窗口中显示网点的名称: Object type : net Object name : /vdd! [15]、删除探测结果 a.点击 Probing 窗口 Remove Nets b.点击 vdd!,所有关于 vdd!的显示被取消 c.点击 Remove all,所有的高亮显示被去除 [16]、Probing 窗口 Cancel。 Extract Method flat

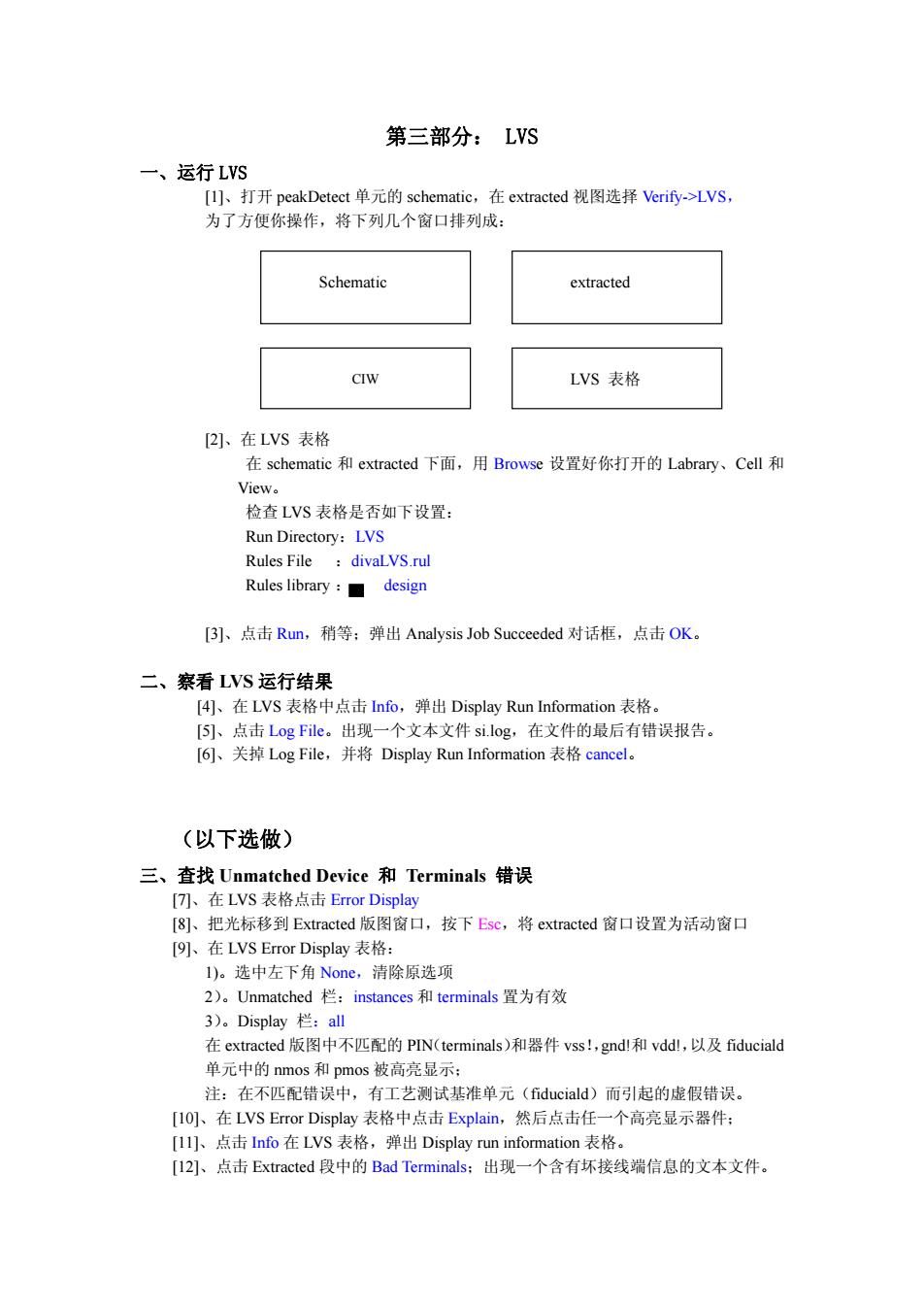

第三部分:LVS 一、运行LVS [l]、打开peakDetect单元的schematic,在extracted视图选择Verify->LVS, 为了方便你操作,将下列几个窗口排列成: Schematic extracted CIW LVS表格 [2]、在LVS表格 在schematic和extracted下面,用Browse设置好你打开的Labrary、Ccll和 View。 检查LVS表格是否如下设置: Run Directory:LVS Rules File divaLVS.rul Rules library:design [3]、点击Run,稍等;弹出Analysis Job Succeeded对话框,点击OK。 二、察看LVS运行结果 [4]、在LVS表格中点击lnfo,弹出Display Run Information表格。 [S]、点击Log File。出现一个文本文件si.log,在文件的最后有错误报告。 [6]、关掉Log File,并将Display Run Information表格cancel。. (以下选做) 三、查找Unmatched Device和Terminals错误 [T)、在LVS表格点击Error Display [8]、把光标移到Extracted版图窗口,按下Esc,将extracted窗口设置为活动窗口 [9]、在LVS Error Display表格: l1)。选中左下角None,清除原选项 2)。Unmatched栏:instances和terminals置为有效 3)。Display栏:all 在extracted版图中不匹配的PN(terminals)和器件vss!,gnd!和vddl,以及fiduciald 单元中的nmos和pmos被高亮显示; 注:在不匹配错误中,有工艺测试基准单元(fiduciald)而引起的虚假错误。 [1O]、在LVS Error Display表格中点击Explain,然后点击任一个高亮显示器件: [1l]、点击Info在LVS表格,弹出Display run information表格。 [l2]、点击Extracted段中的Bad Terminals;出现一个含有坏接线端信息的文本文件

第三部分: LVS 一、运行 LVS [1]、打开 peakDetect 单元的 schematic,在 extracted 视图选择 Verify->LVS, 为了方便你操作,将下列几个窗口排列成: [2]、在 LVS 表格 在 schematic 和 extracted 下面,用 Browse 设置好你打开的 Labrary、Cell 和 View。 检查 LVS 表格是否如下设置: Run Directory:LVS Rules File :divaLVS.rul Rules library : design [3]、点击 Run,稍等;弹出 Analysis Job Succeeded 对话框,点击 OK。 二、察看 LVS 运行结果 [4]、在 LVS 表格中点击 Info,弹出 Display Run Information 表格。 [5]、点击 Log File。出现一个文本文件 si.log,在文件的最后有错误报告。 [6]、关掉 Log File,并将 Display Run Information 表格 cancel。 (以下选做) 三、查找 Unmatched Device 和 Terminals 错误 [7]、在 LVS 表格点击 Error Display [8]、把光标移到 Extracted 版图窗口,按下 Esc,将 extracted 窗口设置为活动窗口 [9]、在 LVS Error Display 表格: 1)。选中左下角 None,清除原选项 2)。Unmatched 栏:instances 和 terminals 置为有效 3)。Display 栏:all 在 extracted 版图中不匹配的 PIN(terminals)和器件 vss!,gnd!和 vdd!,以及 fiduciald 单元中的 nmos 和 pmos 被高亮显示; 注:在不匹配错误中,有工艺测试基准单元(fiduciald)而引起的虚假错误。 [10]、在 LVS Error Display 表格中点击 Explain,然后点击任一个高亮显示器件; [11]、点击 Info 在 LVS 表格,弹出 Display run information 表格。 [12]、点击 Extracted 段中的 Bad Terminals;出现一个含有坏接线端信息的文本文件。 Schematic extracted CIW LVS 表格

[13]、浏览一下文本,然后关掉它。 [14]、在LVS Error Display表中,点击Clear Display [lS]、将LVS Error Display和Display Run Information表格Cancel.。 四、排除对fiduciald基准测试单元的检测,更正虚假的不匹配错误 对fiduciald单元添加ivIncludeValue属性 [16]、打开fiduciald版图 [17)]、编辑此单元的属性,将ivInclude Value属性值设为2: a.在版图窗口按下shift+-q b.在Edit Cell Properties表格中点击Property按钮 c.点击Add d.设置Add Property表格: Name ivInclude Value Type int Value 2 e.在Add Property和Edit Cell Properties两个表格中分别点击OK [18]、保存并关掉fiduciald版图。 五、重新进行Extracting和LVS [19]、打开peakDetect版图 [2o]、选择Verify->Extract,.将Inclusion Limit设置为O,所有ivInclude Value大于零的单 元都将被排除,不被检测,点击OK。 [21]、关掉peakDetect单元Layout版图窗口。 [22]、在peakDetect单元extracted窗口,选择Window-一>Redraw,刷新extracted窗口, 确定fiducial和fiduciald单元不再显示: [23]、在LVS表中点击Run,出现对话框,OK。 [24]、用LVS表的Info来查看运行结果,点击Log file,查看结果,有1个merged类 型的net(错误)。 关掉si.log文件。 六、在原理图中查找merged net 原理图中的merged error是由于版图中有短路。 [25]、在LVS表格点击Error Display。 [26]、在原理图窗口点击,按下EsC激活。 [2刀、在LVS Error Display表格,点击None,然后Merged项选择nets,点击Display 栏First,左边的放大器和输出net被高亮显示,在LVS Error Display表格有解释: Net /132/net18 merged with /net12. 注:这个错误是由于amplifier单元版图上不小心放了一块矩形的metall引起的。它引 起了运放输出netl2和amplifier(器件名I32)中netl8的短路(错误连接)。你可以用q查 看一下网线标号。 [28]、在原理图窗口选择出错amplifier,按下shif+x(稍等),进入下一层。 [29]、将LVS Error Display表格Cancel

[13]、浏览一下文本,然后关掉它。 [14]、在 LVS Error Display 表中,点击 Clear Display [15]、将 LVS Error Display 和 Display Run Information 表格 Cancel。 四、排除对 fiduciald 基准测试单元的检测,更正虚假的不匹配错误 对 fiduciald 单元添加 ivIncludeValue 属性 [16]、打开 fiduciald 版图 [17]、编辑此单元的属性,将 ivIncludeValue 属性值设为 2: a. 在版图窗口按下 shift+q b. 在 Edit Cell Properties 表格中点击 Property 按钮 c. 点击 Add d. 设置 Add Property 表格: e.在 Add Property 和 Edit Cell Properties 两个表格中分别点击 OK [18]、保存并关掉 fiduciald 版图。 五、重新进行 Extracting 和 LVS [19]、打开 peakDetect 版图 [20]、选择 Verify->Extract,将 Inclusion Limit 设置为 0,所有 ivIncludeValue 大于零的单 元都将被排除,不被检测,点击 OK。 [21]、关掉 peakDetect 单元 Layout 版图窗口。 [22]、在 peakDetect 单元 extracted 窗口,选择 Window—>Redraw,刷新 extracted 窗口, 确定 fiducial 和 fiduciald 单元不再显示; [23]、在 LVS 表中点击 Run,出现对话框, OK。 [24]、用 LVS 表的 Info 来查看运行结果,点击 Log file,查看结果,有 1 个 merged 类 型的 net(错误)。 关掉 si.log 文件。 六、在原理图中查找 merged net 原理图中的 merged error 是由于版图中有短路。 [25]、在 LVS 表格点击 Error Display。 [26]、在原理图窗口点击,按下 Esc 激活。 [27]、在 LVS Error Display 表格,点击 None,然后 Merged 项选择 nets,点击 Display 栏 First,左边的放大器和输出 net 被高亮显示,在 LVS Error Display 表格有解释: Net /I32/net18 merged with /net12. 注:这个错误是由于 amplifier 单元版图上不小心放了一块矩形的 metal1 引起的。它引 起了运放输出 net12 和 amplifier(器件名 I32)中 net18 的短路(错误连接)。你可以用 q 查 看一下网线标号。 [28]、在原理图窗口选择出错 amplifier,按下 shift+x(稍等),进入下一层。 [29]、将 LVS Error Display 表格 Cancel。 Name ivIncludeValue Type int Value 2

七、在schematic原理图和Extracted视图之间进行交互探查(Cross Probe) [30]、在peakDetect单元extracted视图,选择Verify-Probe,在原理图中按下Esc。 [31]、选中Probing表格中的cross probe matched,点击Add net,.在schematic原理图中用 鼠标选择出错的输出net,在extracted视图中的相应net被高亮显示。 [32]、用下列方法找出错误: 分析一下错误位置:参照schematic它应该在晶体管Q0的集电极和基极之间。 将extracted出错区域放大。点击Add Dev,在原理图中点击QO:用同样方法先点 击Add dev,再点击器件CO,RO,你能够判断出extracted版图中Q0的集电极和基极 吗?在extracted视图中找到短路错误了吗?(电容下面) [33]、点击Probing表格中Remove All,然后cancel probing表格。在amplifier原理图中 按下shift+-b,返回到peakDetect原理图。 八、更正版图中短路错误 [34]、在peakDetect单元layout视图中删掉刚才找到的矩形metall并Save,重新对layout 进行extract,extracted版图中的短路metall消失了;Save extracted版图。 [35]、对extracted版图进行Verify->LVS->Run,查看info->Log file(在Display Run

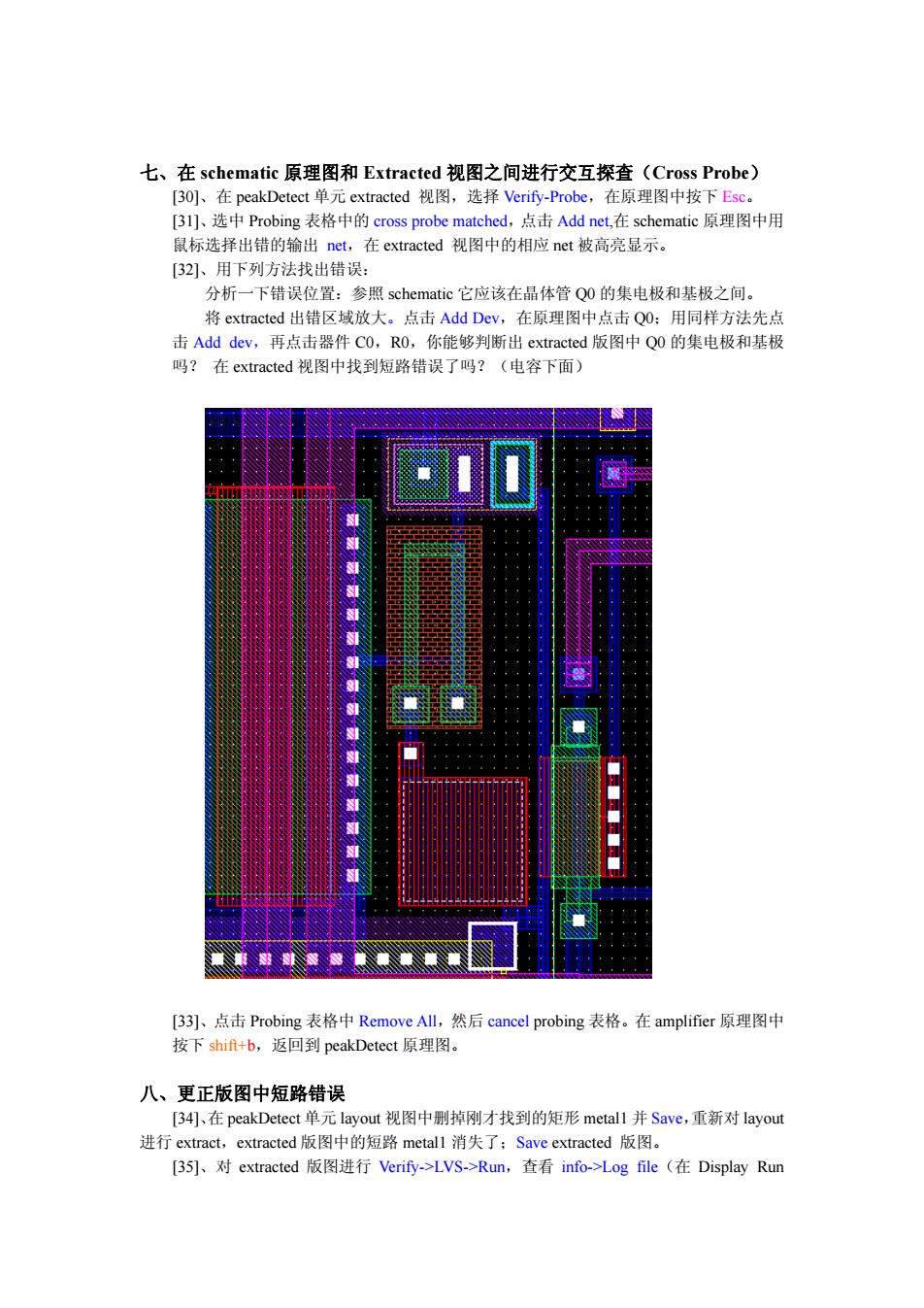

七、在 schematic 原理图和 Extracted 视图之间进行交互探查(Cross Probe) [30]、在 peakDetect 单元 extracted 视图,选择 Verify-Probe,在原理图中按下 Esc。 [31]、选中 Probing 表格中的 cross probe matched,点击 Add net,在 schematic 原理图中用 鼠标选择出错的输出 net,在 extracted 视图中的相应 net 被高亮显示。 [32]、用下列方法找出错误: 分析一下错误位置:参照 schematic 它应该在晶体管 Q0 的集电极和基极之间。 将 extracted 出错区域放大。点击 Add Dev,在原理图中点击 Q0;用同样方法先点 击 Add dev,再点击器件 C0,R0,你能够判断出 extracted 版图中 Q0 的集电极和基极 吗? 在 extracted 视图中找到短路错误了吗?(电容下面) [33]、点击 Probing 表格中 Remove All,然后 cancel probing 表格。在 amplifier 原理图中 按下 shift+b,返回到 peakDetect 原理图。 八、更正版图中短路错误 [34]、在 peakDetect 单元 layout 视图中删掉刚才找到的矩形 metal1 并 Save,重新对 layout 进行 extract,extracted 版图中的短路 metal1 消失了;Save extracted 版图。 [35]、对 extracted 版图进行 Verify->LVS->Run,查看 info->Log file(在 Display Run

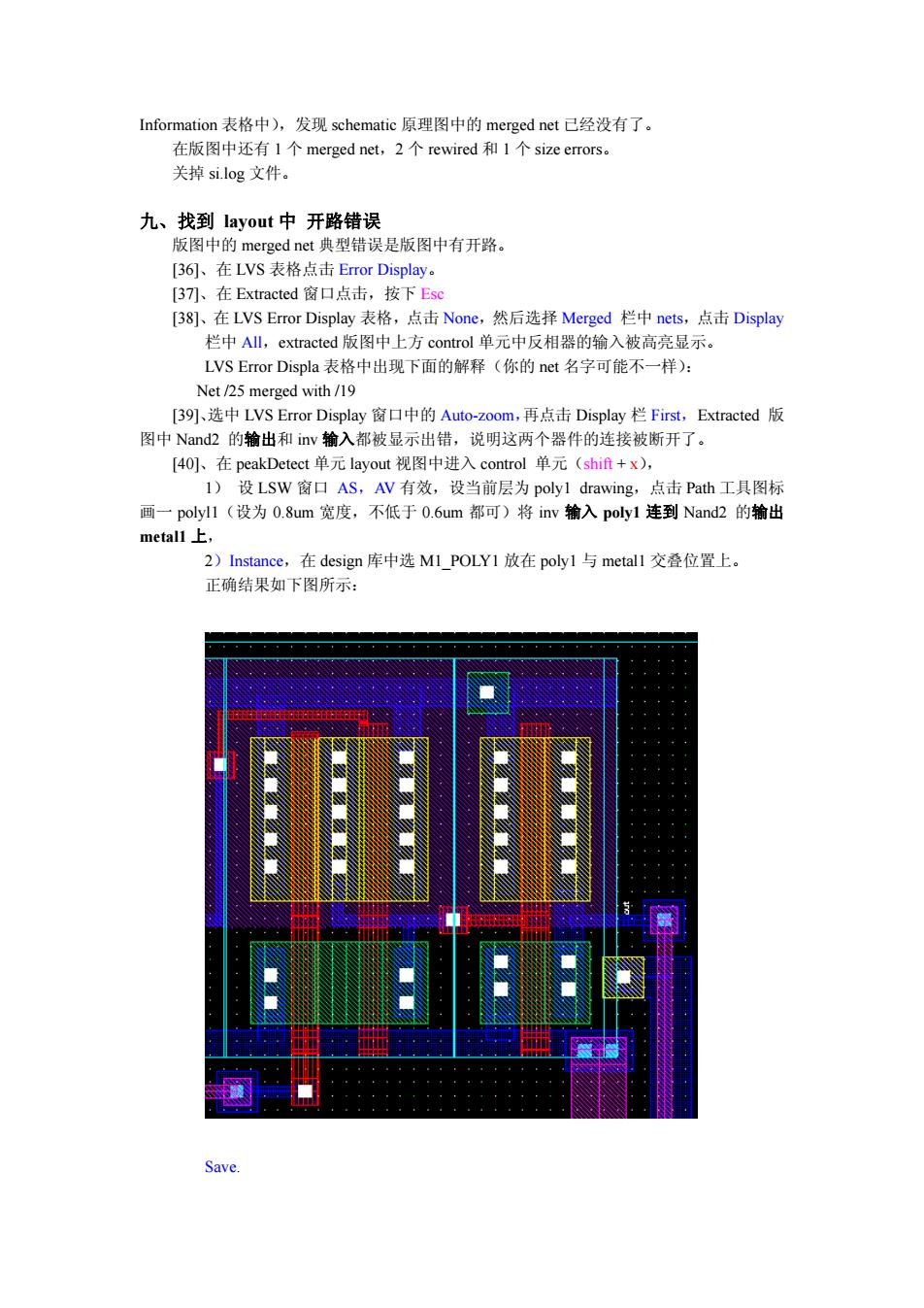

Information表格中),发现schematic原理图中的merged net己经没有了。 在版图中还有l个merged net,.2个rewired和1个size errors。 关掉si.log文件。 九、找到layout中开路错误 版图中的merged net典型错误是版图中有开路。 [36]、在LVS表格点击Error Display。 [37)]、在Extracted窗口点击,按下Esc [38]、在LVS Error Display表格,点击None,然后选择Merged栏中nets,点击Display 栏中All,extracted版图中上方control单元中反相器的输入被高亮显示。 LVS Error Displa表格中出现下面的解释(你的net名字可能不一样): Net/25 merged with/19 [39]、选中LVS Error Display窗口中的Auto-zoom,再点击Display栏First,.Extracted版 图中Nand2的输出和inv输入都被显示出错,说明这两个器件的连接被断开了。 [40]、在peakDetect单元layout视图中进入control单元(shif+x), I)设LSW窗口AS,AV有效,设当前层为polyl drawing,点击Path工具图标 画一polyl1(设为0.8um宽度,不低于0.6um都可)将inv输入poly1连到Nand2的输出 metall上, 2)nstance,.在design库中选MI POLY1放在poly1与metall交叠位置上。 正确结果如下图所示: Save

Information 表格中),发现 schematic 原理图中的 merged net 已经没有了。 在版图中还有 1 个 merged net,2 个 rewired 和 1 个 size errors。 关掉 si.log 文件。 九、找到 layout 中 开路错误 版图中的 merged net 典型错误是版图中有开路。 [36]、在 LVS 表格点击 Error Display。 [37]、在 Extracted 窗口点击,按下 Esc [38]、在 LVS Error Display 表格,点击 None,然后选择 Merged 栏中 nets,点击 Display 栏中 All,extracted 版图中上方 control 单元中反相器的输入被高亮显示。 LVS Error Displa 表格中出现下面的解释(你的 net 名字可能不一样): Net /25 merged with /19 [39]、选中 LVS Error Display 窗口中的 Auto-zoom,再点击 Display 栏 First, Extracted 版 图中 Nand2 的输出和 inv 输入都被显示出错,说明这两个器件的连接被断开了。 [40]、在 peakDetect 单元 layout 视图中进入 control 单元(shift + x), 1) 设 LSW 窗口 AS,AV 有效,设当前层为 poly1 drawing,点击 Path 工具图标 画一 polyl1(设为 0.8um 宽度,不低于 0.6um 都可)将 inv 输入 poly1 连到 Nand2 的输出 metal1 上, 2)Instance,在 design 库中选 M1_POLY1 放在 poly1 与 metal1 交叠位置上。 正确结果如下图所示: Save

shift+b返回顶层版图。 [41]、改正后重新进行extract和LVS,查看log file,merged net错误没有了。 关掉si.log文件和Display Run Information表格。 十、查找size errors [42]、在schematic或者extracted窗口中按下Esc,在LVS表格点击Error Display: [43]、在Error Display表中,点击None,Unmatched选parameters,然后Display选All。 Size error将在两个视图中显示出来,extracted中间的nmos和原理图中的nmos都 被高亮显示。 [44]、点击Auto-Zoom,first,在LVS error Display中将显示相关的解释: Gate width error:Sch=2e-06 Lay=4e-06,Gate length:Sch=le-05 lay=le-05 [45]、Cancel LVS Error Display表格。 [46]、在peakDetect layout版图中找到错误的nmos单元,鼠标左键点击选中,按q进 入编辑属性,点击Parameter,将width改为2u,OK。 [47刀、此时nmos的沟道宽度已经改好,将nmos移动到合适的位置。 [48]、Save。关闭所有的窗口

shift + b 返回顶层版图。 [41]、改正后重新进行 extract 和 LVS,查看 log file,merged net 错误没有了。 关掉 si.log 文件和 Display Run Information 表格。 十、查找 size errors [42]、在 schematic 或者 extracted 窗口中按下 Esc,在 LVS 表格点击 Error Display; [43]、在 Error Display 表中,点击 None,Unmatched 选 parameters,然后 Display 选 All。 Size error 将在两个视图中显示出来,extracted 中间的 nmos 和原理图中的 nmos 都 被高亮显示。 [44]、点击 Auto-zoom,first,在 LVS error Display 中将显示相关的解释: Gate width error: Sch=2e-06 Lay=4e-06,Gate length: Sch=1e-05 lay=1e-05 [45]、Cancel LVS Error Display 表格。 [46]、在 peakDetect layout 版图中找到错误的 nmos 单元,鼠标左键点击选中,按 q 进 入编辑属性,点击 Parameter,将 width 改为 2u,OK。 [47]、此时 nmos 的沟道宽度已经改好,将 nmos 移动到合适的位置。 [48]、Save。关闭所有的窗口