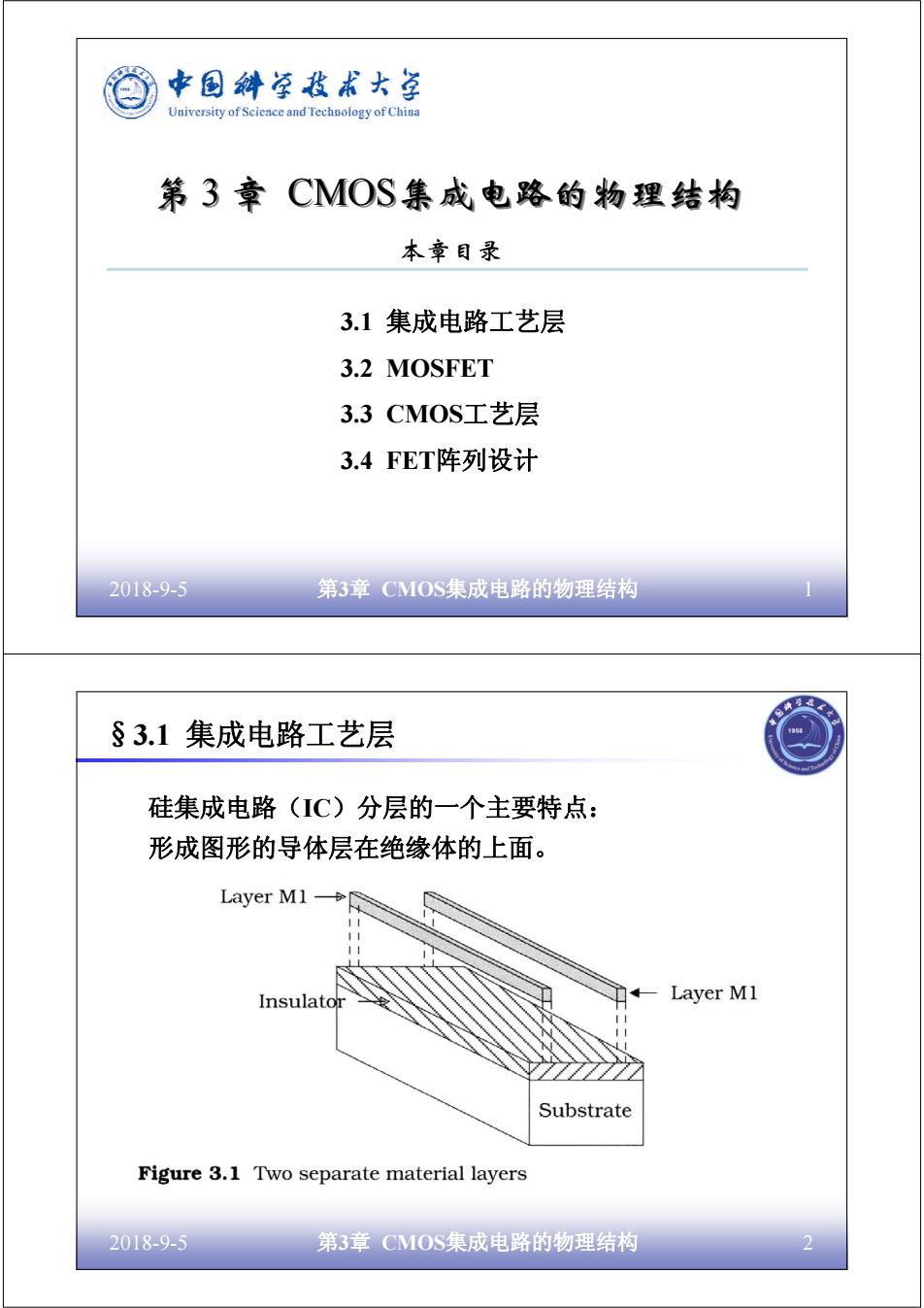

中国绅字我术大学 University of Science and Technology of China 第3章CMOS集成电路的物理结构 本章目录 3.1集成电路工艺层 3.2 MOSFET 3.3CMOS工艺层 3.4FET阵列设计 2018-9-5 第3章CMOS集成电路的物理结构 §3.1集成电路工艺层 硅集成电路(C)分层的一个主要特点: 形成图形的导体层在绝缘体的上面。 Layer M1- Insulator Layer M1 Substrate Figure 3.1 Two separate material layers 2018-9-5 第3章CMOS集成电路的物理结构

2018-9-5 第3章 CMOS集成电路的物理结构 1 第 3 章 CMOS集成电路的物理结构 集成电路的物理结构 本章目录 3.1 集成电路工艺层 3.2 MOSFET 3.3 CMOS工艺层 3.4 FET阵列设计 2018-9-5 第3章 CMOS集成电路的物理结构 2 §3.1 集成电路工艺层 硅集成电路(IC)分层的一个主要特点: 形成图形的导体层在绝缘体的上面

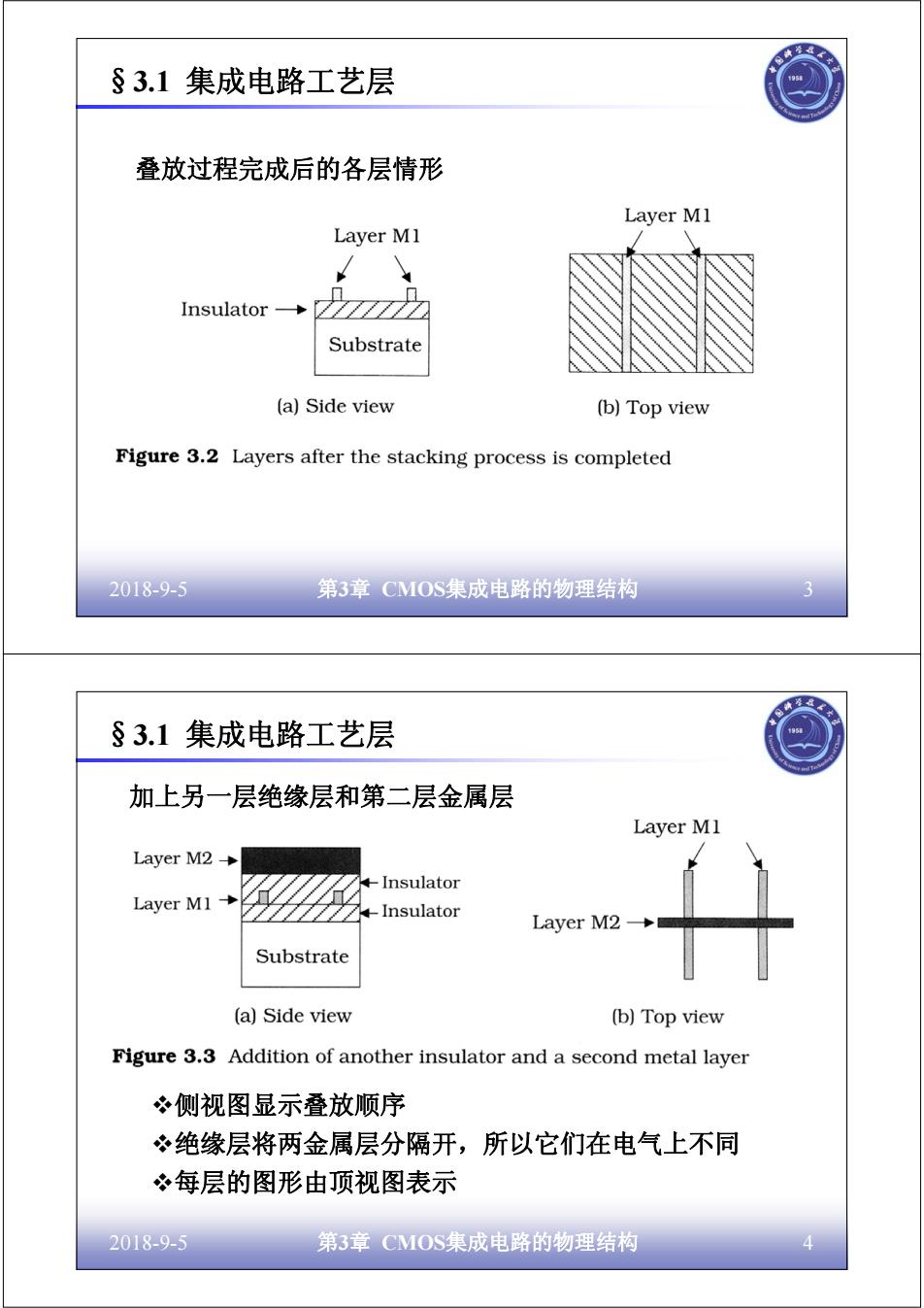

§3.1集成电路工艺层 叠放过程完成后的各层情形 Layer MI Layer MI Insulator+☑777 Substrate (a)Side view (b)Top view Figure 3.2 Layers after the stacking process is completed 2018-9-5 第3章CMOS集成电路的物理结构 §3.1集成电路工艺层 加上另一层绝缘层和第二层金属层 Layer MI Layer M2 +Insulator Layer MI Insulator Layer M2→■ Substrate (a)Side view (b)Top view Figure 3.3 Addition of another insulator and a second metal layer ?侧视图显示叠放顺序 冬绝缘层将两金属层分隔开,所以它们在电气上不同 冬每层的图形由顶视图表示 2018-9-5 第3章CMOS集成电路的物理结构

2018-9-5 第3章 CMOS集成电路的物理结构 3 叠放过程完成后的各层情形 §3.1 集成电路工艺层 2018-9-5 第3章 CMOS集成电路的物理结构 4 §3.1 集成电路工艺层 加上另一层绝缘层和第二层金属层 侧视图显示叠放顺序 绝缘层将两金属层分隔开,所以它们在电气上不同 每层的图形由顶视图表示

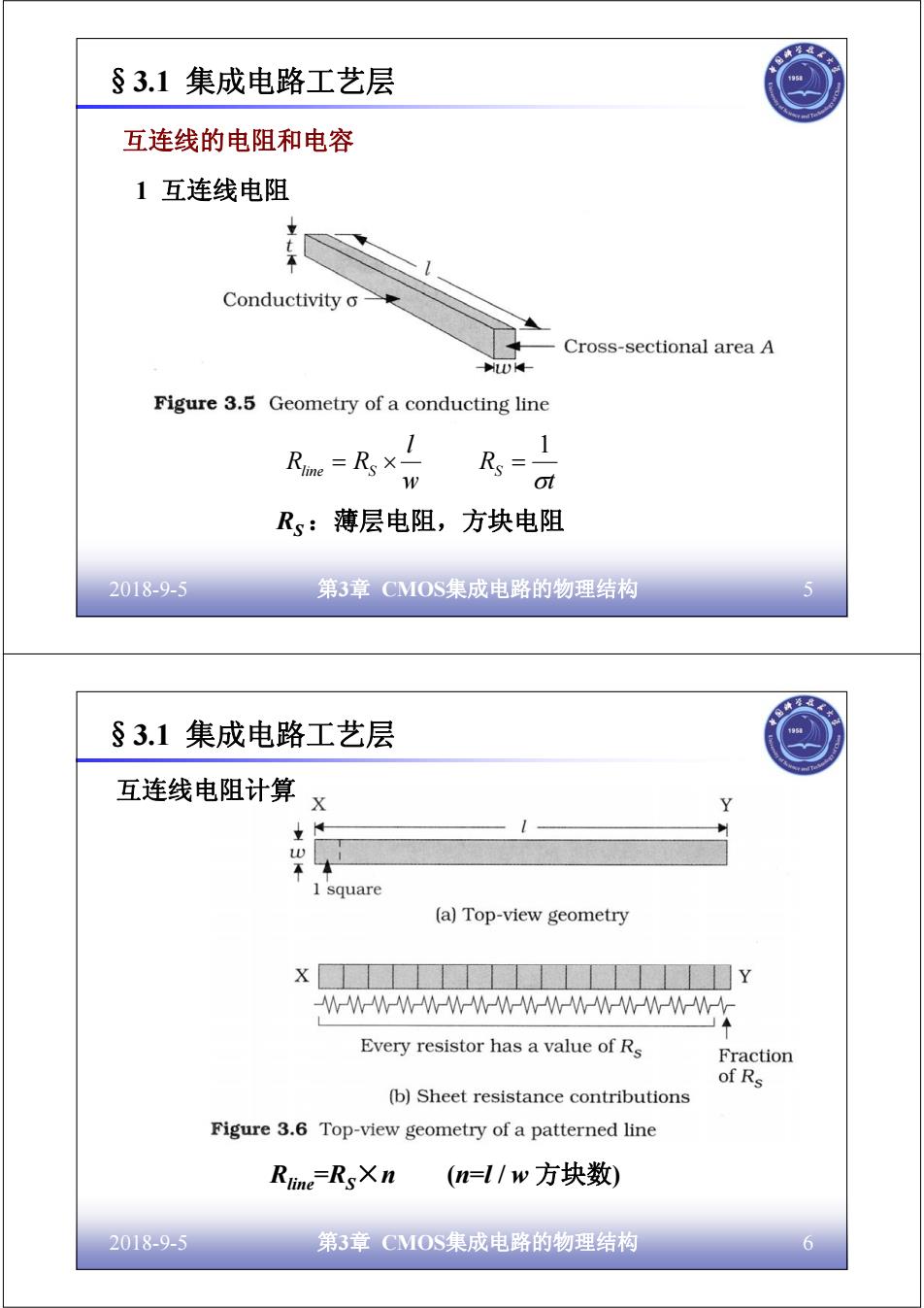

§3.1集成电路工艺层 互连线的电阻和电容 1互连线电阻 Conductivity o Cross-sectional area A WK- Figure 3.5 Geometry of a conducting line Rime =Rs x W ,- ot R:薄层电阻,方块电阻 2018-9-5 第3章CMOS集成电路的物理结构 §3.1集成电路工艺层 互连线电阻计算 X 1 square (a)Top-view geometry Y w-W-w----- Every resistor has a value of Rs Fraction of Rs (b)Sheet resistance contributions Figure 3.6 Top-view geometry of a patterned line Riine-RsXn (n=l/w方块数) 2018-9-5 第3章CMOS集成电路的物理结构 6

2018-9-5 第3章 CMOS集成电路的物理结构 5 §3.1 集成电路工艺层 互连线的电阻和电容 1 互连线电阻 w l Rline = RS × RS :薄层电阻,方块电阻 t RS σ 1 = 2018-9-5 第3章 CMOS集成电路的物理结构 6 §3.1 集成电路工艺层 互连线电阻计算 Rline=RS×n (n=l / w 方块数)

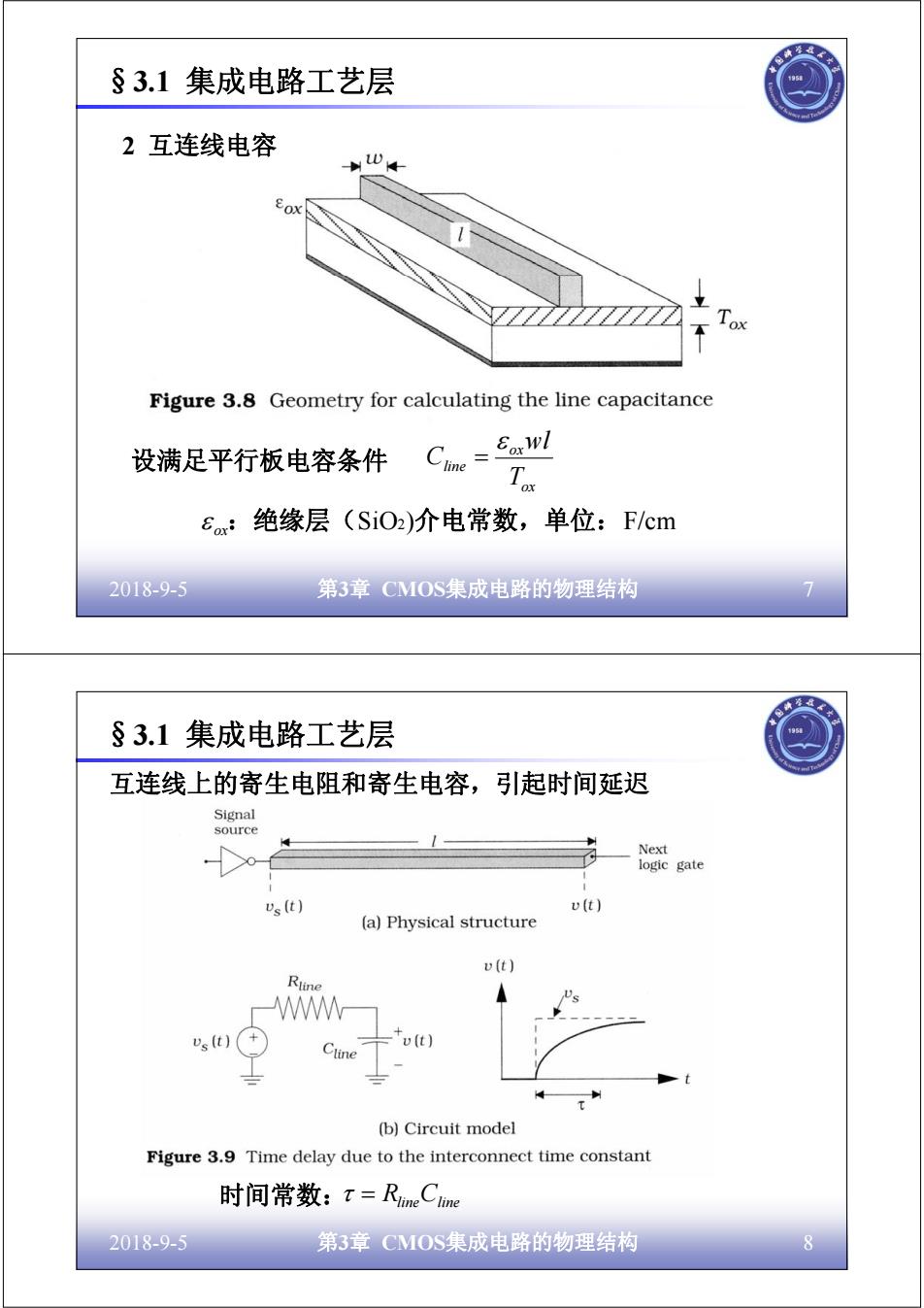

§3.1集成电路工艺层 2互连线电容 EOX o Figure 3.8 Geometry for calculating the line capacitance 设满足平行板电容条件 Ciae-£aswl &:绝缘层(SiO2)介电常数,单位:F/cm 2018-9-5 第3章CMOS集成电路的物理结构 §3.1集成电路工艺层 互连线上的寄生电阻和寄生电容,引起时间延迟 Signal source Next ● logic gate 's(t) v(t) (a)Physical structure v(t) vs(t) "v(t) (b)Circuit model Figure 3.9 Time delay due to the interconnect time constant 时间常数:T=RimneCuine 2018-9-5 第3章CMOS集成电路的物理结构 8

2018-9-5 第3章 CMOS集成电路的物理结构 7 §3.1 集成电路工艺层 2 互连线电容 设满足平行板电容条件 ox ox line T wl C ε = ε ox:绝缘层(SiO2)介电常数,单位:F/cm 2018-9-5 第3章 CMOS集成电路的物理结构 8 §3.1 集成电路工艺层 互连线上的寄生电阻和寄生电容,引起时间延迟 时间常数: = RlineCline τ

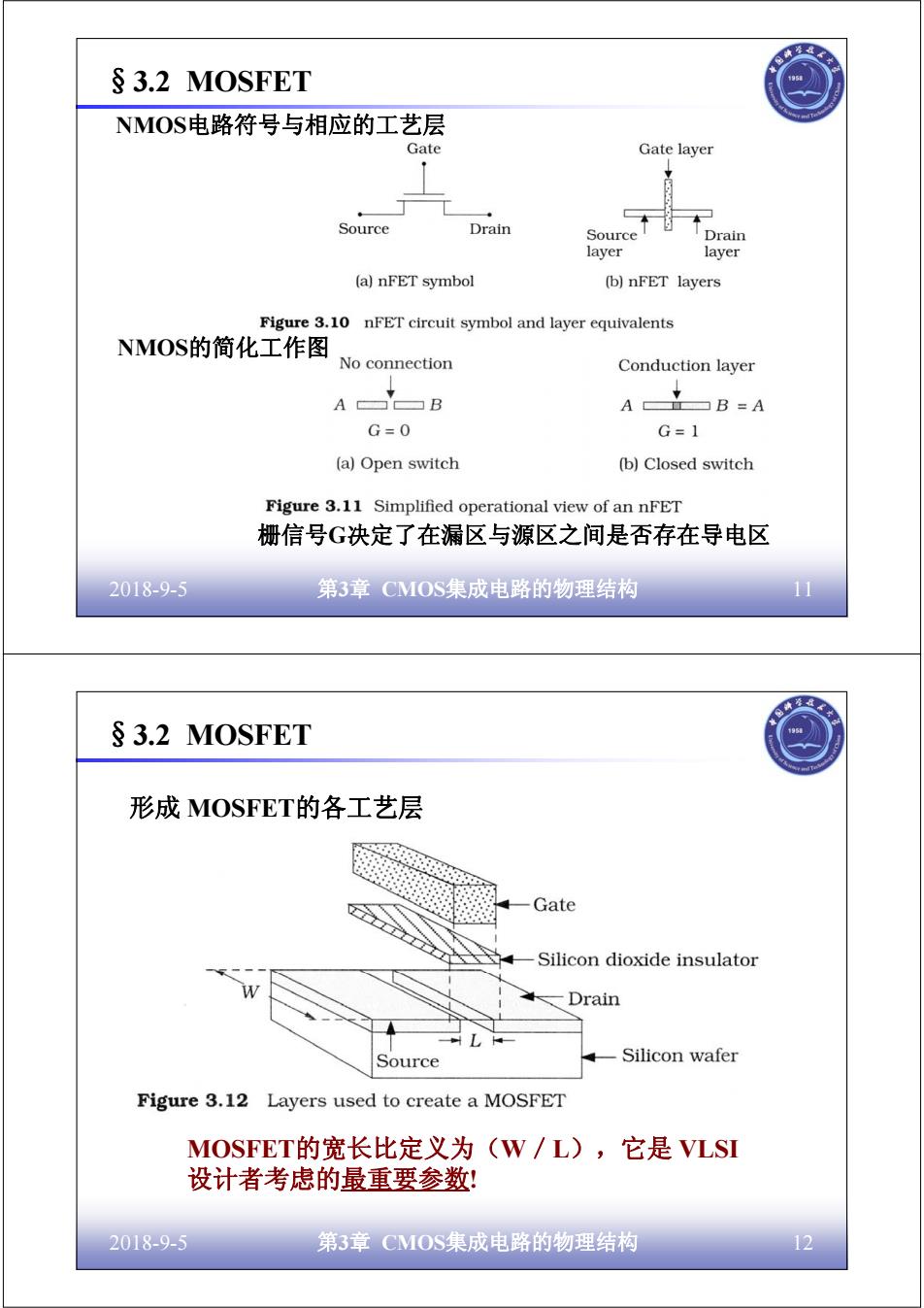

§3.1集成电路工艺层 互连线电阻和电容 >互连线电阻和电容使传播延时增加,相应于性能的下降 >互连线电阻会消耗功率 >互连线电容会引起额外的噪声,影响电路的可靠性 2018-9-5 第3章CMOS集成电路的物理结构 §3.1集成电路工艺层 Intel0.18um工艺互连线 Layer t(nm) w(nm) s(nm)AR 6 1720 860 860 2.0 1000 5 1600 800 800 2.0 1000 1080 540 540 2.0 图 700 3 700 320 320 2.2 图因 700 700 320 320 2.2 图因 700 480 250 250 1.9 g 800 Substrate 2018-9-5 第3章CMOS集成电路的物理结构 10

2018-9-5 第3章 CMOS集成电路的物理结构 9 §3.1 集成电路工艺层 ¾互连线电阻和电容使传播延时增加,相应于性能的下降 ¾互连线电阻会消耗功率 ¾互连线电容会引起额外的噪声,影响电路的可靠性 互连线电阻和电容 2018-9-5 第3章 CMOS集成电路的物理结构 10 §3.1 集成电路工艺层 Intel 0.18µm 工艺互连线

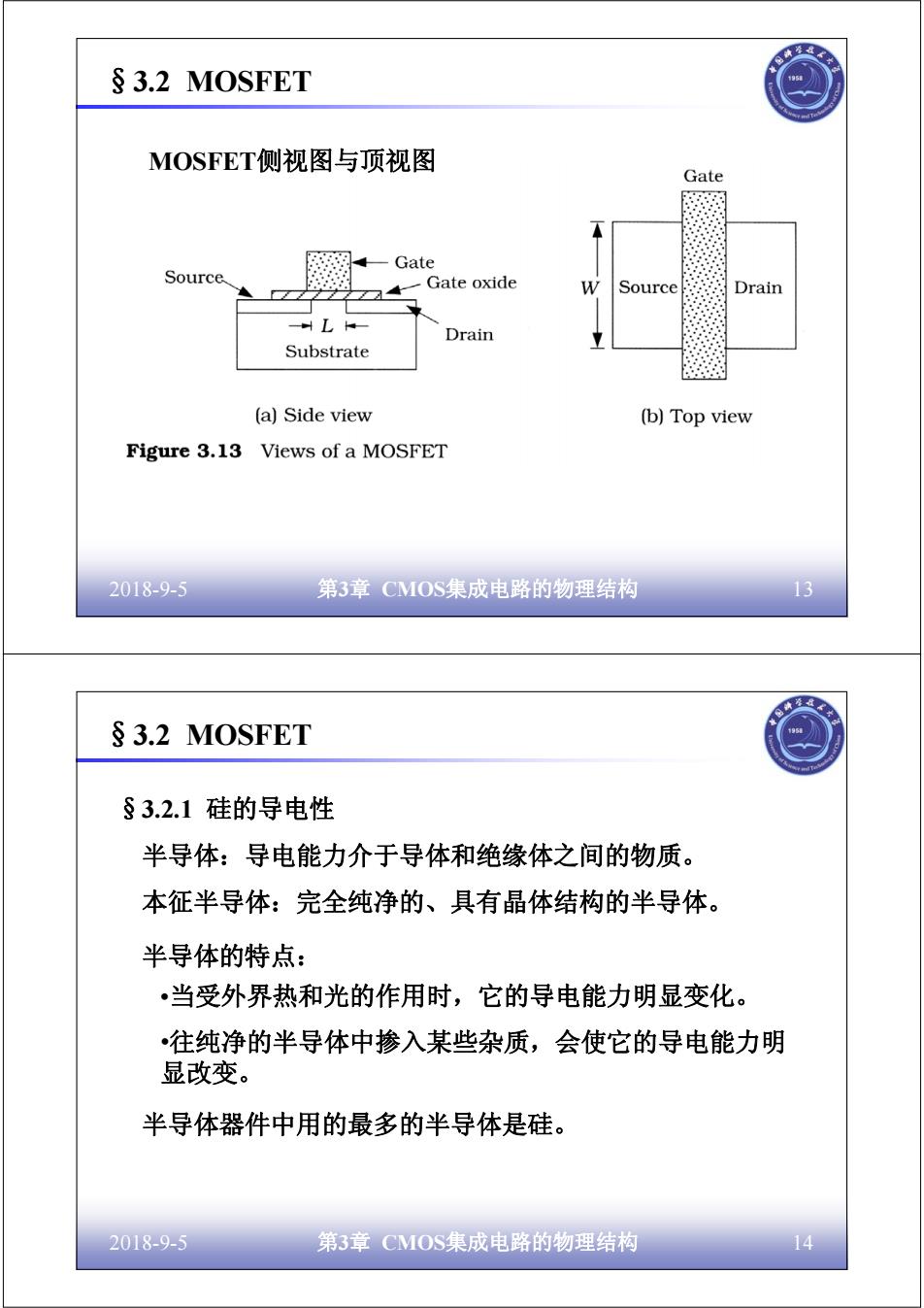

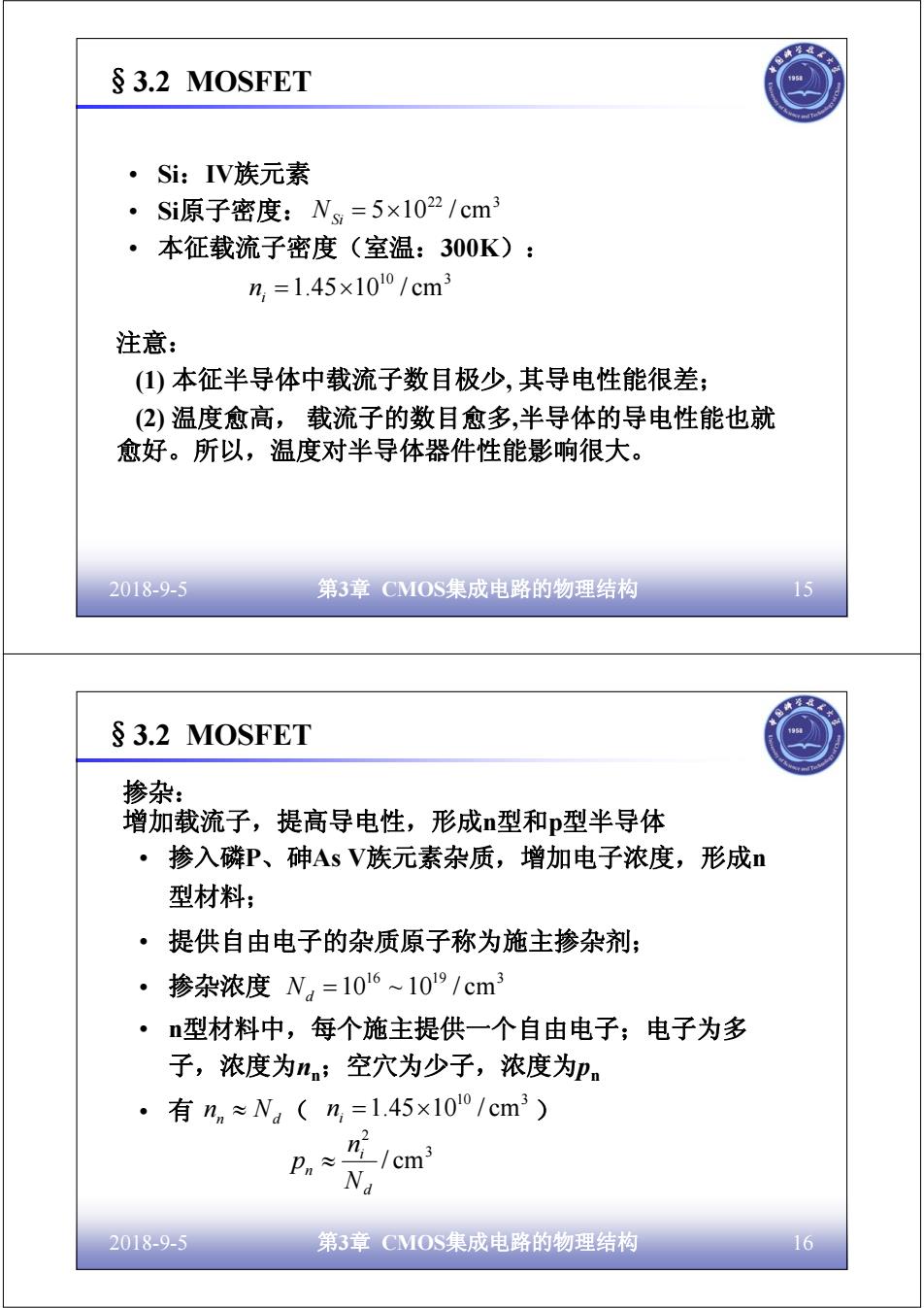

§3.2 MOSFET NMOS电路符号与相应的工艺层 Gate Gate layer Source Drain Source Drain layer layer (a)nFET symbol (b)nFET layers Figure 3.10 nFET circuit symbol and layer equivalents NMOS的简化工作图 No connection Conduction layer A☐B A☐B=A G=0 G=1 (a)Open switch (b)Closed switch Figure 3.11 Simplified operational view of an nFET 栅信号G决定了在漏区与源区之间是否存在导电区 2018-9-5 第3章CMOS集成电路的物理结构 §3.2 MOSFET 形成MOSFET的各工艺层 Gate 04 Silicon dioxide insulator Drain Source Silicon wafer Figure 3.12 Layers used to create a MOSFET MOSFET的宽长比定义为(W/L),它是VLSI 设计者考虑的最重要参数! 2018-9-5 第3章CMOS集成电路的物理结构 12

2018-9-5 第3章 CMOS集成电路的物理结构 11 §3.2 MOSFET NMOS电路符号与相应的工艺层 NMOS的简化工作图 栅信号G决定了在漏区与源区之间是否存在导电区 2018-9-5 第3章 CMOS集成电路的物理结构 12 §3.2 MOSFET 形成 MOSFET的各工艺层 MOSFET的宽长比定义为(W/L),它是 VLSI 设计者考虑的最重要参数!

§3.2 MOSFET MOSFET侧视图与顶视图 Gate Gate Source Gate oxide Source Drain L Drain Substrate (a)Side view (b)Top view Figure 3.13 Views of a MOSFET 2018-9-5 第3章CMOS集成电路的物理结构 3 §3.2 MOSFET §3.2.1硅的导电性 半导体:导电能力介于导体和绝缘体之间的物质。 本征半导体:完全纯净的、具有晶体结构的半导体。 半导体的特点: •当受外界热和光的作用时,它的导电能力明显变化。 •往纯净的半导体中掺入某些杂质,会使它的导电能力明 显改变。 半导体器件中用的最多的半导体是硅。 2018-9-5 第3章CMOS集成电路的物理结构 14

2018-9-5 第3章 CMOS集成电路的物理结构 13 §3.2 MOSFET MOSFET侧视图与顶视图 2018-9-5 第3章 CMOS集成电路的物理结构 14 §3.2 MOSFET §3.2.1 硅的导电性 半导体:导电能力介于导体和绝缘体之间的物质。 半导体的特点: •当受外界热和光的作用时,它的导电能力明显变化。 •往纯净的半导体中掺入某些杂质,会使它的导电能力明 显改变。 半导体器件中用的最多的半导体是硅。 本征半导体:完全纯净的、具有晶体结构的半导体

§3.2 MOSFET © Si:IV族元素 Si原子密度:N=5×1022/cm3 本征载流子密度(室温:300K): n,=1.45×1010/cm3 注意: (①)本征半导体中载流子数目极少,其导电性能很差; (2)温度愈高,载流子的数目愈多,半导体的导电性能也就 愈好。所以,温度对半导体器件性能影响很大。 2018-9-5 第3章CMOS集成电路的物理结构 15 §3.2 MOSFET 掺杂: 增加载流子,提高导电性,形成型和p型半导体 ·掺入磷P、砷AsV族元素杂质,增加电子浓度,形成和 型材料; 提供自由电子的杂质原子称为施主掺杂剂; ·掺杂浓度N,=1016~109/cm3 型材料中,每个施主提供一个自由电子;电子为多 子,浓度为n:空穴为少子,浓度为p。 ·有nn≈N.(n,=1.45×101°/cm3) , cm Na 2018-9-5 第3章CMOS集成电路的物理结构 16

2018-9-5 第3章 CMOS集成电路的物理结构 15 • Si:IV族元素 • Si原子密度: • 本征载流子密度(室温:300K): 22 3 NSi = 5×10 / cm 10 3 ni =1.45×10 / cm §3.2 MOSFET 注意: (1) 本征半导体中载流子数目极少, 其导电性能很差; (2) 温度愈高, 载流子的数目愈多,半导体的导电性能也就 愈好。所以,温度对半导体器件性能影响很大。 2018-9-5 第3章 CMOS集成电路的物理结构 16 掺杂: 增加载流子,提高导电性,形成n型和p型半导体 • 掺入磷P、砷As V族元素杂质,增加电子浓度,形成n 型材料; • 提供自由电子的杂质原子称为施主掺杂剂; • 掺杂浓度 • n型材料中,每个施主提供一个自由电子;电子为多 子,浓度为nn;空穴为少子,浓度为pn • 有( ) 3 2 / cm d i n N n p ≈ 10 3 ni =1.45×10 / cm 16 19 3 Nd =10 ~ 10 / cm nn ≈ Nd §3.2 MOSFET

§3.2 MOSFET 。 掺入硼BⅢ族元素,增加空穴,形成p型材料; 。 提供空穴的杂质原子称为受主掺杂剂; 掺杂浓度N。=104→10/cm3 。1 型材料中,每个受主提供一个空穴,空穴为多子, 浓度为pp;电子为少子,浓度为n。 并有Pp≈N。 np≈ N 2018-9-5 第3章CMOS集成电路的物理结构 §3.2 MOSFET 电导率σ 。 载流子密度为n和p的半导体区域电导率: =q(u n+upp) ·式中:"n和"p为电子和空穴迁移率,cmVs) 常温下本征硅: 4n=1360cm/(V.s) 'p=480cm/(V.s) 本征硅电导率ō≈4.27×10-6/2·cm) 本征硅电阻率p=1/o≈2.34×102cm ·N型材料:o≈q4nn ·P型材料:O≈q4pp 2018-9-5 第3章CMOS集成电路的物理结构 18

2018-9-5 第3章 CMOS集成电路的物理结构 17 • 掺入硼B III族元素,增加空穴,形成p型材料; • 提供空穴的杂质原子称为受主掺杂剂; • 掺杂浓度 • p型材料中,每个受主提供一个空穴,空穴为多子, 浓度为pp;电子为少子,浓度为np • 并有 14 19 3 Na =10 →10 / cm 3 2 / cm N n n a i p ≈ pp ≈ Na §3.2 MOSFET 2018-9-5 第3章 CMOS集成电路的物理结构 18 电导率σ • 载流子密度为n和p的半导体区域电导率: • 式中: 和 为电子和空穴迁移率, • 常温下本征硅: • 本征硅电导率 • 本征硅电阻率 • N型材料: • P型材料: q( n p) σ = μ n + μ p μ n μ p 1360cm /(V s) 2 = ⋅ μn 480cm /(V s) 2 = ⋅ μ p cm /(V s) 2 ⋅ 4.27 10 /( cm) 6 ≈ × Ω⋅ − σ 1/ 2.34 10 cm 5 ρ = σ ≈ × Ω⋅ σ ≈ qμ n n σ ≈ qμ p p §3.2 MOSFET

§3.2 MOSFET 例3.2:一个硼掺杂密度为1015cm3的p型硅掺杂样品, 其多子电荷载体为空穴,密度为 pp≈Na=l05cm3 则少子载体的电子密度为 N。 1.45×109s2.1x105cm3 1015 已知该样品的迁移率为 4n≈1350cm2/(V.s),4,≈450cm2/(V.s) 其电导率为。≈q4P。=1.6×10-19×450×105=0.072(Q·cm) 电阻率为 p=1=L=13.9Q·cm) 60.072 2018-9-5 第3章CMOS集成电路的物理结构 19 §3.2 MOSFET 迁移率与掺杂浓度的关系 4=41+ 室温下:电子4=92cm2/(V.s,42=1380cm2/(V.s), Ng=1.3×107/cm3,a=0.91 空穴4=47.7cm21(V.s,42=495cm2/(V.s), Nw=6.3×1016/cm3,a=0.76 结论:迁移率随掺杂浓度增加而降低! 2018-9-5 第3章CMOS集成电路的物理结构 20

2018-9-5 第3章 CMOS集成电路的物理结构 19 15 3 10 cm− 15 -3 p a p ≈ N = 10 cm 5 3 15 10 2 a 2 p 2.1 10 cm 10 (1.45 10 ) − ≈ × × ≈ = N n n i 1350cm /(V s), 450cm /(V s) 2 2 ≈ ⋅ ≈ ⋅ μn μ p 19 15 -1 p ≈ = 1.6×10 × 450×10 = 0.072(Ω⋅ cm) − σ qμ p p 13.9( cm) 0.072 1 1 = = = Ω ⋅ σ ρ 例3.2:一个硼掺杂密度为 的p型硅掺杂样品, 其多子电荷载体为空穴,密度为 则少子载体的电子密度为 已知该样品的迁移率为 其电导率为 电阻率为 §3.2 MOSFET 2018-9-5 第3章 CMOS集成电路的物理结构 20 迁移率与掺杂浓度的关系 α μ μ μ μ ⎟ ⎟ ⎠ ⎞ ⎜ ⎜ ⎝ ⎛ + − = + Nref N 1 2 1 1 () () 1.3 10 / cm , 0.91 92cm / V s , 1380cm / V s , 17 3 2 2 2 1 = × = = ⋅ = ⋅ α μ μ Nref () () 6.3 10 / cm , 0.76 47.7cm / V s , 495cm / V s , 16 3 2 2 2 1 = × = = ⋅ = ⋅ α μ μ Nref 室温下:电子 空穴 结论:迁移率随掺杂浓度增加而降低! §3.2 MOSFET