中国绅学我术大学 University of Science and Technology of China 第12章CMOS VLSI运算电路 本章目录 >12.1一位加法器电路 >12.2串行进位加法器 >12.3超前进位加法器 >12.4其他高速加法器 >12.5乘法器 >12.6小结 2018-9-5 第12章CMOS VLSI:运算电路 §12.1一位加法器电路 1 半加器的符号及真值表 y 0 0 0 0 C HA 0 1 0 1 1 0 1 个 0 1 S=x⊕y C=X·y 半加器的逻辑电路 另外两种半加器的逻辑电路 C● (a)NAND2 logic (b)NOR-based network 2018-9-5 第12章CMOS VLSI运算电路 2

2018-9-5 第12章 CMOS VLSI运算电路 1 第 12 章 CMOS VLSI CMOS VLSI运算电路 本章目录 ¾12.1 一位加法器电路 ¾12.2 串行进位加法器 ¾12.3 超前进位加法器 ¾12.4 其他高速加法器 ¾12.5 乘法器 ¾12.6 小结 2018-9-5 第12章 CMOS VLSI运算电路 2 1 半加器的符号及真值表 s = x ⊕ y c = x ⋅ y §12.1 一位加法器电路 半加器的逻辑电路 另外两种半加器的逻辑电路

§12.1一位加法器电路 2全加器的符号及真值表 ai bi ci si Ci+l ai bi 0 0 0 0 0 0 1 0 0 FA 1 0 0 1 0 C+1 +) Ci 1 1 0 0 1 0 0 1 1 0 1 1 0 1 1 0 1 0 1 1 Figure 12.4 Full-adder symbol and function table C+1=a,·b+C·(a,©b) =ab,+c,(a,+b) S=a,⊕b⊕C =a,b,c,+C+(a,+b,+c) 2018-9-5 第12章CMOS VLSI运算电路 §12.1一位加法器电路 (1)AOI实现的全加器逻辑电路 C+1=a·b,+C,·(a,+b) s,=ab,C,+C4(a,+b,+c) ai bi ci Figure 12.7 AOI full-adder logic 2018-9-5 第12章CMOS VLSI运算电路

2018-9-5 第12章 CMOS VLSI运算电路 3 §12.1 一位加法器电路 2 全加器的符号及真值表 ( ) ( ) i i i i i i i i i i i a b c a b c a b c a b = ⋅ + ⋅ + + = ⋅ + ⋅ ⊕ 1 ( ) i i i i i i i i i i i a b c c a b c s a b c = + + + = ⊕ ⊕ +1 2018-9-5 第12章 CMOS VLSI运算电路 4 §12.1 一位加法器电路 (1) AOI实现的全加器逻辑电路 ( ) i i i i i i c = a ⋅b + c ⋅ a + b +1 ( ) i i i i i i i i s = a ⋅b ⋅c + c ⋅ a + b + c +1

§12.1一位加法器电路 © 进位输出电路的改进 VpD b.bi b.ai b.bi Cid c+1 Ct and ai b a bi (a)Standard nFET logic (b)Mirror circuit Figure 12.8 Evolution of carry-out circuit 2018-9-5 第12章CMOS VLSI:运算电路 §12.1一位加法器电路 镜像AOI实现的CMOS全加器 VDD bi ci Ci+l+ ci Figure 12.9 Mirror AOI CMOS full-adder 2018-9-5 第12章CMOS VLSI运算电路 6

2018-9-5 第12章 CMOS VLSI运算电路 5 §12.1 一位加法器电路 进位输出电路的改进 2018-9-5 第12章 CMOS VLSI运算电路 6 §12.1 一位加法器电路 镜像AOI实现的CMOS全加器 ?

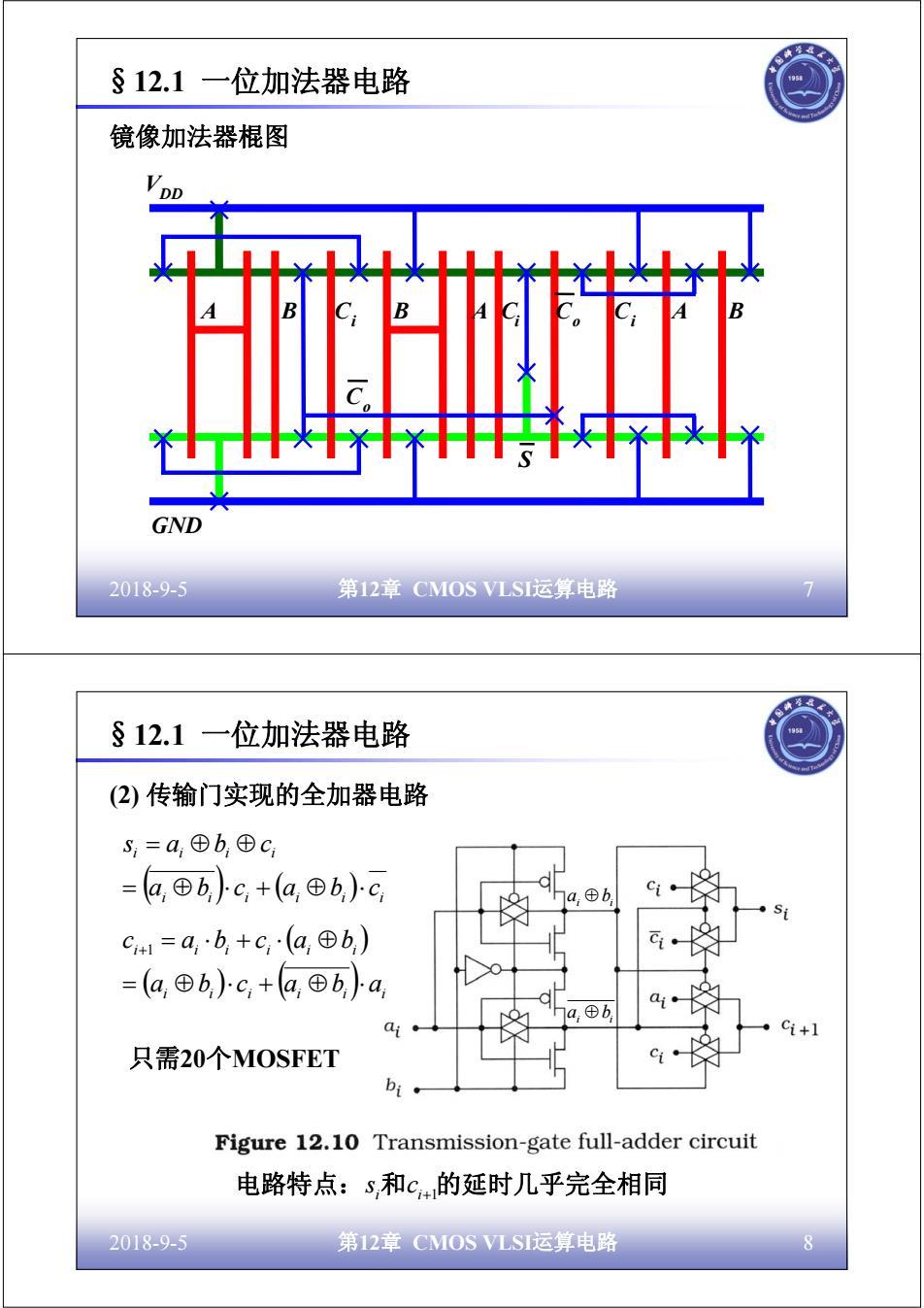

§12.1一位加法器电路 镜像加法器棍图 DD GND 2018-9-5 第12章CMOS VLSI:运算电路 §12.1一位加法器电路 (2)传输门实现的全加器电路 S,=a,田b,⊕C =a,田b)c,+(a,⊕b,)c 7a⊕b ci c=ab,+C,(a,⊕b,) =(a,©b,)c,+a,田b,a a 1a⊕b ai Ci+l 只需20个MOSFET bi Figure 12.10 Transmission-gate full-adder circuit 电路特点:s和c的延时几乎完全相同 2018-9-5 第12章CMOS VLSI运算电路 8

2018-9-5 第12章 CMOS VLSI运算电路 7 镜像加法器棍图 Ci A B VDD GND B C o A Ci C o Ci A B S §12.1 一位加法器电路 2018-9-5 第12章 CMOS VLSI运算电路 8 §12.1 一位加法器电路 (2) 传输门实现的全加器电路 电路特点:si 和ci+1 的延时几乎完全相同 ( ) ( ) ( ) i i i i i i i i i i i i a b c a b a c a b c a b = ⊕ ⋅ + ⊕ ⋅ +1 = ⋅ + ⋅ ⊕ ( ) ( ) i i i i i i i i i i a b c a b c s a b c = ⊕ ⋅ + ⊕ ⋅ = ⊕ ⊕ 只需20个MOSFET ai ⊕bi i i a ⊕b

§12.1一位加法器电路 (3)双轨互补传输管逻辑(CPL)全加器设计 bibi by bu ai cici ai ai cici a 1111 1111 111 bi ab+bc ab+bc XOR/XNOR a b bc+ab bc +ab .bi a XOR/XNOR Ci a C+1 Cu+l (a)2-input array (b)Sum circuit (c)Carry circuit Figure 12.5 CPL full-adder design s,=a,⊕b,⊕c,=a,⊕bc,+(a,⊕b,)c C+1=ab,+C,:(a,⊕b) 2018-9-5 第12章CMOS VLSI:运算电路 §12.2串行进位加法器 4位串行进位加法器 bs as b2 a2 bl al bo ao CA S3 S2 S1 So Figure 12.12 A 4-bit ripple-carry adder 2018-9-5 第12章CMOS VLSI运算电路 10

2018-9-5 第12章 CMOS VLSI运算电路 9 §12.1 一位加法器电路 (3) 双轨互补传输管逻辑(CPL)全加器设计 ( ) ( ) ( ) i i i i i i i i i i i i i i i i c a b c a b s a b c a b c a b c = ⋅ + ⋅ ⊕ = ⊕ ⊕ = ⊕ ⋅ + ⊕ ⋅ +1 i i i i i i i i b c a b a b b c + + i i i i i i i i b c a b a b b c + + 2018-9-5 第12章 CMOS VLSI运算电路 10 §12.2 串行进位加法器 4位串行进位加法器

§12.2串行进位加法器 通过4位串行加法器最坏情形下的延迟 ba as b2 a2 bi al bo ao Co + CA S2 Figure 12.13 Worst-case delay through the 4-bit ripple adder tab =ta3+ta2 +tan+tdo t4b=ta(cn→S3)+2t(cm→com)+ta(ao,b。→C) 推广: tn-bm=ta(cm→Sn-i)+(n-2t(cm→com)+ta(ao,b。-→c) 2018-9-5 第12章CMOS VLSI运算电路 §12.3超前进位加法器 超前进位算法的基础 ai bi 9i Pi ai bi a⊕bi 9:=1 a=b1=0 0 0 C+1 a1=b1=1 1 0 p=1 a1≠b 0 C+1=a·b1+C(a⊕b) Figure 12.15 Basis of the carry look-ahead algorithm C+1=a,b,+c(a,⊕b,) S,=a,田b®c 进位产生信号:g,=a·b 进位传播信号:p,=a⊕b, C+1=8,+p,CS,=p,田c 2018-9-5 第12章CMOS VLSI运算电路 12

2018-9-5 第12章 CMOS VLSI运算电路 11 ( ) ( )( ) 4 3 0 0 1 4 3 2 1 0 t t c s 2t c c t a ,b c t t t t t b d in d in out d b d d d d = → + → + → = + + + §12.2 串行进位加法器 通过4位串行加法器最坏情形下的延迟 ( ) ( )( ) ( ) 1 0 0 1 t t c s n 2 t c c t a ,b c n−bit = d in → n− + − d in → out + d → 推广: 2018-9-5 第12章 CMOS VLSI运算电路 12 ( ) i i i i ai bi c +1 = a ⋅b + c ⋅ ⊕ §12.3 超前进位加法器 超前进位算法的基础 i i i i i i p a b g a b = ⊕ = ⋅ 进位传播信号: 进位产生信号: i i i i i i i c = g + p ⋅c s = p ⊕c + 1 i i i i s = a ⊕b ⊕ c

§12.3超前进位加法器 超前进位算法的基础 Ci+1=8,+P,C S,=P©c C1=8o+Po·Co C2=81+p1·C1 C3=82+P2·C2 C4=83+P3·C3 C2=81+P1(8o+P0Co)=81+P18o+p1·poCo C3=82+P2(81+P180+p1·poCo) =82+P281+P2'P‘8o+P2P1'PoCo C4=83+P3(82+P2'81+P2P18o+P2p1PoCo) =83+P3·82+P3'P281+P3P2P18o+P3·P2P1P0Co 2018-9-5 第12章CMOS VLSI:运算电路 13 §12.3超前进位加法器 4位CLA进位的逻辑电路 用CLA进位电路计算和 co Po S,=p,⊕C 90* co Po ● co 50 90 Po 91 P P1 S1 91 CLA Network C2 2, 92 S2 P3 93 53 P3 93 2018-9-5 第12章CMOS VLSI运算电路 14

2018-9-5 第12章 CMOS VLSI运算电路 13 §12.3 超前进位加法器 超前进位算法的基础 3 2 2 2 4 3 3 3 1 0 0 0 2 1 1 1 c g p c c g p c c g p c c g p c = + ⋅ = + ⋅ = + ⋅ = + ⋅ 2 1 1 0 0 0 1 1 0 1 0 0 c = g + p ⋅(g + p ⋅c ) = g + p ⋅ g + p ⋅ p ⋅c 2 2 1 2 1 0 2 1 0 0 3 2 2 1 1 0 1 0 0 ( ) g p g p p g p p p c c g p g p g p p c = + ⋅ + ⋅ ⋅ + ⋅ ⋅ ⋅ = + ⋅ + ⋅ + ⋅ ⋅ 3 3 2 3 2 1 3 2 1 0 3 2 1 0 0 4 3 3 2 2 1 2 1 0 2 1 0 0 ( ) g p g p p g p p p g p p p p c c g p g p g p p g p p p c = + ⋅ + ⋅ ⋅ + ⋅ ⋅ ⋅ + ⋅ ⋅ ⋅ ⋅ = + ⋅ + ⋅ + ⋅ ⋅ + ⋅ ⋅ ⋅ i i i i i i i c = g + p ⋅c s = p ⊕c + 1 2018-9-5 第12章 CMOS VLSI运算电路 14 §12.3 超前进位加法器 4位CLA进位的逻辑电路 用CLA进位电路计算和 i i i s = p ⊕ c

§12.3超前进位加法器 实现CLA各项 进位的nFET Po 逻辑阵列 (a)cI logic (b)cologic c4 P3 P2+ 1- 9091293 (c)calogic (d)c4logic Figure 12.18 nFET logic arrays for the CLA terms 2018-9-5 第12章CMOS VLSI:运算电路 15 §12.3 超前进位加法器 可能采用的三种电路 VpD VpD d VpD ·O/pFET logic nFET logic nFET nFET logic logic (a)Complementary (b)Pseudo nMOS (c)Dynamic Figure 12.19 Possible uses of the nFET logic arrays in Figure 12.18 2018-9-5 第12章CMOS VLSI运算电路 16

2018-9-5 第12章 CMOS VLSI运算电路 15 §12.3 超前进位加法器 实现CLA各项 进位的nFET 逻辑阵列 2018-9-5 第12章 CMOS VLSI运算电路 16 §12.3 超前进位加法器 可能采用的三种电路

§12.3超前进位加法器 静态CLA镜像电路 VpD VpD Po b.co 9o+-d ·90 ·g0 (a)Series-parallel circuit (b)Mirror equivalent Figure 12.20 Static CLA mirror circuit C1=80+P0·Co 2018-9-5 第12章CMOS VLSI:运算电路 §12.3超前进位加法器 VDD 产生c,的静态镜像电路 g1 co+dl ·C2 ·g0 Figure 12.21 Static mirror circuit for c2 C1=80+P0C0 C2=81+P91=81+p(g0+p0c) 2018-9-5 第12章CMOS VLSI运算电路 18

2018-9-5 第12章 CMOS VLSI运算电路 17 1 0 0 0 c = g + p ⋅c §12.3 超前进位加法器 静态CLA镜像电路 2018-9-5 第12章 CMOS VLSI运算电路 18 ( ) 2 1 1 1 1 1 0 0 0 1 0 0 0 c g p c g p g p c c g p c = + ⋅ = + + ⋅ = + ⋅ §12.3 超前进位加法器 产生c2 的静态镜像电路

§12.3超前进位加法器 MODL进位电路 Precharge pFETs VpD 0一c4 P3· 0一c3 P2- 0一2 0一c1 90g192门93 Co+ 0。 Figure 12.22 MODL carry circuit 2018-9-5 第12章CMOS VLSI:运算电路 19 §12.3超前进位加法器 12.3.1曼彻斯特进位链 C+1=8i+P,C1 a b P gi k 0 0 0 1 0 1 1 0 0 1 0 1 0 0 1 1 0 0 Figure 12.23 Propagate.generate,and carry-kill values 进位产生信号:g,=a,b, 进位传播信号:p,=a,⊕b, 进位清除信号:k,=a,+b=a·, 2018-9-5 第12章CMOS VLSI运算电路 20

2018-9-5 第12章 CMOS VLSI运算电路 19 §12.3 超前进位加法器 MODL进位电路 2018-9-5 第12章 CMOS VLSI运算电路 20 §12.3 超前进位加法器 12.3.1 曼彻斯特进位链 i i i i i i p a b g a b = ⊕ = ⋅ 进位传播信号: 进位产生信号: i i i i i 进位清除信号:k = a + b = a ⋅b i i i i c = g + p ⋅c +1