中国绅学我术大学 University of Science and Technology of China 第六章附序逻辑电路 本章目录 >6.1概述 >6.2时序逻辑电路的分析方法 >6.3若干常用的时序逻辑电路 >6.4时序逻辑电路的设计方法 >6.5用可编程逻辑器件实现同步时序逻辑电路 >6.6时序逻辑电路中的竞争一冒险现象 2017-8-4 第六章时序逻辑电路 §6.1概述 一、时序逻辑电路的特点 1逻辑功能特点:任一时刻的输出不仅取决于该时刻的输入, 还与电路原来的状态有关。 2电路结构特点: 例:串行加法器,两个多位数从低位到高位逐位相加 ai (1)通常包含组合电路和存储电路两 b Ci-l CI 个部分,存储电路是必不可少的。 (2)存储电路的输出状态必须反馈到 CLK 组合电路的输入端,与输入信号共同 决定组合逻辑电路的输出。 2017-8-4 第六章时序逻辑电路

2017-8-4 第六章 时序逻辑电路 1 第六章 时序逻辑电路 第六章 时序逻辑电路 本章目录 ¾6.1 概述 ¾6.2 时序逻辑电路的分析方法 ¾6.3 若干常用的时序逻辑电路 ¾6.4 时序逻辑电路的设计方法 ¾6.5 用可编程逻辑器件实现同步时序逻辑电路 ¾6.6 时序逻辑电路中的竞争-冒险现象 2017-8-4 第六章 时序逻辑电路 2 §6.1 概述 一、时序逻辑电路的特点 1 逻辑功能特点:任一时刻的输出不仅取决于该时刻的输入, 还与电路原来的状态有关。 2 电路结构特点: 例:串行加法器,两个多位数从低位到高位逐位相加 (1)通常包含组合电路和存储电路两 个部分,存储电路是必不可少的。 (2)存储电路的输出状态必须反馈到 组合电路的输入端,与输入信号共同 决定组合逻辑电路的输出

§6.1概述 二、时序逻辑电路的一般结构与功能描述方法 1时序逻辑电路的结构框图 组合逻辑电路 y 91 存储电路 9, 输入变量:X(x,x2,…,x)方输出变量:Y(y,2,,y方 存储电路的输入信号:Z(31,22,…,)方 存储电路的输出信号:Q(q1,92,…,91) 2017-8-4 第六章时序逻辑电路 §6.1概述 2时序逻辑电路的功能描述(可用三个方程组来描述) y=f(x1,x2,…,x1,91,92,,91) →输出方程Y=F[X,Q] y,=∫(x,x2,,x,91,92,,9) 21=81(X1,X2,…,x,91,92,,9) →驱动方程Z=G[X,Q] 2k=8k(x1,X2,,x1,91,92,…,9) q41=h(31,32,…,21,91,92,…,91) →状态方程Q*=H[Z,Q] 91=h(31,22,…,21,91,92,…,91) 2017-8-4 第六章时序逻辑电路

2017-8-4 第六章 时序逻辑电路 3 二、时序逻辑电路的一般结构与功能描述方法 1 时序逻辑电路的结构框图 ( , , , ) ( , , , ) ( , , , ) ( , , , ) 1 2 1 2 1 2 1 2 l k i j Q q q q Z z z z X x x x Y y y y L L L L 存储电路的输出信号: 存储电路的输入信号: ; 输入变量: ;输出变量: ; §6.1 概述 2017-8-4 第六章 时序逻辑电路 4 2 时序逻辑电路的功能描述(可用三个方程组来描述) [ , ] ( , , , , , , , ) ( , , , , , , , ) 1 2 1 2 1 1 1 2 1 2 Y F X Q y f x x x q q q y f x x x q q q j j i l i l ⇒ = ⎪ ⎩ ⎪ ⎨ ⎧ = = 输出方程 L L M L L [ , ] ( , , , , , , , ) ( , , , , , , , ) 1 2 1 2 1 1 1 2 1 2 Z G X Q z g x x x q q q z g x x x q q q k k i l i l ⇒ = ⎪ ⎩ ⎪ ⎨ ⎧ = = 驱动方程 L L M L L * [ , ] ( , , , , , , , ) ( , , , , , , , ) 1 2 1 2 * 1 1 2 1 2 * 1 Q H Z Q q h z z z q q q q h z z z q q q l l i l i l ⇒ = ⎪ ⎩ ⎪ ⎨ ⎧ = = 状态方程 L L M L L §6.1 概述

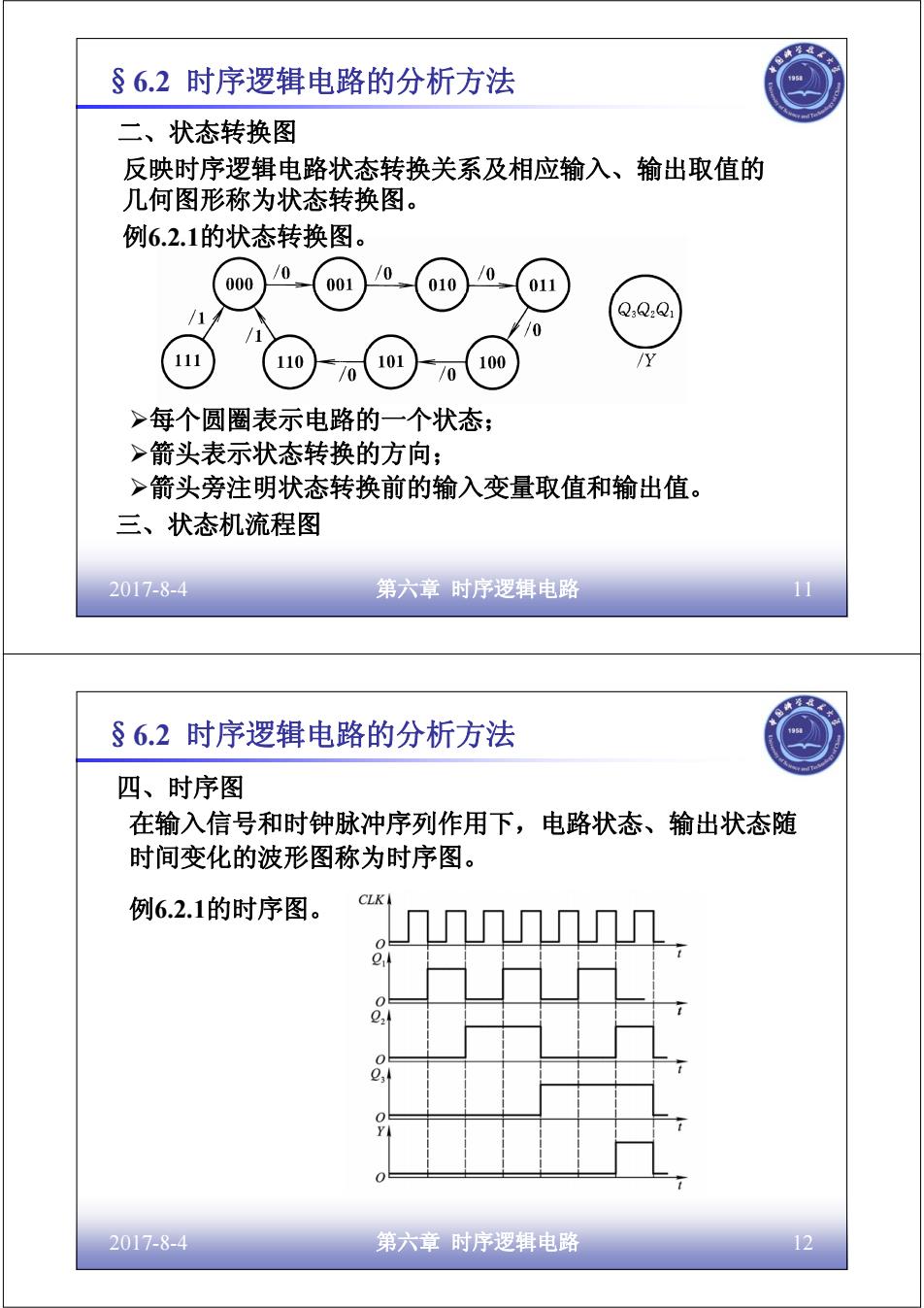

§6.1概述 三、时序逻辑电路的分类 1根据存储电路的动作特点分类: 同步时序电路:所有触发器状态的变化都是在同一时钟信号 控制下同时发生的。 异步时序电路:触发器状态的变化不是同时发生的。 2根据输出信号特点分类: 米利(Meay)型电路:输出信号不仅取决于存储电路的状态, 还取决于输入变量。 穆尔(Moore)型电路:输出信号仅取决于存储电路的状态。 注:时序电路工作时是在电路的有限个状态间按一定规律转换 的,所以又将时序电路称为状态机。 2017-8-4 第六章时序逻辑电路 §6.2时序逻辑电路的分析方法 6.2.1同步时序逻辑电路的分析方法 分析:找出给定时序电路的逻辑功能。 分析同步时序逻辑电路的一般步骤: (1)从给定的逻辑图中写出每个触发器的驱动方程; (2)将驱动方程代入相应触发器的特性方程,得到状态 方程; (3)根据逻辑图写出电路的输出方程。 2017-8-4 第六章时序逻辑电路

2017-8-4 第六章 时序逻辑电路 5 三、时序逻辑电路的分类 1 根据存储电路的动作特点分类: 同步时序电路:所有触发器状态的变化都是在同一时钟信号 控制下同时发生的。 异步时序电路:触发器状态的变化不是同时发生的。 2 根据输出信号特点分类: 米利(Mealy)型电路:输出信号不仅取决于存储电路的状态, 还取决于输入变量。 穆尔(Moore)型电路:输出信号仅取决于存储电路的状态。 注:时序电路工作时是在电路的有限个状态间按一定规律转换 的,所以又将时序电路称为状态机。 §6.1 概述 2017-8-4 第六章 时序逻辑电路 6 §6.2 时序逻辑电路的分析方法 6.2.1 同步时序逻辑电路的分析方法 分析:找出给定时序电路的逻辑功能。 分析同步时序逻辑电路的一般步骤: (1)从给定的逻辑图中写出每个触发器的驱动方程; (2)将驱动方程代入相应触发器的特性方程,得到状态 方程; (3)根据逻辑图写出电路的输出方程

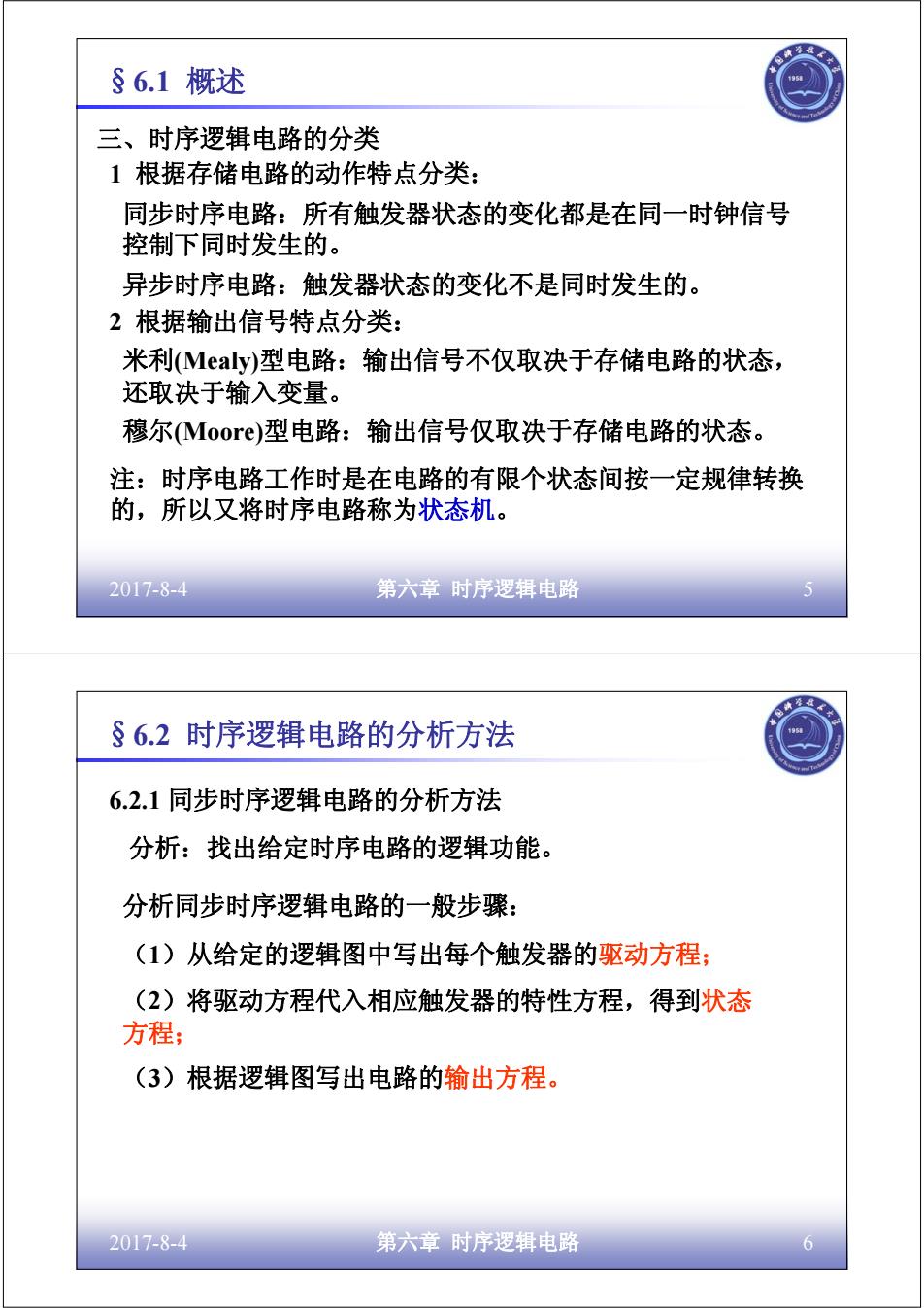

§6.2时序逻辑电路的分析方法 例6.2.1分析图示时序逻辑电路的逻辑功能,写出它的驱动方 程、状态方程和输出方程。FF、FF,和FF,是三个主从结构的 TTL触发器,下降沿动作,输入端悬空时和逻辑1等效。 1K7 FF FF. FF CLK 2017-8-4 第六章时序逻辑电路 §6.2时序逻辑电路的分析方法 0 1K7 FF, FF, CLK 1写出驱动方程: 2.代入JK触发器的特性方程 J1=(9223), K=1 Q*=JQ'+KQ,得状态方程: J2=Q, K2=(gO)1 Q*=(932)'·Q J3=Q02, K,=Q2 92*=9Q2+Q00 Q3*=QQ2Q3+Q30 3.写出输出方程:Y=Q2Q3 2017-8-4 第六章时序逻辑电路 8

2017-8-4 第六章 时序逻辑电路 7 §6.2 时序逻辑电路的分析方法 例6.2.1 分析图示时序逻辑电路的逻辑功能,写出它的驱动方 程、状态方程和输出方程。FF1、FF2和FF3是三个主从结构的 TTL触发器,下降沿动作,输入端悬空时和逻辑1等效。 2017-8-4 第六章 时序逻辑电路 8 §6.2 时序逻辑电路的分析方法 1.写出驱动方程: ⎪ ⎩ ⎪ ⎨ ⎧ = = = = ′ ′ ′ = ′ = 3 1 2 3 2 2 1 2 1 3 1 2 3 1 , , ( ) ( ) , 1 J Q Q K Q J Q K Q Q J Q Q K ,得状态方程: 代入 触发器的特性方程 Q JQ K Q JK * = ′ + ′ 2. ⎪ ⎩ ⎪ ⎨ ⎧ = ′ + ′ = ′ + ′ ′ = ′⋅ ′ 3 1 2 3 2 3 2 1 2 1 3 2 1 2 3 1 * * * ( ) Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q 2 3 3.写出输出方程:Y = Q Q

§6.2时序逻辑电路的分析方法 6.2.2时序逻辑电路的状态转换表、状态转换图、状态机流程图 和时序图 1状态转换表 反映时序逻辑电路的输出、次态和输入、现态间对应取值 关系的表格称为状态转换表。 逻辑方程组转换为状态转换表的步骤: (1)将任何一组输入及电路初态代入状态方程和输出方程, 算出电路的次态和现态下的输出; (2)以次态作为新的初态,和这时的输入再代入状态方程和 输出方程,又得到新的次态和输出; (3)继续上述过程,直至状态出现循环; (4)将全部计算结果列成真值表。 2017-8-4 第六章时序逻辑电路 §6.2 时序逻辑电路的分析方法 例6.2.2试列出例6.2.1电路的状态转换表。 9*=(Q223)'21 状态方程: Q2*=Q23+QQ22 Q*=Q92Q3+Q3Q3 状态转换表的另一种形式 输出方程:Y=Q2Q CLK 23 22 21 状态转换表 0 0 0 0 0 2322 21 23* 02* 21*Y 0 0 1 0 000 0 0 1 0 2 0 1 0 0 001 0 1 0 0 3 0 1 0 0 10 0 1 1 0 4 0 0 0 01 1 1 0 00 5 1 0 1 0 100 1 0 1 0 6 1 1 0 1 101 1 0 0 7 0 0 0 0 110 0 0 01 0 1 1 1 1 1 1 0 0 0 1 1 0 0 00 2017-8-4 第六章时序逻辑电路 10

2017-8-4 第六章 时序逻辑电路 9 6.2.2 时序逻辑电路的状态转换表、状态转换图、状态机流程图 和时序图 1 状态转换表 (1)将任何一组输入及电路初态代入状态方程和输出方程, 算出电路的次态和现态下的输出; (2)以次态作为新的初态,和这时的输入再代入状态方程和 输出方程,又得到新的次态和输出; (3)继续上述过程,直至状态出现循环; (4)将全部计算结果列成真值表。 逻辑方程组转换为状态转换表的步骤: §6.2 时序逻辑电路的分析方法 反映时序逻辑电路的输出、次态和输入、现态间对应取值 关系的表格称为状态转换表。 2017-8-4 第六章 时序逻辑电路 10 1 1 1 0 0 0 1 1 1 0 0 0 0 1 1 0 1 1 1 0 0 1 0 0 1 0 1 0 0 1 1 1 0 0 0 0 1 0 0 1 1 0 0 0 1 0 1 0 0 0 0 0 0 0 1 0 Q3 Q2 Q1 Q3 * Q2 * Q1 * Y 状态转换表 例6.2.2 试列出例6.2.1电路的状态转换表。 状态方程: ⎪ ⎩ ⎪ ⎨ ⎧ = ′ + ′ = ′ + ′ ′ = ′⋅ ′ 3 1 2 3 2 3 2 1 2 1 3 2 1 2 3 1 * * * ( ) Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q 输出方程:Y = Q2Q3 0 1 1 1 1 7 0 0 0 0 1 0 0 0 0 6 1 1 0 1 5 1 0 1 0 4 1 0 0 0 3 0 1 1 0 2 0 1 0 0 1 0 0 1 0 0 0 0 0 0 CLK Q3 Q2 Q1 Y 状态转换表的另一种形式 §6.2 时序逻辑电路的分析方法

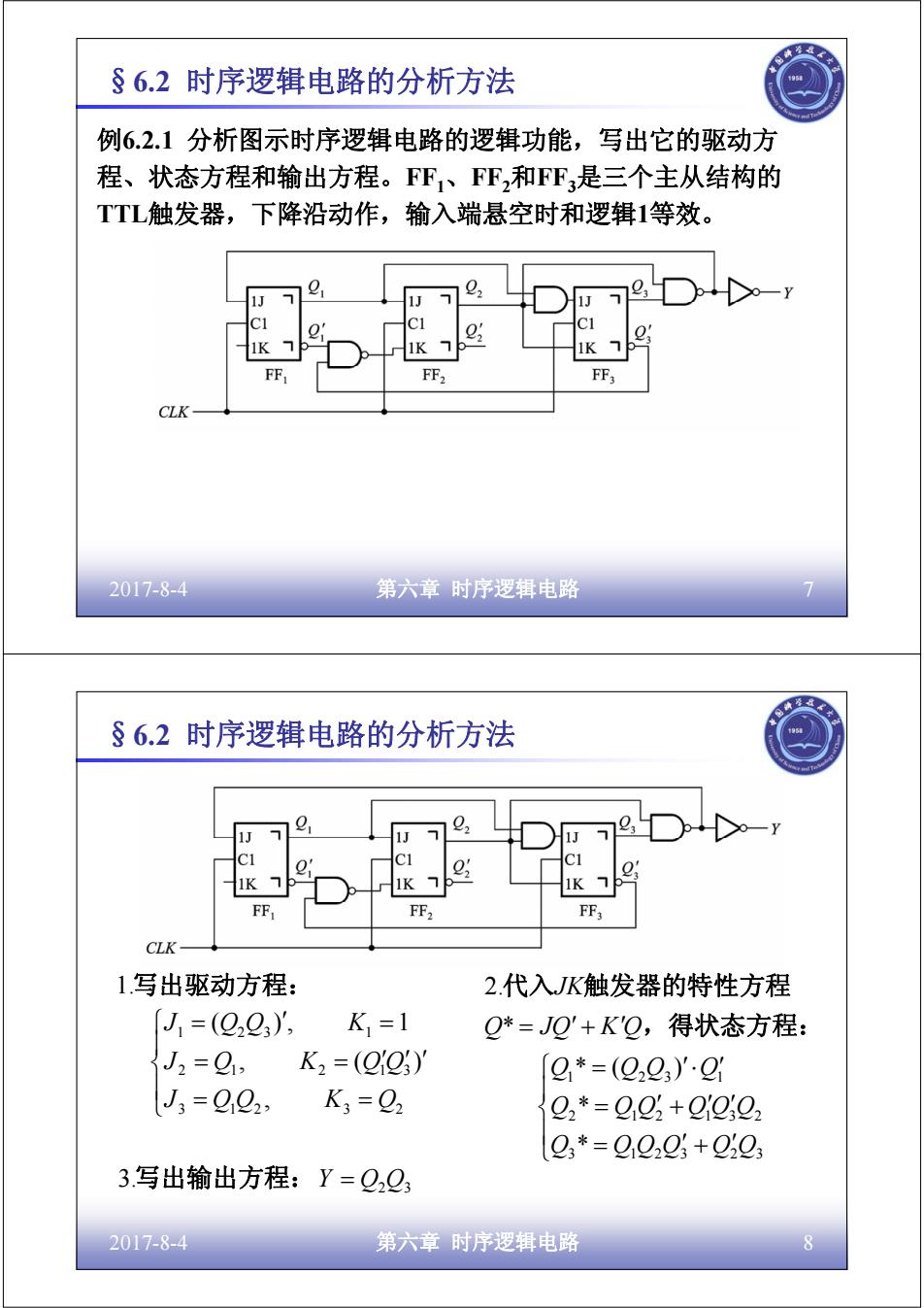

§6.2时序逻辑电路的分析方法 二、状态转换图 反映时序逻辑电路状态转换关系及相应输入、输出取值的 几何图形称为状态转换图。 例6.2.1的状态转换图。 /0 000 001 010 011 Q:Q:Q /0 110 101 10 100 /0 >每个圆圈表示电路的一个状态; >箭头表示状态转换的方向; >箭头旁注明状态转换前的输入变量取值和输出值。 三、状态机流程图 2017-8-4 第六章时序逻辑电路 §6.2时序逻辑电路的分析方法 四、时序图 在输入信号和时钟脉冲序列作用下,电路状态、输出状态随 时间变化的波形图称为时序图。 例6.2.1的时序图。 CLK 9 0 22 0 e; 2017-8-4 第六章时序逻辑电路 12

2017-8-4 第六章 时序逻辑电路 11 二、状态转换图 ¾每个圆圈表示电路的一个状态; ¾箭头表示状态转换的方向; ¾箭头旁注明状态转换前的输入变量取值和输出值。 三、状态机流程图 §6.2 时序逻辑电路的分析方法 例6.2.1的状态转换图。 反映时序逻辑电路状态转换关系及相应输入、输出取值的 几何图形称为状态转换图。 2017-8-4 第六章 时序逻辑电路 12 四、时序图 在输入信号和时钟脉冲序列作用下,电路状态、输出状态随 时间变化的波形图称为时序图。 例6.2.1的时序图。 §6.2 时序逻辑电路的分析方法

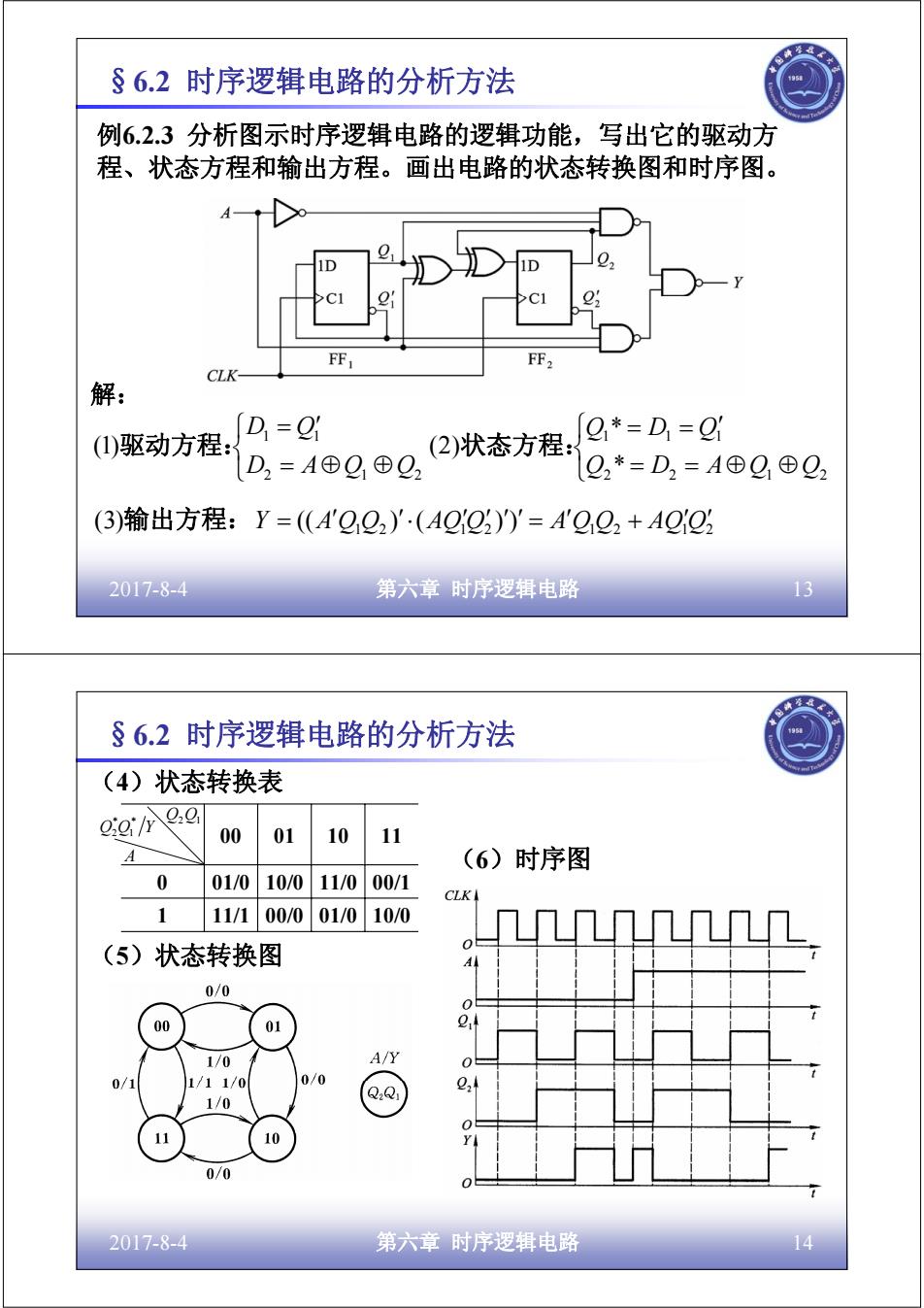

§6.2时序逻辑电路的分析方法 例6.2.3分析图示时序逻辑电路的逻辑功能,写出它的驱动方 程、状态方程和输出方程。画出电路的状态转换图和时序图。 FF, FF CLK- 解: (1)驱动方程: D=O D2=A⊕9⊕Q, 2状态方程:9=D=Q Q2*=D2=A田Q1田Q2 (3)输出方程:Y=(A'QQ2)'(AQQ2))'=AQQ2+AQQ 2017-8-4 第六章时序逻辑电路 13 §6.2时序逻辑电路的分析方法 (4)状态转换表 o:g/v 92Q 00 01 10 11 (6)时序图 0 01/0 10/0 11/0 00/1 CLK 1 11/1 00/0 01/0 10/0 (5)状态转换图 O A 0/0 00 01 24 1/0 A/Y 0/1 1/11/0 0/0 Q:Q, 224 1/0 1 10 0/0 2017-8-4 第六章时序逻辑电路

2017-8-4 第六章 时序逻辑电路 13 例6.2.3 分析图示时序逻辑电路的逻辑功能,写出它的驱动方 程、状态方程和输出方程。画出电路的状态转换图和时序图。 ⎩ ⎨ ⎧ = ⊕ ⊕ = ′ 2 1 2 1 1 (1) D A Q Q D Q 驱动方程: ⎩ ⎨ ⎧ = = ⊕ ⊕ = = ′ 2 2 1 2 1 1 1 * * (2) Q D A Q Q Q D Q 状态方程: 1 2 1 2 1 2 1 2 (3)输出方程:Y = ((A′Q Q )′⋅(AQ′Q′)′)′ = A′Q Q + AQ′Q′ 解: §6.2 时序逻辑电路的分析方法 2017-8-4 第六章 时序逻辑电路 14 1 11/1 00/0 01/0 10/0 0 01/0 10/0 11/0 00/1 00 01 10 11 A Q Q Y * * 2 1 Q2Q1 (4)状态转换表 (5)状态转换图 (6)时序图 §6.2 时序逻辑电路的分析方法

§6.2时序逻辑电路的分析方法 *6.2.3异步时序逻辑电路的分析方法 ●电路中的触发器没有统一的时钟信号,触发器状态的变化不 是同时发生的。 例6.2.4已知异步时序电路的逻辑图如图所示,试分析它的逻辑 功能,画出电路的状态转换图和时序图。触发器和门电路均为 TTL电路。 clko FF FR FF FF 2017-8-4 第六章时序逻辑电路 15 §6.2时序逻辑电路的分析方法 clk clk clk 1K FFo FF FF, FF 解: 驱动方程: 状态方程: Jo=Ko=1 Q。=Q6·clk J1=Q5,K1=1 Q=Q2·clk J2=K2=1 O =03.clkz J3=Q22,K3=1 O;=0003.clk; 输出方程:C=QQ3 2017-8-4 第六章时序逻辑电路 16

2017-8-4 第六章 时序逻辑电路 15 *6.2.3 异步时序逻辑电路的分析方法 z电路中的触发器没有统一的时钟信号,触发器状态的变化不 是同时发生的。 例6.2.4 已知异步时序电路的逻辑图如图所示,试分析它的逻辑 功能,画出电路的状态转换图和时序图。触发器和门电路均为 TTL电路。 §6.2 时序逻辑电路的分析方法 2017-8-4 第六章 时序逻辑电路 16 ⎪ ⎪ ⎩ ⎪ ⎪ ⎨ ⎧ = = = = = ′ = = = , 1 1 , 1 1 3 1 2 3 2 2 1 3 1 0 0 J Q Q K J K J Q K J K 解: ⎪ ⎪ ⎩ ⎪ ⎪ ⎨ ⎧ = ′ ⋅ = ′ ⋅ = ′ ′ ⋅ = ′ ⋅ 1 2 3 3 * 3 2 2 * 2 3 1 1 * 1 0 0 * 0 Q Q Q Q clk Q Q clk Q Q Q clk Q Q clk C = Q0Q3 驱动方程: 状态方程: 输出方程: §6.2 时序逻辑电路的分析方法

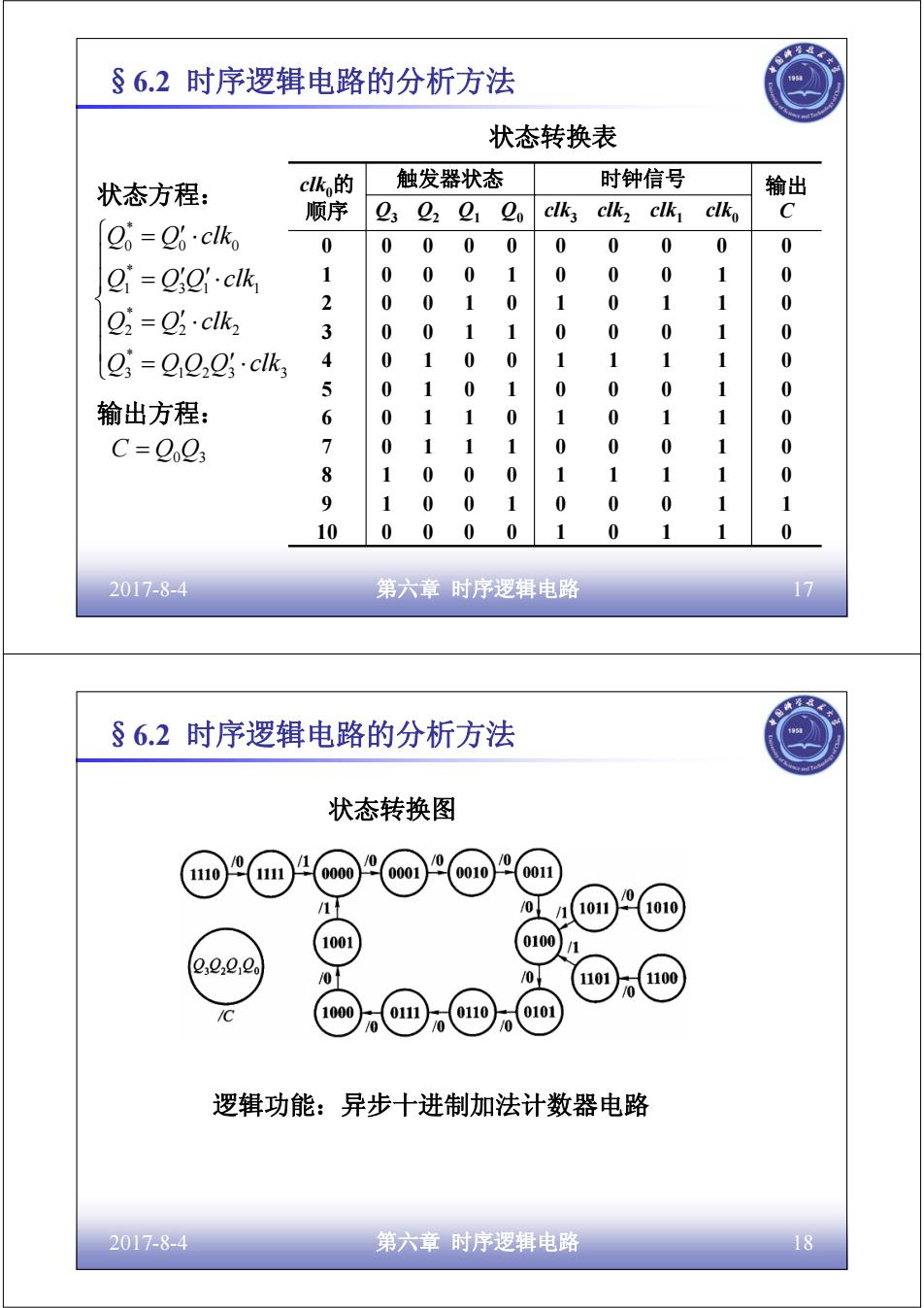

§6.2时序逻辑电路的分析方法 状态转换表 状态方程: clk,的 触发器状态 时钟信号 输出 顺序 2322 2120 clk clk,clk clko C g=g·clk 0 0 0 0 0 0 0 0 0 0 Q"=00'.clk 1 0 0 0 1 0 0 0 1 0 2 0 0 1 0 1 0 1 1 0 Q2=Q3·ck 3 0 0 1 0 0 0 1 0 O:=00.0.clk 0 1 0 0 1 1 1 0 5 0 0 0 1 0 输出方程: 6 0 1 1 0 C=0003 7 0 1 0 0 0 1 0 8 1 0 0 0 1 1 1 1 0 9 1 0 0 1 0 0 0 1 1 10 0 0 0 0 0 1 0 2017-8-4 第六章时序逻辑电路 17 §6.2时序逻辑电路的分析方法 状态转换图 0 1110 1111 0000 0001 0010 0011 10 /1 /0 1011 1010 1001 0100 /1 20222o 0 /0 1101 1100 0 C 1000 0111 0110 0101 逻辑功能:异步十进制加法计数器电路 2017-8-4 第六章时序逻辑电路 18

2017-8-4 第六章 时序逻辑电路 17 ⎪ ⎪ ⎩ ⎪ ⎪ ⎨ ⎧ = ′ ⋅ = ′ ⋅ = ′ ′ ⋅ = ′ ⋅ 1 2 3 3 * 3 2 2 * 2 3 1 1 * 1 0 0 * 0 Q Q Q Q clk Q Q clk Q Q Q clk Q Q clk 状态方程: C = Q0Q3 输出方程: 10 0 0 0 0 1 0 1 1 0 9 1 0 0 1 0 0 0 1 1 8 1 0 0 0 1 1 1 1 0 7 0 1 1 1 0 0 0 1 0 6 0 1 1 0 1 0 1 1 0 5 0 1 0 1 0 0 0 1 0 4 0 1 0 0 1 1 1 1 0 3 0 0 1 1 0 0 0 1 0 2 0 0 1 0 1 0 1 1 0 1 0 0 0 1 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 clk0 clk1 clk2 clk Q3 Q2 Q1 Q0 3 输出 C clk0的 触发器状态 时钟信号 顺序 状态转换表 §6.2 时序逻辑电路的分析方法 2017-8-4 第六章 时序逻辑电路 18 状态转换图 逻辑功能:异步十进制加法计数器电路 §6.2 时序逻辑电路的分析方法

§6.3若干常用的时序逻辑电路 6.3.1移位寄存器 移位寄存器:具有储存代码和移位的功能。 移位:指寄存器里存储的代码能在移位脉冲的作用下依次左移 或右移。 应用:寄存代码、数据的串-并转换、数值运算、数据处理等。 1用D触发器构成的移位寄存器 并 行 输 出 12 FFo FF FF2 FF 患行凸 串行 输 1D 输出 >C1 移位CLK 脉冲 2017-8-4 第六章时序逻辑电路 19 §6.3若干常用的时序逻辑电路 19 输 出 D FF。 1 Do >CI >C1 CLK 移位寄存器中代码的移动情况 CLK的顺序 输入D 221 C, 23 0 0 0 0 0 0 1 1 1 0 0 0 2 2 0 0 1 0 0 09 3 1 0 1 0 4 1 1 0 2017-8-4 第六章时序逻辑电路 20

2017-8-4 第六章 时序逻辑电路 19 移位寄存器:具有储存代码和移位的功能。 移位:指寄存器里存储的代码能在移位脉冲的作用下依次左移 或右移。 1 用D触发器构成的移位寄存器 §6.3 若干常用的时序逻辑电路 6.3.1 移位寄存器 应用:寄存代码、数据的串-并转换、数值运算、数据处理等。 2017-8-4 第六章 时序逻辑电路 20 4 1 1 1 0 1 3 1 1 0 1 0 2 0 0 1 0 0 1 1 1 0 0 0 0 0 0 0 0 0 CLK的顺序 输入DI Q0 Q1 Q2 Q3 移位寄存器中代码的移动情况 §6.3 若干常用的时序逻辑电路