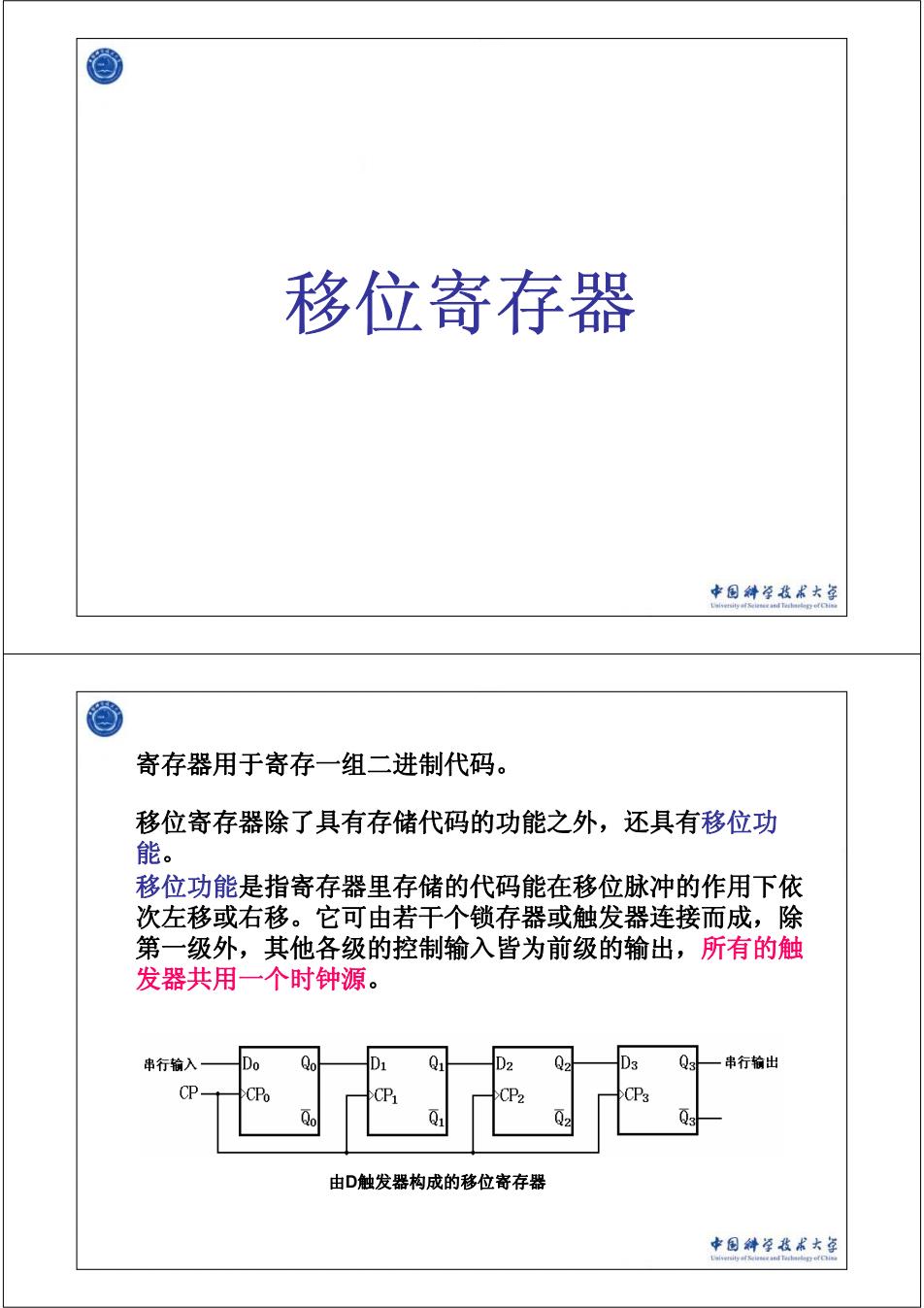

移位寄存器 中国斜学我术大学 寄存器用于寄存一组二进制代码。 移位寄存器除了具有存储代码的功能之外,还具有移位功 能。 移位功能是指寄存器里存储的代码能在移位脉冲的作用下依 次左移或右移。它可由若干个锁存器或触发器连接而成,除 第一级外,其他各级的控制输入皆为前级的输出,所有的触 发器共用一个时钟源。 串行输入 Do Qo D2 Q D3 Qs 串行输出 CP CPo CP2 CPs 由D触发器构成的移位寄存器 中国神学我术大学

移位寄存器 寄存器用于寄存一组二进制代码。 移位寄存器除了具有存储代码的功能之外,还具有移位功 能。 移位功能是指寄存器里存储的代码能在移位脉冲的作用下依 次左移或右移。它可由若干个锁存器或触发器连接而成,除 第一级外,其他各级的控制输入皆为前级的输出,所有的触 发器共用一个时钟源。 由D触发器构成的移位寄存器

实验内容 一、 用四块D型触发器(二块74LS74)接成4位输出的移位寄存器。 ◆LED ALED ALED ALED 串入 Q CP CPo (0.5Hz) 1.移位型环形计数器:从D端串行输入,寄存器的初态分别置成Q,-Q:0001, 0110,0101,0111,在每种初态下,把D接Q,记录在CP作用下LED的工作状态。 2.移位型扭环计数器:从D,端串行输入,寄存器的初态分别置成Q3-Q:0000和 0101,把D接Q,记录在CP作用下LED的工作状态。 3.自启动:D-Q1Q2Q3 Q3- 1413L12L1L10L9L8L 1413L12L110L9L8 Vee 2RD 2D 2CP 2SD 2Q 2Q 74LS74 74LS00 1RD 1D 1CP 1Sp 1Q1Q GND GND 1234567 1234567 中国神学我术大学 ty4T行 测试双向移位寄存器74LS194的逻辑功能 清零端CR接“1”,D,D1,D2,D3,S1,S分别接6个逻辑开关,CP接1Hz脉冲信号,Qo Q分别接4个LED 74LS194功能表 1615L1413L12L110L9 CR S1 So 工作状态 Vec Qo Q1 Q2 Q3 CP S1 So 0 ×× 置零 D 74LS194 1 00 保持 1 01 CR DsR Do D1 D2 D3 DsL GND 右移 1234678 1 10 左移 1 11 并行输入 1.S1S。=11,DDD,D3分别取0110和1001,记录Q-Q,的工作状态。 2.S1S,=00,观察并记录Q-Q,的状态。 3.SS。=01,取初态Q-Qg:1000,使DsR与Q相连,记录Q,-Q3的工作状态。 4.S1S。=10,取初态Q-Q3:0001,使Ds与Q相连,记录Q-Q3的工作状态。 5.将数字“6”锁存在寄存器中,并用数码管显示,观察SS为何值时,寄存器不受 CP的影响。 中园神学我术大学

实验内容 一、用四块D型触发器(二块74LS74)接成4位输出的移位寄存器。 1. 移位型环形计数器:从D0端串行输入,寄存器的初态分别置成Q3-Q0:0001, 0110,0101,0111,在每种初态下,把D0接Q3,记录在CP作用下LED的工作状态。 2.移位型扭环计数器:从D0端串行输入,寄存器的初态分别置成Q3-Q0:0000和 0101,把D0接 Q3,记录在CP作用下LED的工作状态。 3. 自启动: 二、测试双向移位寄存器74LS194的逻辑功能 清零端CR接“1”,D0,D1,D2,D3,S1,S0分别接6个逻辑开关,CP接1Hz脉冲信号,Q0- Q3分别接4个LED 1.S1S0=11,D0D1D2D3分别取0110和1001,记录Q0-Q3的工作状态。 2.S1S0=00,观察并记录Q0-Q3的状态。 3.S1S0=01,取初态Q0-Q3:1000,使DSR与Q3相连,记录Q0-Q3的工作状态。 4.S1S0=10,取初态Q0-Q3:0001,使DSL与Q0相连,记录Q0-Q3的工作状态。 5.将数字“6”锁存在寄存器中,并用数码管显示,观察S1S0为何值时,寄存器不受 CP的影响。 CR S1 S0 工作状态 0 1 1 1 1 × × 0 0 0 1 1 0 1 1 置零 保持 右移 左移 并行输入 74LS194功能表

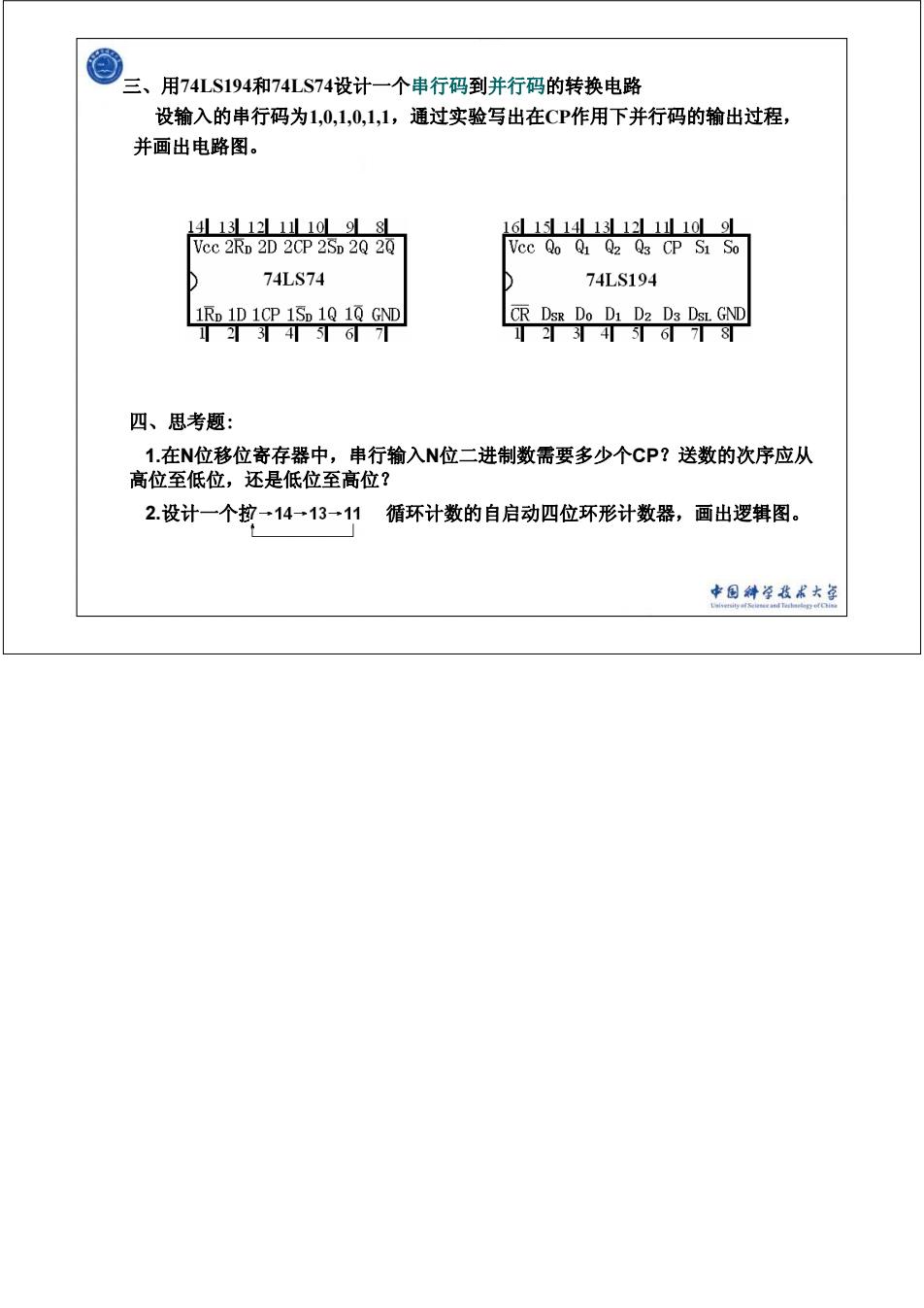

三、 用74LS194和74LS74设计一个串行码到并行码的转换电路 设输入的串行码为1,0,1,0,1,1,通过实验写出在CP作用下并行码的输出过程, 并画出电路图。 1413L12L1110L9L8L 1615d1413L121110L9L Vec 2RD 2D 2CP 2SD 2Q2Q Vec Qo Q1 Q2 Q3 CP S1 So D 74LS74 74LS194 1RD 1D 1CP 1SD 1Q1Q GND CR DsR Do D1 D2 D3 DsL GND 1234567 12345678 四、思考题: 1.在N位移位寄存器中,串行输入N位二进制数需要多少个CP?送数的次序应从 高位至低位,还是低位至高位? 2.设计一个拉→14一13→11 循环计数的自启动四位环形计数器,画出逻辑图。 中国神学我术大学 vutsily af eletes anil Teshtebt行(

三、用74LS194和74LS74设计一个串行码到并行码的转换电路 设输入的串行码为1,0,1,0,1,1,通过实验写出在CP作用下并行码的输出过程, 并画出电路图。 四、思考题: 1.在N位移位寄存器中,串行输入N位二进制数需要多少个CP?送数的次序应从 高位至低位,还是低位至高位? 2.设计一个按 循环计数的自启动四位环形计数器,画出逻辑图