目 录 第1章VLSI概论 … 1 1.1复杂性与设计……1 1,1,1设计流程举例 3 1.1.2VL芯片的类型…… 5 1.2基本概念… 5 1.3本书安排 7 1,4参考资料 …8 第1部分硅片逻辑 第2章MOSFET逻辑设计 0…13 2.1理想开关与布尔运算… 13 2.2 MOSFET开关 17 2.3基本的CMOS逻辑门… 23 2.3.1非门(NOT门)… 24 2.3.2CM0S或非门(NOR门)… 25 2.3.3CMOS与非门(NAND门)… 28 2.4CMOS复合逻辑门… 30 2.4.1结构化逻辑设计……32 2.4.2异或门(XOR)和异或非门(XNOR)… 40 2.4.3一般化的AOI和OA1逻辑门 41 2.5传输门(TG)电路 42 逻辑设计…… 43 2.6时钟控制和数据流控制。 45 2.7参考资料… 48 2.8习题… 48 第3章CMOS集成电路的物理结构 … 51 3.1集成电路工艺层… 51 互连线的电阻和电容… 53 3.2M0SFET… 56 32.1硅的导电性… 58 3.2.2nFET和pFET… 62 3.2.3FET中的电流 0。±+4t+00t+4ee000t 63 3.2.4栅电容的驱动… 67 ·I

3.3CMOS工艺层 69 3.4FET阵列设计 71 3.4.1基本门设计……… 73 3.4.2复合逻辑门4……… 76 3.4.3一般性讨论 78 3.4.4小结… 81 3.5参考资料 81 3.6习题… 82 第4章CM○S集成电路的制造 85 4.1硅工艺概述……。 85 本章概要… 87 4.2材料生长与淀积… 88 4.2.1二氧化硅… 88 4,2.2氨化硅……… 89 4,2.3多晶硅… 90 4,2.4金属化… 90 4.2.5掺杂硅层 91 4.2.6化学机械抛光 92 4.3刻蚀…… 93 洁净间………… …97 4.4CMOS工艺流程 97 工艺改进…… 101 4.5设计规则… 104 4.5,1物理极限… 107 4.5.2电气规则…“ 108 4.6参考资料… 108 第5章物理设计的基本要素…… 109 5.1基本概念… 109 CAD工見·… 110 5.2基本结构的版图 1I1 5.2.1n阱… 5.2.2有源区… 112 5.23掺杂硅区… 113 5.2.4M0F5T…**+" 114 5.2.5有源区接触… 117 5,2.6金属层1 118 5.2.7通孔和多层金属 121 5.2.8防止门锁现象… 121 5.2,9版图编辑器… 123 5.3单元概念… 124 5.4FET的尺寸确定和单位晶体管…129 ·Ⅱ·

5.5逻辑门的物理设计…133 5.5.1T单元…134 5.5.2与非门(NAND)和或非门(NOR)单元…135 5.5.3复合逻辑门………136 5.5.4关于版图的小结 136 5.6设计层次化 137 5.7参考资料… …139 第2部分从逻辑到电子电路 第6章M0SFET的电气特性…143 6.1M0S物理学…, 143 阔值电压的推导… 6.2nFET电流-电压方程… 147 6.2,1 SPICE Level】方程…**,, 153 6.2.2体偏置效应… 153 6,2.3电流方程推导 154 6.3FET的RC模型… 157 6.3.1漏源FET电阻… 0…00440444: 157 6.3.2FET电容… 159 6.3.3模型建立“……… 163 6.4pFET特性…… 165 pFET寄生参数 …小 168 6.5小尺寸MOSFET模型 169 6.5,1尺寸缩小原埋… 169 6.5.2小尺寸器件效应……… 171 6.5,3SPCE模型… …172 6.6参考资料… 173 6.7习题 …174 第7章CMOS逻辑门电子学分析… 176 7.1CMOS反相器的直流特性 176 7.2反相器的开关特性…… 181 7,2.1下降时问计算… 185 7.2.2上开时间… 186 7,2.3传播延时…… 188 7.2,4一毅分析 189 7.2.5反相器电路小结 191 7.3功耗… 191 7.4DC特性:与非门(NANI)门)和或非j(NOR门) 193 7.4.1与非门(NAD门)分析…193 7.4.2或非门(NOR门)… 196 7.5与非门和或非门的暂态响应…… 197 ·Ⅲ·

7.5.】NAN2开关时间…198 7.5.2二输入或非门(NOR2)的开关时间 444*4+…200 75.3小结*…n**……+小” 202 7.6复合逻辑门的分折………… 202 204 7.7逻辑门过渡特性设计 205 7.8传输门和传输管… 208 7.9关于SPICE模拟… 211 7.10参考资料… 213 7,11题…… 214 第8章高速CMOS逻辑电路设计 217 8.1门延时…… 217 8.2驱动大电容负载… 224 在反相器链中使延时最小 226 8.3逻辑努力(Logical Effort)… 231 8.3.1基本定义… 231 8.3.2一般化情形… 235 8.3.3级数的优化… 239 8.3.4逻辑面积…… 240 8.3.5分支情况… 241 8.3.6小结… 242 8.4 BiCMOS驱动器 242 8.4.1双极型管的特性… 243 8.4.2驱动电路… 246 8,5参考资料… 44” 248 8.6习题…… 249 第9章CMOS逻辑电路的高级技术 251 9.1镜像电路… 251 9.2淮nMOS电路… 253 9.3三态电路… 255 9.4时钟控制CMOS … 256 9.5动态CM○S逻辑电路… 261 9.5.1多米诺逻辑… 263 9,5,2动态逻辑电路的功耗… 266 9.6双轨逻辑电路……1 266 9.6.1CVL… 267 9.6.2互补传输管逻辑… 269 9.7参考资料…… 270 9.8习题 …270 ·V·

第3部分 VLSI系统设计 第10章用Verilog硬件描述语言描述系统 275 10.1基本概念。 275 10.2结构化的门级模型… 276 Viog举例… 276 10.3开关级建模…… 284 10.4层次化设计… 288 10.5行为级和RTL建模 291 10.6参考资料…… 297 10.7习题… 298 第11章常用的VLSl系统部件 300 11.1多路选择器… 300 11.2二进制译码器… 305 11.3相等检测器和比较器 307 11.4优先权编码器… 310 11,5移位和循环操作 313 11.6锁存器… 316 11.7D触发器… 321 11.8寄存器… 。4+e4“4 326 11.9综合的作用… 327 11.10参考资料…… 328 11.11习题… 329 第12章CMOS VLS引运算电路… 330 12.1一位加法器电路… 330 12.2串行进位加法器 335 12.3超前进位加法器… 338 12.3,1曼彻斯特进位链…… 343 12.3.2扩展为宽位加法器 345 12.4其他高速加法器… 348 12.4,1进位旁路电路(Cary-Skip Circuits)… 348 12.4.2进位选择加法器(Cay-Select Adder)… 349 12.4.3进位保留加法器(Cary-Save Adder) 350 12.5乘法器… …351 12.5.1阵列乘法器… 353 12.5.2其他乘法器 355 12.6小结… 358 12.7参考资料… 358 12.8习题… …359 .V·

第13章存储器与可编程逻辑…… 360 13.1静态RAM… 360 13.2RAM阵列……364 13.3动态RAM… 372 13.3.1DRAM单元的物理设计……………………………………·375 13.3,2分割字线结构…… 376 13.4R○M阵列… 377 用户编程ROM… ........ 379 13.5逻辑阵列… 382 13.5.】可缩程逻辑阵列… 382 3.5.2门阵列… 385 13.6参考资料… 386 13.7习题… 387 第14章系统级物理设计… 390 14.1大规模集成电路的物理设计 390 14.2互连线延时模型… 391 】4.2.}信号延时与连线长度的关系……… 398 14,2.2对互连线延时的考虑 399 14.3串扰…… …399 有关串忧的考虑 403 14.4互连线的尺寸缩小… 404 14,5布局布线… 406 14.6输人和输出电路… …410 14.6.1输入电路… 410 【4,6.2输出驱动器… 414 14.7电源的分配和功耗… 416 同时切换引起的噪声… 418 14.8低功耗设计考虑… 421 14.9参考资料… 422 14.10习题… 423 第15章LS时钟和系统设计… 426 15.1时钟控制触发器… 426 经典的状态机” 427 15.2CMOS时钟方式 429 15.2.1钟控逻辑链… 429 15.2.2动态逻辑链… 437 15.3流水线系统… 439 15.4时钟的产生和分配… 443 【5.4,1时钟的稳定和产生 444 15.4.2时钟布线与驱动器树结构… 446 ·Ⅵ·

15.5系统设计考虑…451 15,5.1位片式设计****“**+*…“******…甲**” 452 15.5.2 cache存储器 453 15.5.3脉动系统和并行处理… 454 15.5,4小结*小…***…*…**…**, 455 15.6参考资料… …………455 第16章视S引电路的可靠性与测试…457 16.1一般概念… ……457 可靠性建模… 459 16.2CMOS测试 462 16.2,1C0S故暗模型……… …463 16.2,2门级测试…… …*………464 16.2.3100测试 466 16.3测试生成方法… 467 16.3.1静态CM0S逻辑门……467 16.3.2故障的逻辑影响 468 16.3.3路径的敏化 ……470 16.3.4D算法 470 16.3.5布尔差分…… 471 16,4小结… 473 16.5参考资料… 473 ·W·

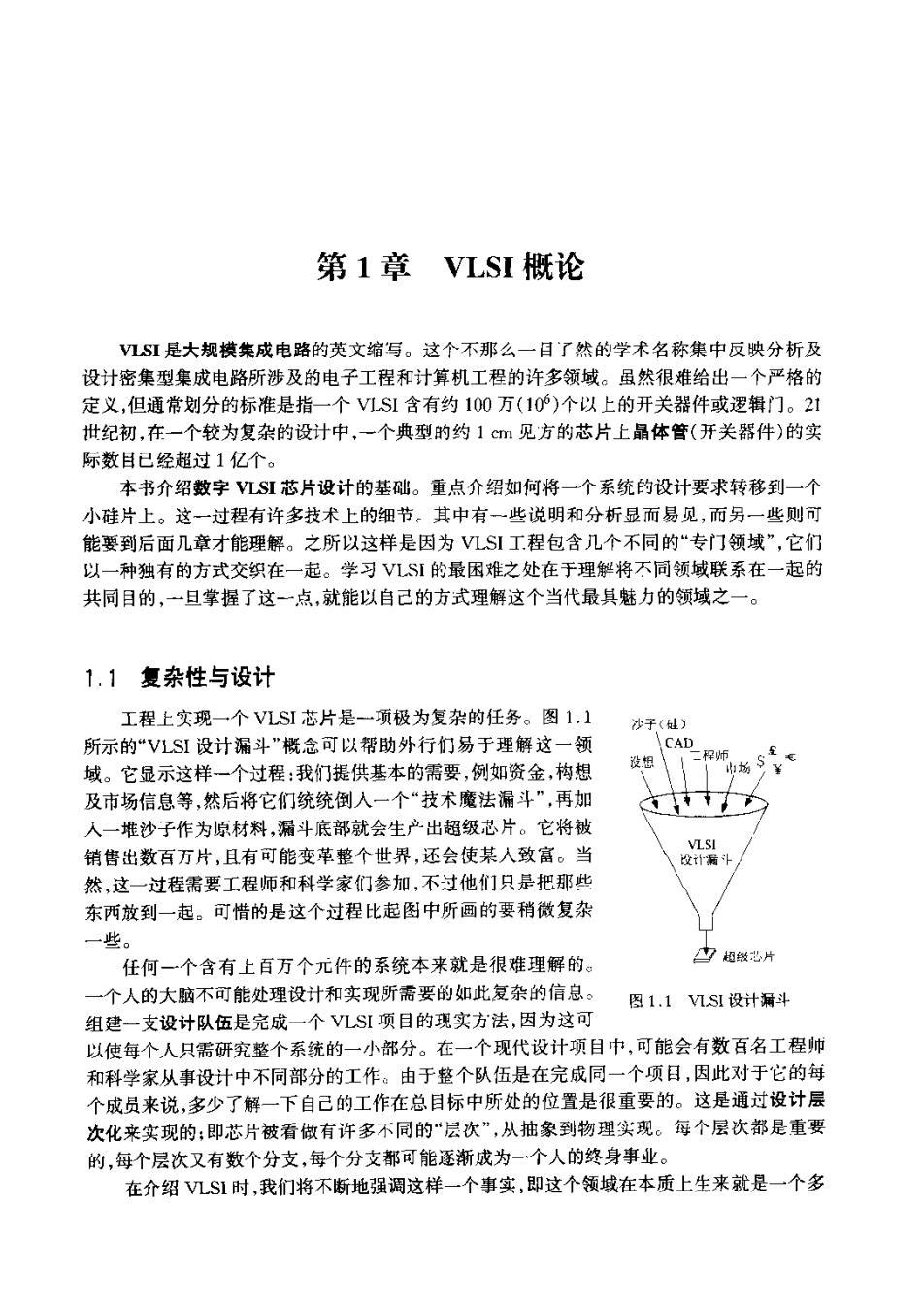

第1章 VLSI概论 LSI是大规模集成电路的英文缩写。这个不那么一目了然的学术名称集中反映分析及 设计密集型集成电路所涉及的电子工程和计算机工程的许多领域。虽然很难给出一个严格的 定义,但通常划分的标准是指一个V1S1含有约100万(10)个以上的开关器件或逻辑门。21 世纪初,在一个较为复杂的设计中,一个典型的约1cm见方的芯片上晶体管(开关器件)的实 际数目已经超过1亿个。 本书介绍数字VLS芯片设计的基础。重点介绍如何将一个系统的设计要求转移到一个 小硅片上。这一过程有许多技术上的细节。其中有一些说明和分析显而易见,而另一些则可 能要到后面几章才能理解。之所以这样是因为VLS工程包含几个不同的“专门领域”,它们 以一种独有的方式交织在一起。学习VLS的最困难之处在于理解将不同领域联系在一起的 共同目的,一旦掌握了这一点,就能以自己的方式理解这个当代最其魅力的领域之一。 1.1复杂性与设计 工程上实现一个VLSI芯片是一项极为复杂的任务。图1.1 沙子(陆) 所示的“V1SI设计漏斗”概念可以帮助外行们易于理解这一领 CAD 设想 程师 域。它显示这样一个过程:我们提供基本的需要,例如资金,构想 h场¥ 及市场信息等,然后将它们统统倒入一个“技术魔法漏斗”,再加 入一堆沙子作为原材料,漏斗底部就会生产出超级芯片。它将被 VLSI 销售出数百万片,且有可能变革整个世界,还会使某人致富。当 设计漏斗 然,这一过程需要工程师和科学家们参加,不过他们只是把那些 东两放到一起。可惜的是这个过程比起图中所画的要稍微复杂 一些。 任何一一个含有上百万个元件的系统本来就是很难理解的。 雪超微忠片 一个人的大脑不可能处理设计和实现所需要的如此复杂的信息。 图1.1V1SI设计漏斗 组建一支设计队伍是完成一个VLS项目的现实方法,因为这可 以使每个人只需研究整个系统的一小部分。在一个现代设计项目中,可能会有数车名工程帅 和科学家从事设计中不同部分的工作。由于整个队伍是在完成同一个项目,因此对于它的每 个成员来说,多少了解一下自己的工作在总目标中所处的位置是很重要的。这是通过设计层 次化来实现的:即芯片被看做有许多不同的“层次”,从抽象到物理实现。每个层次都是重要 的,每个层次又有数个分支,每个分支都可能逐渐成为一个人的终身事业。 在介绍VLS时,我们将不断地强调这样一个事实,即这个领域在本质上生来就是一个多

2 超大规模集成电路与系统导论 学科的领域,需要无数方面的专家共同实现一个能够正确工作的设计。计算机结构设计人员 必须与程序编写人员及逻辑设计人员交流合作,他们还必须理解电路设计及硅片加工的某些 问题。电子专业人员必须超出电路的范围,看看他们研究的元件如何影响系统。每个人都需 要依靠计算机辅助设计工具及支持小组,支持小组完成10000个左右的其他任务,在此就不 赘述了。如果这种说法使这个领域听起来十分复杂,那是因为它就是如此。VLSI不是一个 容易理解的简单学科,但是经过一段适当的时间是能够掌握它的基础的。最终在这个领域工 作的人往往会被吸引住,因为其中的一个或多个方面会引起他们的兴趣,并且符合他们的知识 背景。 既然对VLSI所涉及的范围有所了解,就让我们进一步来描述它的设计过程。图1.2显 示它的概貌及在设计过程中的各个主要步骤。VLS设计的起始点是对系统要求的说明。在 这一点上,产品同时用一般的和专门的术语定义,即提出整个项目的设计目标,如功能、速度、 尺寸等等。这是层次化设计的最高层。系统说明用来建立抽象的高层次的模型。数字设计通 常基子某种硬件描述语言(HDL),它可以建立操作的抽象模型。VHDL和VerilogTM是实际中 最常用的硬件描述语言,其他几种语言(包括C和C++)也被应用。抽象模型包含系统中每 个模块的功能及各个模块间相互作用的信息。这个模型必须经过广泛的验证步骤,一遍遍地 检查设计以确保正确无误。 项层设计· 系统要求说明 一初始概念 系统设计与验证 抽象的高层次模型 女 逻斩综合 一逻辑设计与验证 ↓ 电路设计 =CMOS设计与验证 & 底层设计· 物理设计 一娃片逻辑设计与验证 制造 一大批量生产测试与封装 0 完成的VLSI芯片 一市为 图1.2层次化设计的一般框图 设计过程的下一个步骤叫做综合。通过抽象的逻辑模型,完成系统的逻辑设计,即说明构 成每个单元所需要的基本门和基本单元。这是将设计转人电路设计层的基础。这里采用晶体 管作为开关,而布尔变量则看成变化的电压信号。为了构成晶体管,我们再向下一层转人物理

第1章V1SI概论 3 设计。在这一层,采用复杂的映射技术将电路建立在一个微小的硅片上,晶体管和导线转变成 用金属和其他材料做成的极其微小的形式。物理设计是系统设计的最后一步。设计完成后, 项目进人生产线,其最终结果是一个完成的电子VLSI芯片。 如果从系统一级的要求出发,整个设计过程叫做自上而下的方法。起始的工作是相当抽 象和理论性的。在许多步骤完成之前,这些工作与硅片没有直接的联系。反过来的方法起始 于硅片和电路阶段。第一步是建立最基本的单元,如逻辑门、加法器、寄存器等。这些单元组 合起来就可得到较大、较复杂的逻辑模块,后者又可用做更大规模设计的功能块。这一自下而 上的设计方法用于小项目尚可,对复杂的现代VLS引设计就不切实际了。如果从一位一位数 开始设计一个工作正确的16位微处理机,那将是极端困难的。 自下而上地学习VLS的各个方面则是学习这一领域基础的好办法,因此本书的前半部 分即采用这一方法。我们将从简单开始,逐渐进人复杂、抽象的更高层次。目的是给大家一个 连贯的认识,即这个领域是一个由许多不同领域组成的整体。有些问题即便看上去极度专业 化,以后也会与其他概念相关联。一旦掌握了基础,我们就可以站在更高的层次上研究问题。 本书的后半部分将介绍VLSI系统方面的问题,以给出一个完整的概念。 1.1.1设计流程举例 作为一个层次化设计的例子,让我们先确定在一个基本的微处理器设计中什么是必需的。 初始的构想可在定义指令集和部件的系统层次上。一条指令是所设计的微处理器能够执行的 一个基本操作(如两个二进制数相加)。指令集则是一个具体处理器的全部指令集合。部件是 提供某个指定功能(如加法)的数字逻辑单元。计算机体系结构领域则研究组成计算机的单元 及它们是如何组合在一起的。 图1.3为这一问题的基本设计流程。指今集和部件组可以来建造一个高层次的结构模 型。这个层次只是抽象地描述系统的行为而不考虑在实际构成电路时需要的低层次细节。例 如,我们]可以定义一个加法运算为 register_X←A+B 意即将A和B的和传送到一个名为register_X(寄存器X)的存储器件中。这种高层次的抽象 可以用来定义处理器的体系结构,且常称为寄存器传输级(RTL)描述。RTL模型只描述系统 如何操作,不考虑具体的部件。当用HDL语言把它写下后,就可用来侧试指令并且验证体系 结构的行为。抽象设计能为系统建立一个方框图。 RTL代码可以转化为一个包含更多有关操作和行为部件细节的等效描述。每个功能块 的操作可在DL行为级上进行概括,这时的重点是放在这些功能块与其他部分相互作用的大 行为上。这一阶段的行为建模是极为关键的,因为要用它来验证体系结构。这一阶段的所有 问题都必须得到解决后才能进行下一步工作。 下一阶段的设计过程是将系统的功能块转化为以布尔方程和逻辑门为基础的逻辑模型。 这使抽象设计进入实际阶段,它是实现硬件设计的第一步。这一阶段可以通过两种途径完成: 逻辑电路的自动设计与综合或定制设计。自动设计以一系列在高性能L作站运行的CAD(计 算机辅助设计)工具为基础。一个综合工具通常可以接受HDL代码,按照一组预先确定的规 则产生相应的逻辑电路。编写恰当的HDL代码能够很快地产生逻辑设计,所以自动综合用于