正在加载图片...

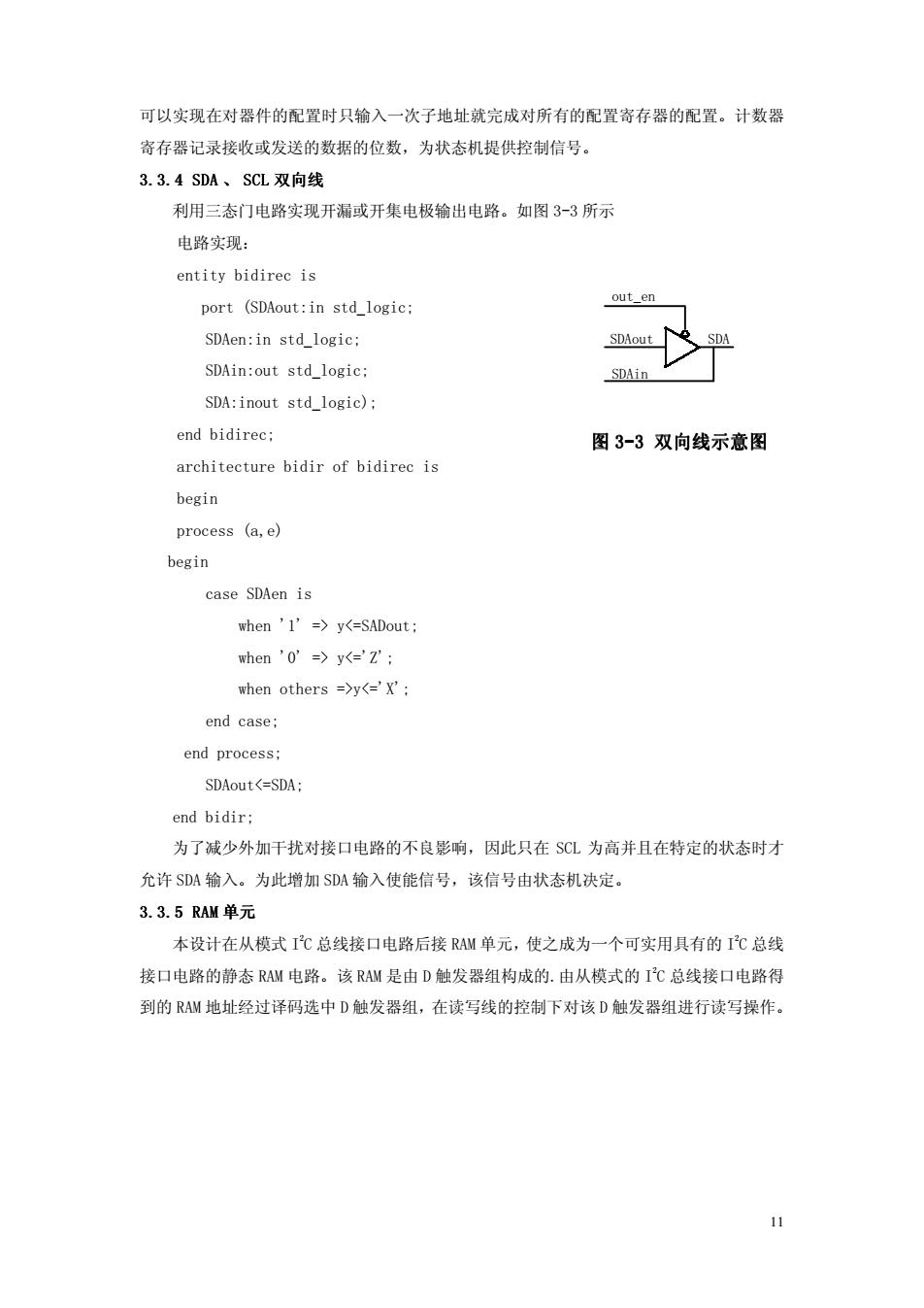

可以实现在对器件的配置时只输入一次子地址就完成对所有的配置寄存器的配置。计数器 寄存器记录接收或发送的数据的位数,为状态机提供控制信号。 3.3.4SDA、SCL双向线 利用三态门电路实现开漏或开集电极输出电路。如图3-3所示 电路实现: entity bidirec is outen port (SDAout:in std_logic; SDAen:in std logic; SDAout SDA SDAin:out std logic; SDAin SDA:inout std_logic); end bidirec; 图3-3双向线示意图 architecture bidir of bidirec is begin process (a,e) begin case SDAen is when’1'=>y<=SADout: when'0'=>y<='Z'; when others =>y<='X'; end case; end process; SDAout<=SDA: end bidir; 为了减少外加干扰对接口电路的不良影响,因此只在SCL为高并且在特定的状态时才 允许SDA输入。为此增加SDA输入使能信号,该信号由状态机决定。 3.3.5RAM单元 本设计在从模式IC总线接口电路后接RAM单元,使之成为一个可实用具有的I℃总线 接口电路的静态RAM电路。该RAM是由D触发器组构成的.由从模式的IC总线接口电路得 到的RAM地址经过译码选中D触发器组,在读写线的控制下对该D触发器组进行读写操作。 "" FG )5F ¤

#$BNM¦y·¨®Ù+Ä

#$Ïá

#$%

Ïá xkãw

«

9uvwWX¡¢% oLoLn e

< f c v@âjkâ

l%Ú~ ojo +P ò zõüü ûÕ{zè

{ü d e

Nüõ üÕï

è

e

zõõ üÕï

è

e

õ

Nü üÕï

è

e

õ

Nü üÕï

èe

zõÕ ûÕ{zè

y{èüzèüN{z ûÕ{

ûÕ{zè ûz

õ {

èz dyOze ûz

õ èyz e

zõ zõ g

!

e

Nü

zõ K

!

ë

zõ

üz{

!

À

zõÕ èyz

zõÕ {

èz

e

Nü!

e

zõÕ ûÕ{

912 W"

#$¸Õ&NF f 9÷DEFÚ,

uvB 89 e

M%9& e

M'Ò¡¢¡¢uvw,% oLoL %

P ¾& F

? %

P ¾&'¥Ù9)ÃÄ

'v %

P % %

P e (ã ºqÙ

L

(

%

P ·¨#7)*²* e (ã ºFXY

WX e (㠺8XY I% �����������������������������������������������