正在加载图片...

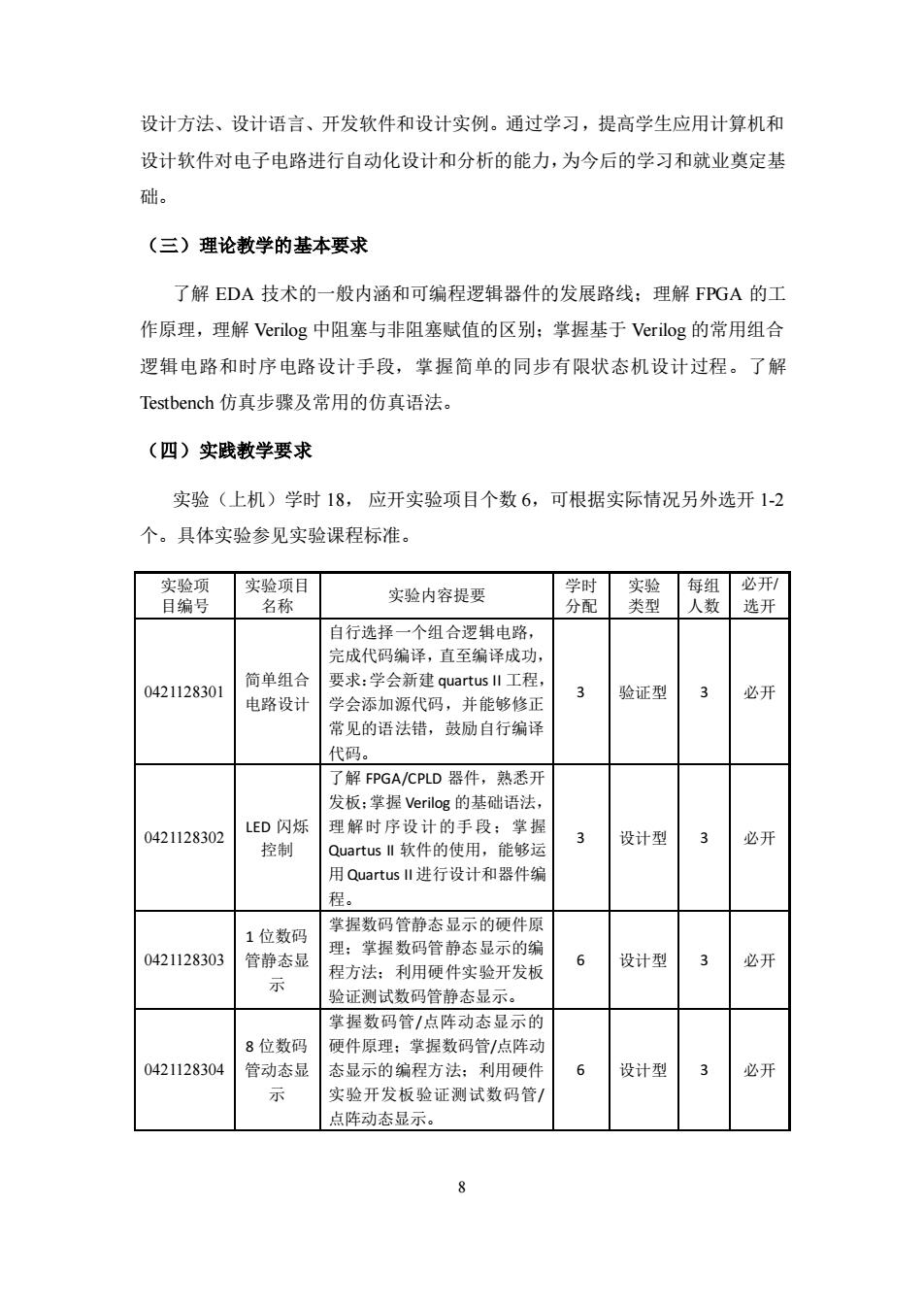

设计方法、设计语言、开发软件和设计实例。通过学习,提高学生应用计算机和 设计软件对电子电路进行自动化设计和分析的能力,为今后的学习和就业奠定基 础。 (三)理论教学的基本要求 了解EDA技术的一般内涵和可编程逻辑器件的发展路线:理解FPGA的工 作原理,理解Verilog中阻塞与非阻塞赋值的区别:掌握基于Verilog的常用组合 逻辑电路和时序电路设计手段,掌握简单的同步有限状态机设计过程。了解 Testbench仿真步骤及常用的仿真语法。 (四)实践教学要求 实验(上机)学时18,应开实验项目个数6,可根据实际情况另外选开1-2 个。具体实验参见实验课程标准。 实验内容提要 自行选择一个组合逻辑电路, 完成代码编译,直至编译成功, 简单组合 0421128301 要求:学会新建quartus ll工程 3 电路设计 学会添加源代码 并能够修正 验证型 必开 常见的语法错,鼓励自行编译 代码。 了解FPGA/CPLD器件,孰悉开 发板:掌握Verilog的基础语法, 042112830 LED闪烁 理解时序设计 的手段:掌护 控制 Quartus l软件的使用 能够远 3 设计型 3 必开 用Quartu5川进行设计和器件 程。 堂握数码管静本品示的硬件原 1位数码 042112830 管静态显 理:掌握数码管静态显示的编 3 程方法:利用硬件实验开发板 设计型 必开 验证测试数码管静态显示。 掌握数码管/点阵动态显示的 8位数码 硬件原理:堂挥数码管/点阵动 0421128304 管动态显 态显示的编程方法:利用硬件 6 设计型 3 必开 实验开发板验证测试数码管/ 点阵动态显示。8 设计方法、设计语言、开发软件和设计实例。通过学习,提高学生应用计算机和 设计软件对电子电路进行自动化设计和分析的能力,为今后的学习和就业奠定基 础。 (三)理论教学的基本要求 了解 EDA 技术的一般内涵和可编程逻辑器件的发展路线;理解 FPGA 的工 作原理,理解 Verilog 中阻塞与非阻塞赋值的区别;掌握基于 Verilog 的常用组合 逻辑电路和时序电路设计手段,掌握简单的同步有限状态机设计过程。了解 Testbench 仿真步骤及常用的仿真语法。 (四)实践教学要求 实验(上机)学时 18, 应开实验项目个数 6,可根据实际情况另外选开 1-2 个。具体实验参见实验课程标准。 实验项 目编号 实验项目 名称 实验内容提要 学时 分配 实验 类型 每组 人数 必开/ 选开 0421128301 简单组合 电路设计 自行选择一个组合逻辑电路, 完成代码编译,直至编译成功, 要求:学会新建 quartus II 工程, 学会添加源代码,并能够修正 常见的语法错,鼓励自行编译 代码。 3 验证型 3 必开 0421128302 LED 闪烁 控制 了解 FPGA/CPLD 器件,熟悉开 发板;掌握 Verilog 的基础语法, 理解时序设计的手段;掌握 Quartus II 软件的使用,能够运 用Quartus II 进行设计和器件编 程。 3 设计型 3 必开 0421128303 1 位数码 管静态显 示 掌握数码管静态显示的硬件原 理;掌握数码管静态显示的编 程方法;利用硬件实验开发板 验证测试数码管静态显示。 6 设计型 3 必开 0421128304 8 位数码 管动态显 示 掌握数码管/点阵动态显示的 硬件原理;掌握数码管/点阵动 态显示的编程方法;利用硬件 实验开发板验证测试数码管/ 点阵动态显示。 6 设计型 3 必开