正在加载图片...

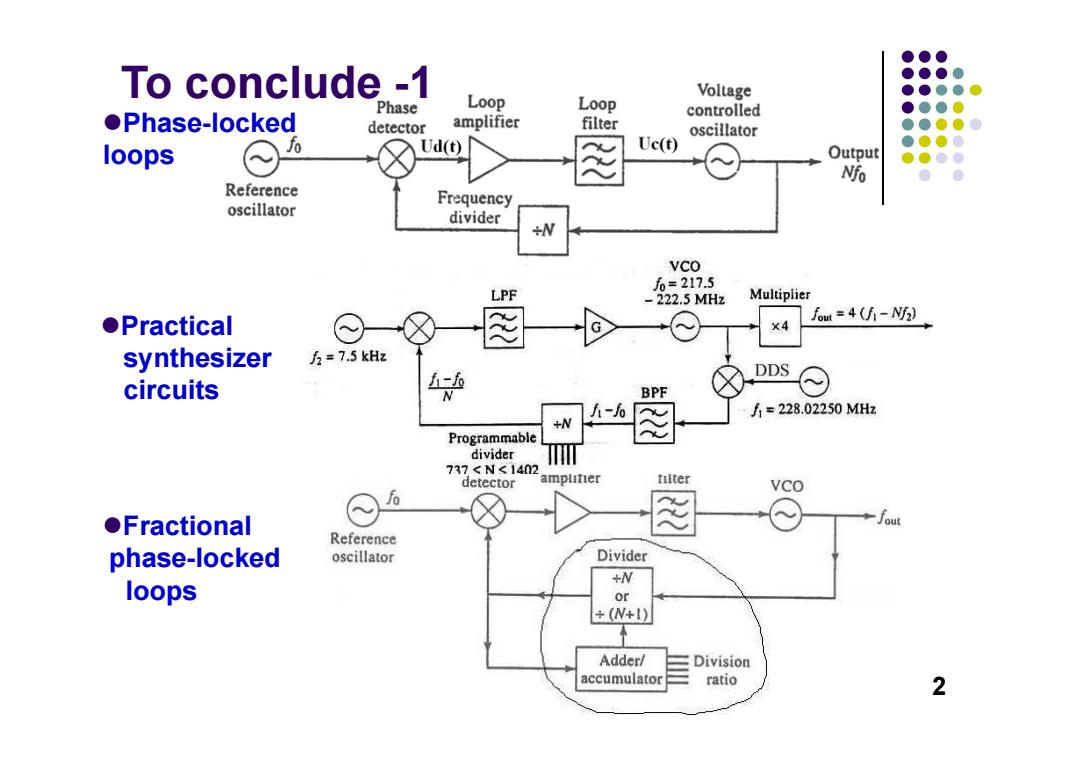

●●● To conclude -1 ●●●● Voltage ●●●●心 Phase Loop Loop controlled ●●●0 ●Phase-locked detector amplifier filter oscillator ●●●●0 ●●●● loops Ud(t) Uc(t) Output ●●●● 听% ●● Reference oscillator Frequency divider ÷W VCO 6=217.5 LPF -222.5MHz Multiplier ●Practical 图 fou=4(-N52) ×4 synthesizer 五=7.5kHz DDS circuits BPF 斤=228.02250MHz Programmable divider 737<N<1402 detector ampuitier tilter vCO fo ●Fractional fout Reference phase-locked oscillator Divider +N loops or +(W+I) Adder/ Division accumulator ratio 2To conclude -1 Phase-locked loops Practical synthesizer circuits Fractional phase-locked loops 2