正在加载图片...

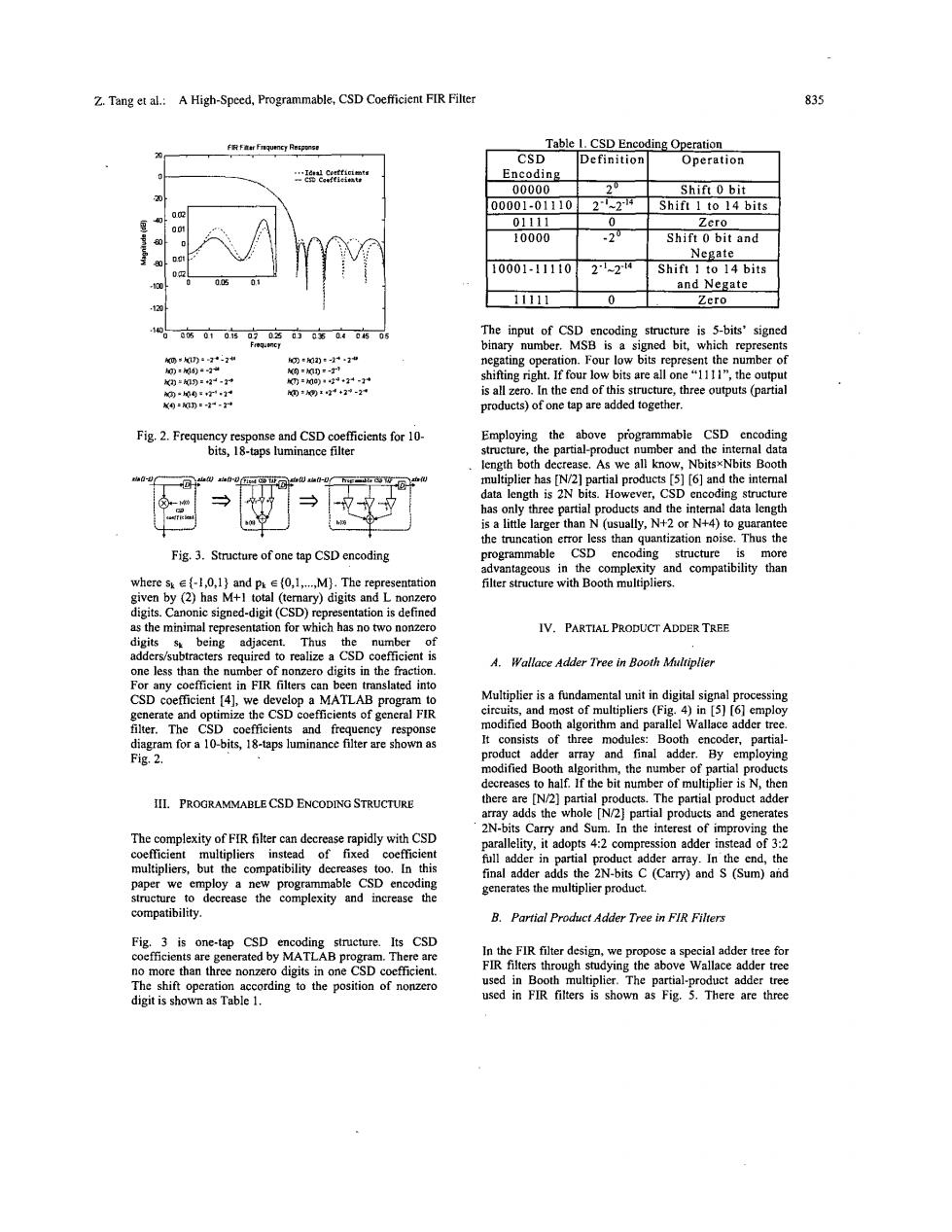

Z.Tang et al.:A High-Speed,Programmable,CSD Coefficient FIR Filter 835 Table 1.CSD Encoding Operation CSD Definition Operation "e1 Encoding 00000 20 Shift 0 bit 00001-01110 2124 Shift 1 to 14 bits 0 01111 0 Zero 10000 Shift 0 bit and Negate 10001-11110 2*124 Shift】tol4bits and Negate 11111 0 Zero og0s01is立zd由o南@4a帖05 The input of CSD encoding structure is 5-bits'signed Freqisncy binary number.MSB is a signed bit,which represents 0¥)=-72" 切02)-+7" negating operation.Four low bits represent the number of 0=00·-24 阿=00=- )=0》=+2.2* 闭=0)24,24- shifting right.If four low bits are all one"1111",the output 0=物x2*+z*-2 is all zero.In the end of this structure,three outputs (partial 9=0功=-2-2 products)of one tap are added together. Fig.2.Frequency response and CSD coefficients for 10- Employing the above programmabie CSD encoding bits,18-taps luminance filter structure,the partial-product number and the internal data length both decrease.As we all know,NbitsxNbits Booth multiplier has [N/2]partial products [5][6]and the interal data length is 2N bits.However,CSD encoding structure has only three partial products and the internal data length is a little larger than N(usually,N+2 or N+4)to guarantee the truncation error less than quantization noise.Thus the Fig.3.Structure of one tap CSD encoding programmable CSD encoding structure is more advantageous in the complexity and compatibility than where sk∈{l,0,l}and p∈{0,l,,M}.The representation filter structure with Booth multipliers given by (2)has M+I total (ternary)digits and L nonzero digits.Canonic signed-digit(CSD)representation is defined as the minimal representation for which has no two nonzero IV.PARTIAL PRODUCT ADDER TREE digits s being adjacent.Thus the number of adders/subtracters required to realize a CSD coefficient is A.Wallace Adder Tree in Booth Multiplier one less than the number of nonzero digits in the fraction. For any coefficient in FIR filters can been translated into CSD coefficient [4],we develop a MATLAB program to Multiplier is a fundamental unit in digital signal processing generate and optimize the CSD coefficients of general FIR circuits,and most of multipliers (Fig.4)in [5][6]employ filter.The CSD coefficients and frequency response modified Booth algorithm and parallel Wallace adder tree diagram for a 10-bits,18-taps luminance filter are shown as It consists of three modules:Booth encoder,partial- Fig.2. product adder array and final adder.By employing modified Booth algorithm,the number of partial products decreases to half.If the bit number of multiplier is N,then III.PROGRAMMABLE CSD ENCODING STRUCTURE there are [N/2]partial products.The partial product adder array adds the whole [N/2]partial products and generates The complexity of FIR filter can decrease rapidly with CSD 2N-bits Carry and Sum.In the interest of improving the parallelity,it adopts 4:2 compression adder instead of 3:2 coefficient multipliers instead of fixed coefficient full adder in partial product adder array.In the end,the multipliers,but the compatibility decreases too.In this final adder adds the 2N-bits C (Carry)and S (Sum)and paper we employ a new programmable CSD encoding generates the multiplier product. structure to decrease the complexity and increase the compatibility. B.Partial Product Adder Tree in FIR Filters Fig.3 is one-tap CSD encoding structure.Its CSD coefficients are generated by MATLAB program.There are In the FIR filter design,we propose a special adder tree for no more than three nonzero digits in one CSD coefficient. FIR filters through studying the above Wallace adder tree The shift operation according to the position of nonzero used in Booth multiplier.The partial-product adder tree digit is shown as Table 1. used in FIR filters is shown as Fig.5.There are three