正在加载图片...

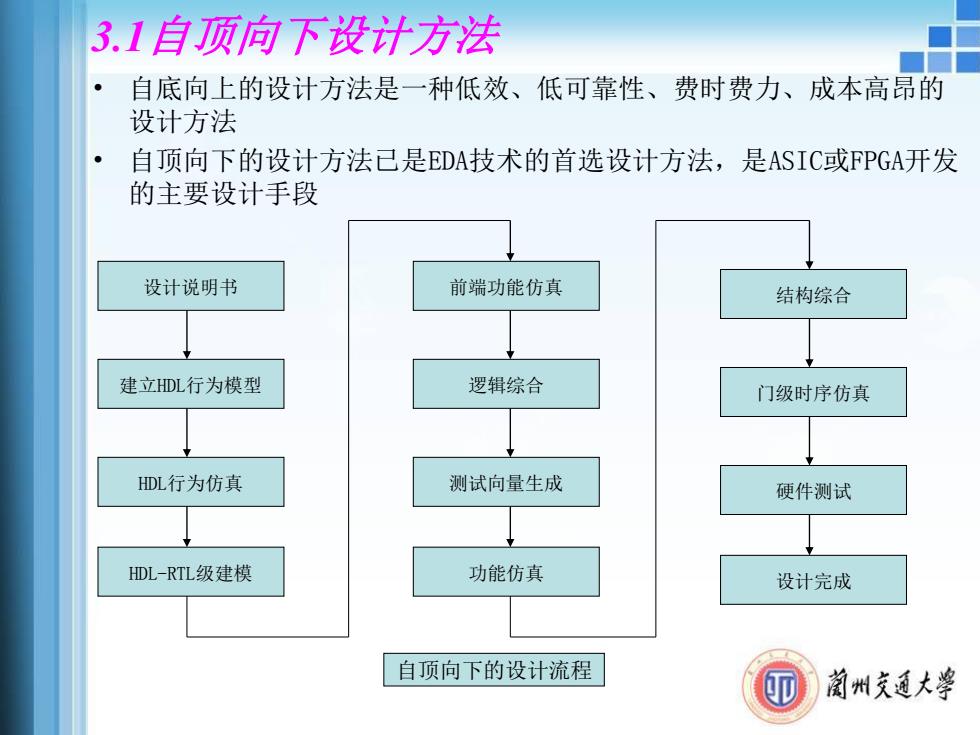

3.1自顶向下设计方法 自底向上的设计方法是一种低效、低可靠性、费时费力、成本高昂的 设计方法 自顶向下的设计方法己是EDA技术的首选设计方法,是ASIC或FPGA开发 的主要设计手段 设计说明书 前端功能仿真 结构综合 建立HDL行为模型 逻辑综合 门级时序仿真 HDL行为仿真 测试向量生成 硬件测试 HDL-RTL级建模 功能仿真 设计完成 自顶向下的设计流程 菌州克通大粤 3.1自顶向下设计方法 • 自底向上的设计方法是一种低效、低可靠性、费时费力、成本高昂的 设计方法 • 自顶向下的设计方法已是EDA技术的首选设计方法,是ASIC或FPGA开发 的主要设计手段 设计说明书 建立HDL行为模型 HDL行为仿真 HDL-RTL级建模 前端功能仿真 逻辑综合 测试向量生成 功能仿真 结构综合 门级时序仿真 硬件测试 设计完成 自顶向下的设计流程