正在加载图片...

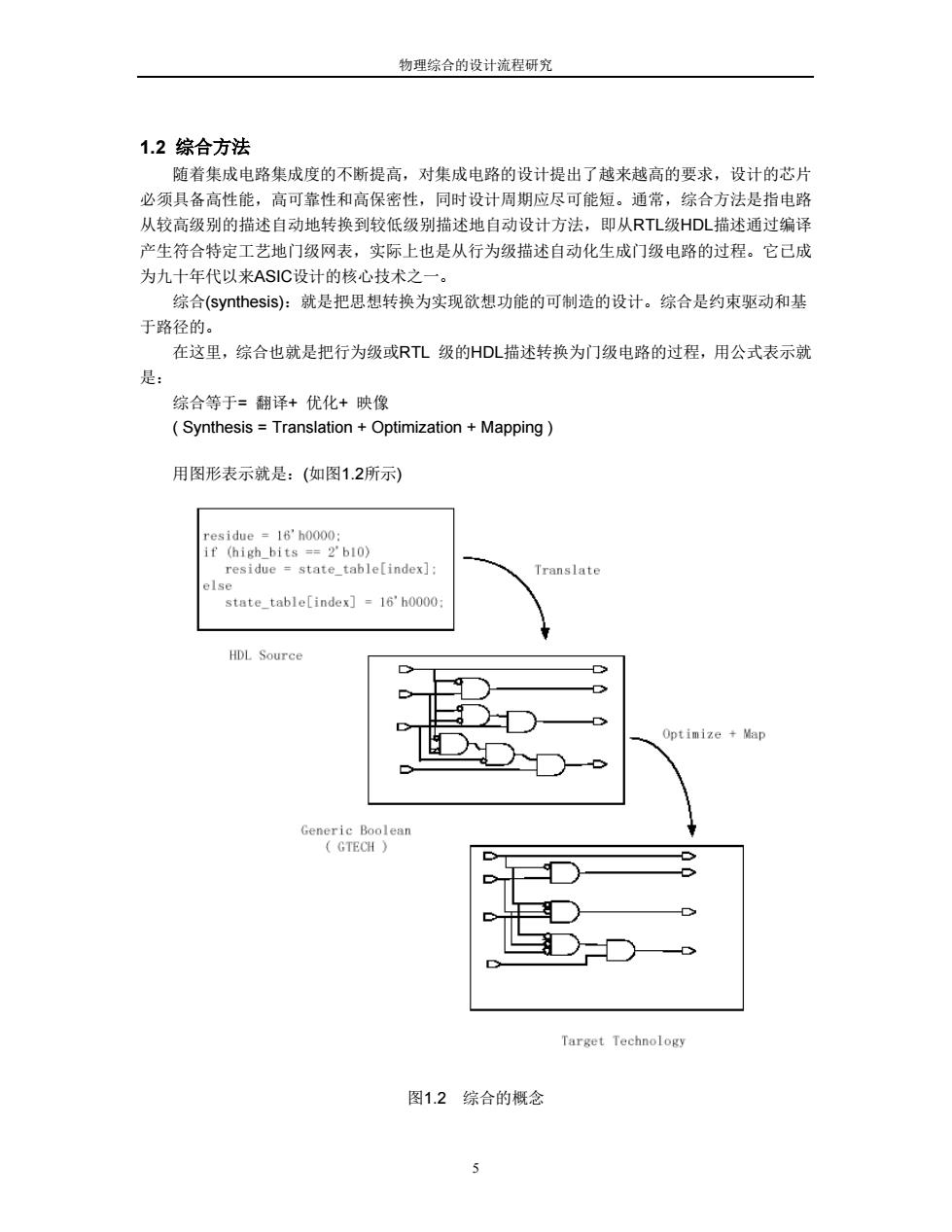

物理综合的设计流程研究 1.2综合方法 随着集成电路集成度的不断提高,对集成电路的设计提出了越来越高的要求,设计的芯片 必须具备高性能,高可靠性和高保密性,同时设计周期应尽可能短。通常,综合方法是指电路 从较高级别的描述自动地转换到较低级别描述地自动设计方法,即从RTL级HDL描述通过编译 产生符合特定工艺地门级网表,实际上也是从行为级描述自动化生成门级电路的过程。它已成 为九十年代以来ASIC设计的核心技术之一。 综合(synthesis):就是把思想转换为实现欲想功能的可制造的设计。综合是约束驱动和基 于路径的。 在这里,综合也就是把行为级或RTL级的HDL描述转换为门级电路的过程,用公式表示就 是: 综合等于=翻译+优化+映像 Synthesis=Translation Optimization Mapping 用图形表示就是:(如图1.2所示) residue 16'h0000: if (high_bits ==2'b10) residue statetable[index]: Translate else state table[index]16'h0000 HDL Source Optimize Map Generic Boolean GTECH Target Technology 图1.2综合的概念 5物理综合的设计流程研究 1.2 综合方法 随着集成电路集成度的不断提高,对集成电路的设计提出了越来越高的要求,设计的芯片 必须具备高性能,高可靠性和高保密性,同时设计周期应尽可能短。通常,综合方法是指电路 从较高级别的描述自动地转换到较低级别描述地自动设计方法,即从RTL级HDL描述通过编译 产生符合特定工艺地门级网表,实际上也是从行为级描述自动化生成门级电路的过程。它已成 为九十年代以来ASIC设计的核心技术之一。 综合(synthesis):就是把思想转换为实现欲想功能的可制造的设计。综合是约束驱动和基 于路径的。 在这里,综合也就是把行为级或RTL 级的HDL描述转换为门级电路的过程,用公式表示就 是: 综合等于= 翻译+ 优化+ 映像 ( Synthesis = Translation + Optimization + Mapping ) 用图形表示就是:(如图1.2所示) 图1.2 综合的概念 5