正在加载图片...

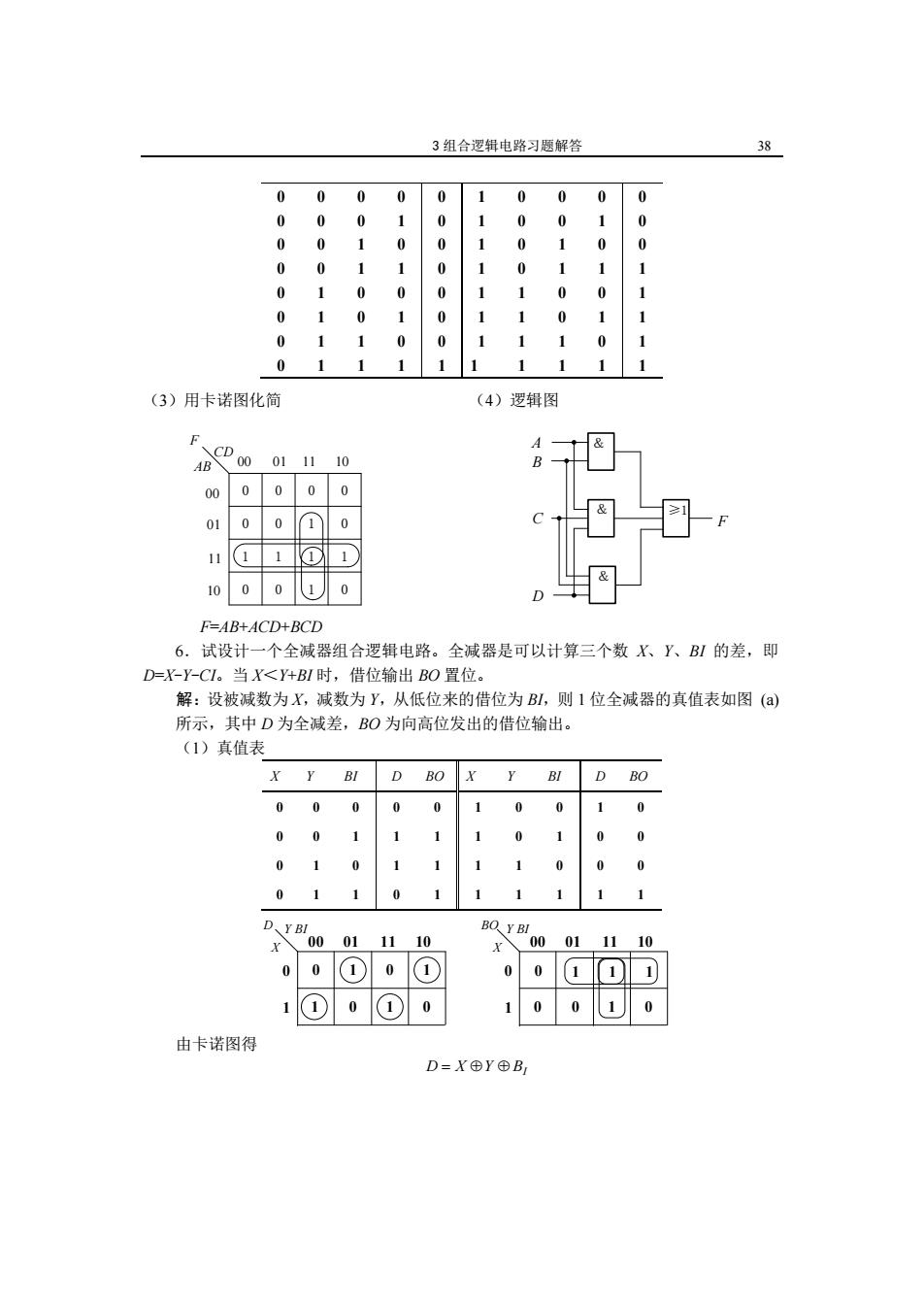

3组合逻辑电路习题解答 38 0 00 S 1 0 0 0 0 000 1 0 001 0 0 1 0 1 0 0 001 1 1 S 1 1 01 0 0 0 1 1 0 0 1 0 10 1 S 0 1 0 11 0 0 1 1 1 0 1 0 1 1 1 (3)用卡诺图化简 (4)逻辑图 F CD AB 00 01 1110 00 0 0 0 01 0 0 0 11 1 10 0 0 0 F=AB+ACD+BCD 6.试设计一个全减器组合逻辑电路。全减器是可以计算三个数X、Y、B1的差,即 D=X-Y-CI。当X<Y+BI时,借位输出BO置位。 解:设被减数为X,减数为Y,从低位来的借位为BL,则1位全减器的真值表如图() 所示,其中D为全减差,BO为向高位发出的借位输出。 (1)真值表 X Y BI D BO BI D BO 00 0 0 1 00 1 1 1 1 1 0 0 0 1 0 1 1 1 0 0 0 1 1 0 1 1 D、YBI BO Y BI 、00 0111 10 X 00 011110 0 (1) (1 0 0 1 ①0 0 1 00 10 由卡诺图得 D=X⊕Y⊕B3 组合逻辑电路习题解答 38 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 0 0 1 1 1 1 1 (3)用卡诺图化简 (4)逻辑图 AB00CD 011110 00 01 11 10 F 0 0 0 0 0 0 1 0 1 1 1 1 0 0 1 0 BC A & & ≥1 F D & BC A & & ≥1 F D & F=AB+ACD+BCD 6.试设计一个全减器组合逻辑电路。全减器是可以计算三个数 X、Y、BI 的差,即 D=X-Y-CI。当 X<Y+BI 时,借位输出 BO 置位。 解:设被减数为 X,减数为 Y,从低位来的借位为 BI,则 1 位全减器的真值表如图 (a) 所示,其中 D 为全减差,BO 为向高位发出的借位输出。 (1)真值表 X Y BI D BO X Y BI D BO 0 0 0 0 0 1 0 0 1 0 0 0 1 1 1 1 0 1 0 0 0 1 0 1 1 1 1 0 0 0 0 1 1 0 1 1 1 1 1 1 0 1 0 1 1 0 1 0 0 1 00 01 11 10 X D Y BI 0 1 1 1 0 0 1 0 0 1 00 01 11 10 X Y BI BO 由卡诺图得 D X Y BI