正在加载图片...

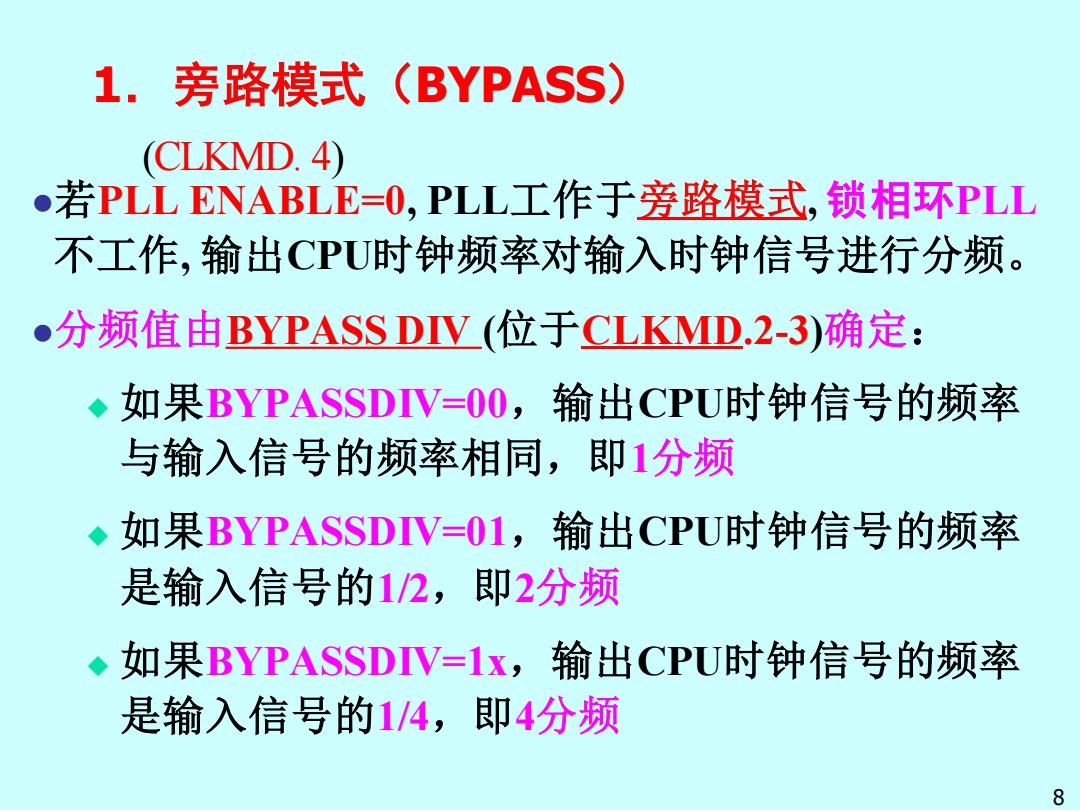

1.旁路模式(BYPASS) (CLKMD.4) 若PLL ENABLE=O,PLL工作于旁路模式,锁相环PLL 不工作,输出CPU时钟频率对输入时钟信号进行分频。 ●分频值由BYPASS DIV(位于CLKMD.2-3)确定: ◆如果BYPASSDIV=O0, 输出CPU时钟信号的频率 与输入信号的频率相同,即1分频 ◆如果BYPASSDIV=01,名 输出CPU时钟信号的频率 是输入信号的12,即2分频 ◆如果BYPASSDIV=1x,输出CPU时钟信号的频率 是输入信号的1/4,即4分频 81.旁路模式(BYPASS) ⚫若PLL ENABLE=0, PLL工作于旁路模式, 锁相环PLL 不工作, 输出CPU时钟频率对输入时钟信号进行分频。 ⚫分频值由BYPASS DIV (位于CLKMD.2-3)确定: ◆ 如果BYPASSDIV=00,输出CPU时钟信号的频率 与输入信号的频率相同,即1分频 ◆ 如果BYPASSDIV=01,输出CPU时钟信号的频率 是输入信号的1/2,即2分频 ◆ 如果BYPASSDIV=1x,输出CPU时钟信号的频率 是输入信号的1/4,即4分频 8 DSP时钟发生器 ÷ CLKDIV CPU时钟 CPU、外设、 其他器件 CLKIN CLKOUT (CLKMD. 4)