正在加载图片...

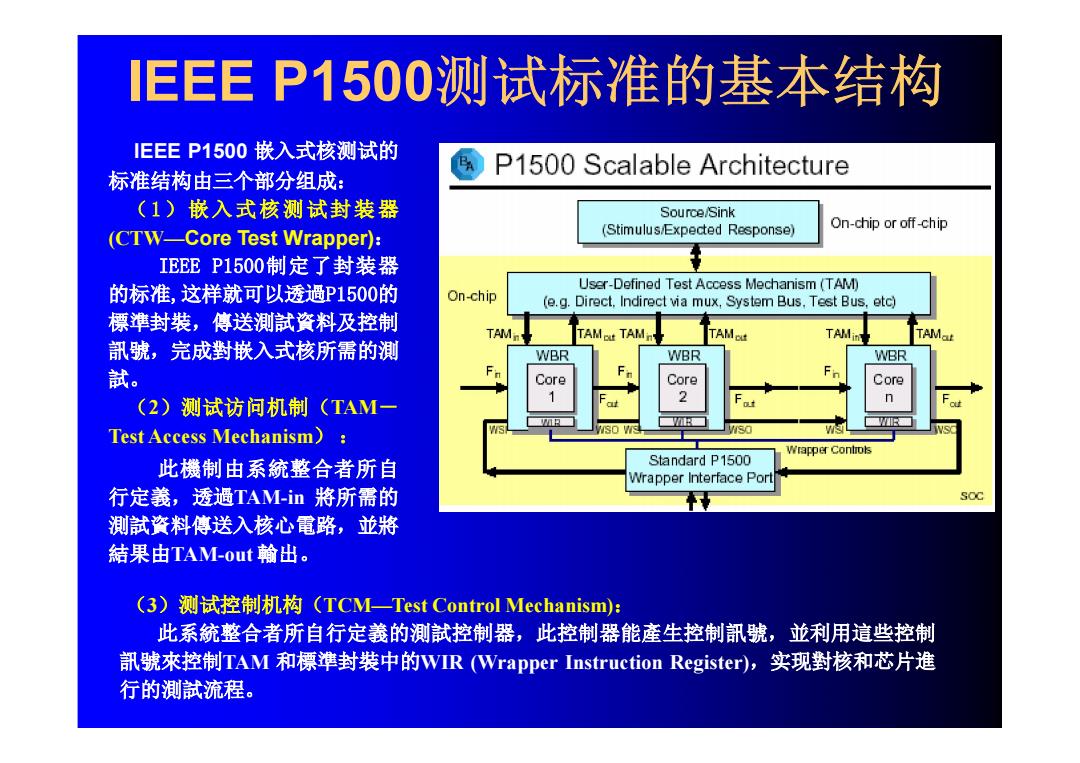

IEEE P1500测试标准的基本结构 IEEE P1500嵌入式核测试的 P1500 Scalable Architecture 标准结构由三个部分组成: (1)嵌入式核测试封装器 Source/Sink (Stimulus/Expected Response) On-chip or off-chip (CTW-Core Test Wrapper): IEEE P1500制定了封装器 的标准,这样就可以透過P1500的 User-Defined Test Access Mechanism (TAM) On-chip (e.g.Direct.Indirect via mux,System Bus.Test Bus,etc) 標準封装,停送测試资料及控制 TAM TAMTAM TAM 訊號,完成對嵌入式核所需的测 WBR WBR WBR 試。 Core Core Core 2 (2)测试访问机制(TAM一 n Test Access Mechanism): 301 此機制由系統整合者所自 Standard P1500 wrapper Interface Port 行定義,透過TAM-im将所需的 SOC 测試资料停送入核心電路,並將 結果由TAM-out輸出。 (3)测试控制机构(TCM一Test Control Mechanism): 此系統整合者所自行定義的测試控制器,此控制器能產生控制訊號,並利用這些控制 訊號來控制TAM和標準封装中的WIR(Wrapper Instruction Register),实现對核和芯片進 行的测試流程。IEEE P1500测试标准的基本结构 IEEE P1500 嵌入式核测试的 标准结构由三个部分组成: ( 1)嵌入式核测试封装器 (CTW—Core Test Wrapper): IEEE P1500制定了封装器 的标准,这样就可以透過P1500的 標準封裝,傳送測試資料及控制 訊號,完成對嵌入式核所需的測 試。 (2)测试访问机制(TAM- Test Access Mechanism) : 此機制由系統整合者所自 行定義,透過TAM-in 將所需的 測試資料傳送入核心電路,並將 結果由TAM-out 輸出。 (3)测试控制机构(TCM—Test Control Mechanism): 此系統整合者所自行定義的測試控制器,此控制器能產生控制訊號,並利用這些控制 訊號來控制TAM 和標準封裝中的WIR (Wrapper Instruction Register),实现對核和芯片進 行的測試流程