正在加载图片...

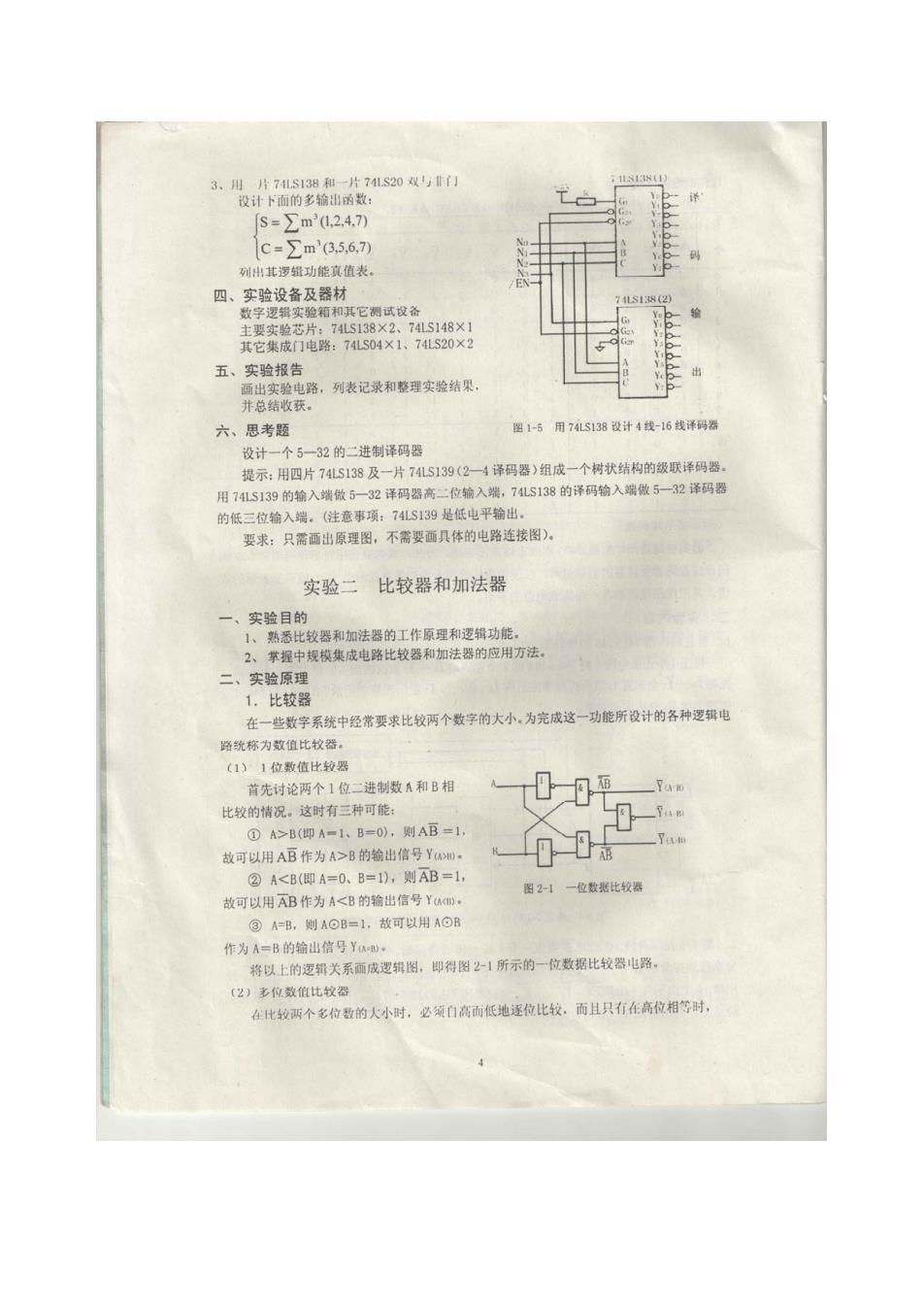

3、用片71S138和一片741S20双与门 设计下面的多输出函数: s=∑m'1.24.刀 C=∑m'(35,6,7) 列出其逻辑功能真值表, 四、实验设备及器材 数字逻辑实验箱和其它测试设备 主要实验芯片:74LS138×2、741S148×1 其它集成门电路:74LS04×1、74LS20×2 五、实验报告 画出实验电路,列表记录和整理实验结果。 并总结收获。 六、思考题 图1-5用74LS138设计4线-16线译码器 设计一个5一32的二进制译码器 提示:用四片741S138及一片741S139(2一4译码器)组成一个树状结构的级联译码器。 用74S139的输入端做5一32译码器高二位输入端,74S138的译码输入端做5一32译码器 的低三位输入端。(注意事项:74LS139是低电平输出。 要求:只需画出原理图,不需要画具体的电路连接图)。 实验二比较器和加法器 一、实验目的 1、熟悉比较器和加法器的工作原理和逻辑功能。 2、掌握中规模集成电路比较器和加法器的应用方法, 二、实验原理 1.比较器 在一些数字系统中经常要求比较两个数字的大小,为完成这一功能所设计的各种逻辑电 路统称为数值比较器 (1)1位数值比较器 首先讨论两个1位二进制数A和B相 比较的情况。这时有三种可能: ①A>B(即A-1、B=0),则AB=1 故可以用AB作为A>B的输出信号Y: ②A<B(即A=0、B=1),则AB=1, 图2-1一位数据比较器 故可以用AB作为A<B的输出信号Ya, ③A=B,则A⊙B=1,故可以用A⊙B 作为A=B的输出信号YA:D, 将以上的逻辑关系画成逻辑图,即得图21所示的一位数据比较器电路 (2)多位数值比较器 在比较两个多位数的大小时,必须自高而低地逐位比纹,而且只有在高位相等时