正在加载图片...

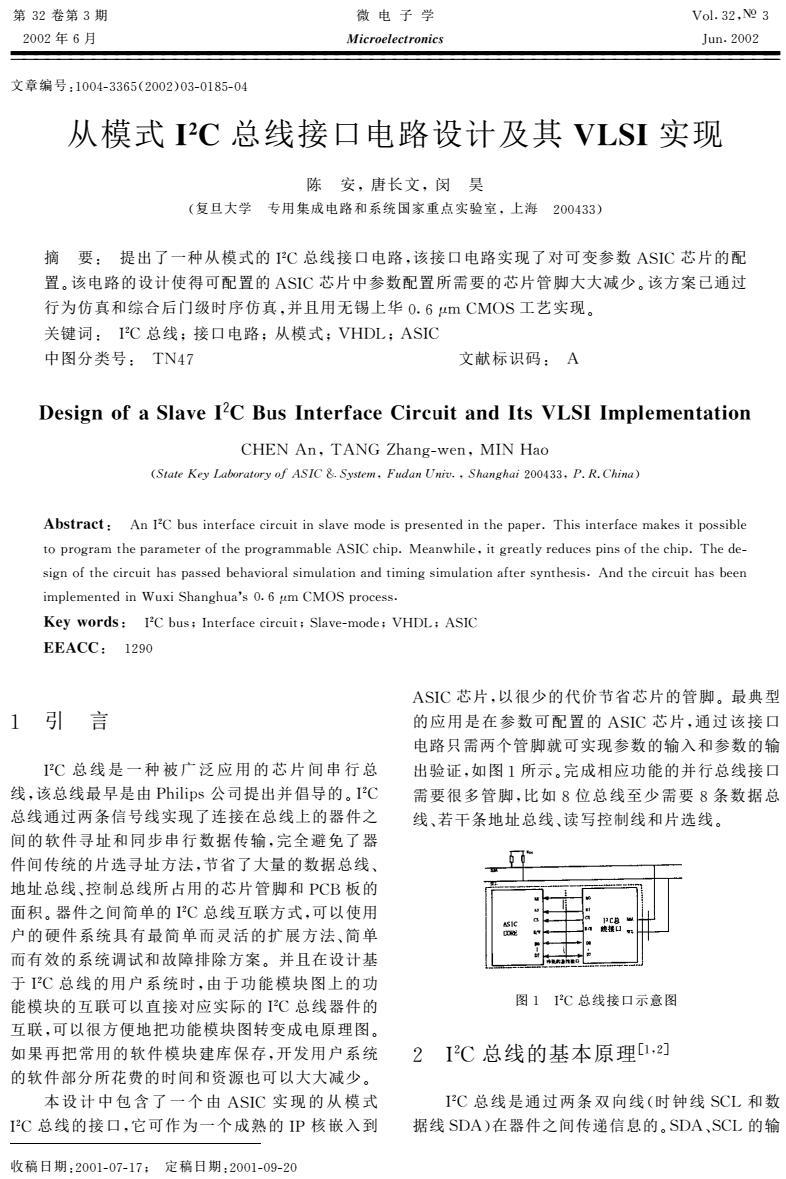

第32卷第3期 微电子学 Vol.32,N9 3 2002年6月 Microelectronics Jun.2002 文章编号:1004-3365(2002)03-0185-04 从模式I2C总线接口电路设计及其VLSI实现 陈安,唐长文,闵昊 (复旦大学专用集成电路和系统国家重点实验室,上海200433) 摘要:提出了一种从模式的I2C总线接口电路,该接口电路实现了对可变参数ASIC芯片的配 置。该电路的设计使得可配置的ASIC芯片中参数配置所需要的芯片管脚大大减少。该方案已通过 行为仿真和综合后门级时序仿真,并且用无锡上华0.6μm CMOS工艺实现。 关键词:I2C总线;接口电路;从模式;VHDL:ASIC 中图分类号:TN47 文献标识码:A Design of a Slave I2C Bus Interface Circuit and Its VLSI Implementation CHEN An,TANG Zhang-wen,MIN Hao (State Key Laboratory of ASIC &System,Fudan Univ.Shanghai 200433,P.R.China) Abstract:An IC bus interface circuit in slave mode is presented in the paper.This interface makes it possible to program the parameter of the programmable ASIC chip.Meanwhile,it greatly reduces pins of the chip.The de- sign of the circuit has passed behavioral simulation and timing simulation after synthesis.And the circuit has been implemented in Wuxi Shanghua's 0.6 um CMOS process. Key words:IC bus;Interface circuit Slave-mode:VHDL:ASIC EEACC:1290 ASIC芯片,以很少的代价节省芯片的管脚。最典型 1引言 的应用是在参数可配置的ASIC芯片,通过该接口 电路只需两个管脚就可实现参数的输入和参数的输 I2C总线是一种被广泛应用的芯片间串行总 出验证,如图1所示。完成相应功能的并行总线接口 线,该总线最早是由Philips公司提出并倡导的。I2C 需要很多管脚,比如8位总线至少需要8条数据总 总线通过两条信号线实现了连接在总线上的器件之 线、若干条地址总线、读写控制线和片选线。 间的软件寻址和同步串行数据传输,完全避免了器 件间传统的片选寻址方法,节省了大量的数据总线、 地址总线、控制总线所占用的芯片管脚和PCB板的 面积。器件之间简单的12C总线互联方式,可以使用 ASIC 户的硬件系统具有最简单而灵活的扩展方法、简单 能接口好 而有效的系统调试和故障排除方案。并且在设计基 作的 于I2C总线的用户系统时,由于功能模块图上的功 能模块的互联可以直接对应实际的I2℃总线器件的 图112C总线接口示意图 互联,可以很方便地把功能模块图转变成电原理图。 如果再把常用的软件模块建库保存,开发用户系统 2I2C总线的基本原理[1,2] 的软件部分所花费的时间和资源也可以大大减少。 本设计中包含了一个由ASIC实现的从模式 I2C总线是通过两条双向线(时钟线SCL和数 I2C总线的接口,它可作为一个成熟的IP核嵌入到 据线SDA)在器件之间传递信息的。SDA、SCL的输 收稿日期:2001-07-17;定稿日期:2001-09-20收稿日期!"##$%#&%$&’ 定稿日期!"##$%#(%"# 文章编号!$##)%**+,-"##".#*%#$/,%#) 从模式 0 1 2总线接口电路设计及其 3450实现 陈 安6唐长文6闵 昊 -复旦大学 专用集成电路和系统国家重点实验室6上海 "##)**. 摘 要! 提出了一种从模式的 7 " 8总线接口电路6该接口电路实现了对可变参数 9:78芯片的配 置;该电路的设计使得可配置的 9:78芯片中参数配置所需要的芯片管脚大大减少;该方案已通过 行为仿真和综合后门级时序仿真6并且用无锡上华 #<+=> 8?@:工艺实现; 关键词! 7 " 8总线’接口电路’从模式’ABCD’9:78 中图分类号! EF)& 文献标识码! 9 GHIJKLMNO5POQH0R 2STI0LUHVNOWH2JVWTJUOLX0UI34500YZPHYHLUOUJML 8B[F 9\6E9F]^_‘\a%bc\6?7F B‘d -efgfhihjkglmngfmnjmopeqrsejtfhu6vwxgyzy{|<6e}gy~}g{"##)**6!"#"r}{yg. $%IUVOWU! 9\7" 8&’()\*c+,‘-c-)+-’)*)\(.‘/c>d0c)(1+c(c\*c0)\*_c1‘1c+<E_)()\*c+,‘-c>‘2c()*1d(()&.c *d1+da+‘> *_c1‘+‘>c*c+d,*_c1+da+‘>>‘&.c9:78-_)1<?c‘\b_).c6)*a+c‘*.3+c0’-c(1)\(d,*_c-_)1<E_c0c% ()a\d,*_c-)+-’)*_‘(1‘((c0&c_‘/)d+‘.()>’.‘*)d\‘\0*)>)\a()>’.‘*)d\‘,*c+(3\*_c()(<9\0*_c-)+-’)*_‘(&cc\ )>1.c>c\*c0)\4’5):_‘\a_’‘6(#<+=> 8?@:1+d-c((< 7H89MVXI! 7 " 8&’(’7\*c+,‘-c-)+-’)*’:.‘/c%>d0c’ABCD’9:78 ::$22! $"(# $ 引 言 7 " 8总 线 是 一 种 被 广 泛 应 用 的 芯 片 间 串 行 总 线6该总线最早是由 ;_).)1(公司提出并倡导的;7 " 8 总线通过两条信号线实现了连接在总线上的器件之 间的软件寻址和同步串行数据传输6完全避免了器 件间传统的片选寻址方法6节省了大量的数据总线< 地址总线<控制总线所占用的芯片管脚和 ;8=板的 面积;器件之间简单的 7 " 8总线互联方式6可以使用 户的硬件系统具有最简单而灵活的扩展方法<简单 而有效的系统调试和故障排除方案;并且在设计基 于 7 " 8总线的用户系统时6由于功能模块图上的功 能模块的互联可以直接对应实际的 7 " 8总线器件的 互联6可以很方便地把功能模块图转变成电原理图; 如果再把常用的软件模块建库保存6开发用户系统 的软件部分所花费的时间和资源也可以大大减少; 本 设 计 中 包 含 了 一 个 由 9:78实 现 的 从 模 式 7 " 8总线的接口6它可作为一个成熟的 7;核嵌入到 9:78芯片6以很少的代价节省芯片的管脚;最典型 的应用是在参数可配置的 9:78芯片6通过该接口 电路只需两个管脚就可实现参数的输入和参数的输 出验证6如图 $所示;完成相应功能的并行总线接口 需要很多管脚6比如 /位总线至少需要 /条数据总 线<若干条地址总线<读写控制线和片选线; 图 $ 7 " 8总线接口示意图 " 7 " 8总线的基本原理>$6"? 7 " 8总线是通过两条双向线-时钟线 :8D和数 据线 :C9.在器件之间传递信息的;:C9<:8D的输 第 *"卷第 *期 "##"年 +月 微 电 子 学 @ABCDEFEBGCDHABI Ad.<*"6J * K’\ LLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLL <"##