正在加载图片...

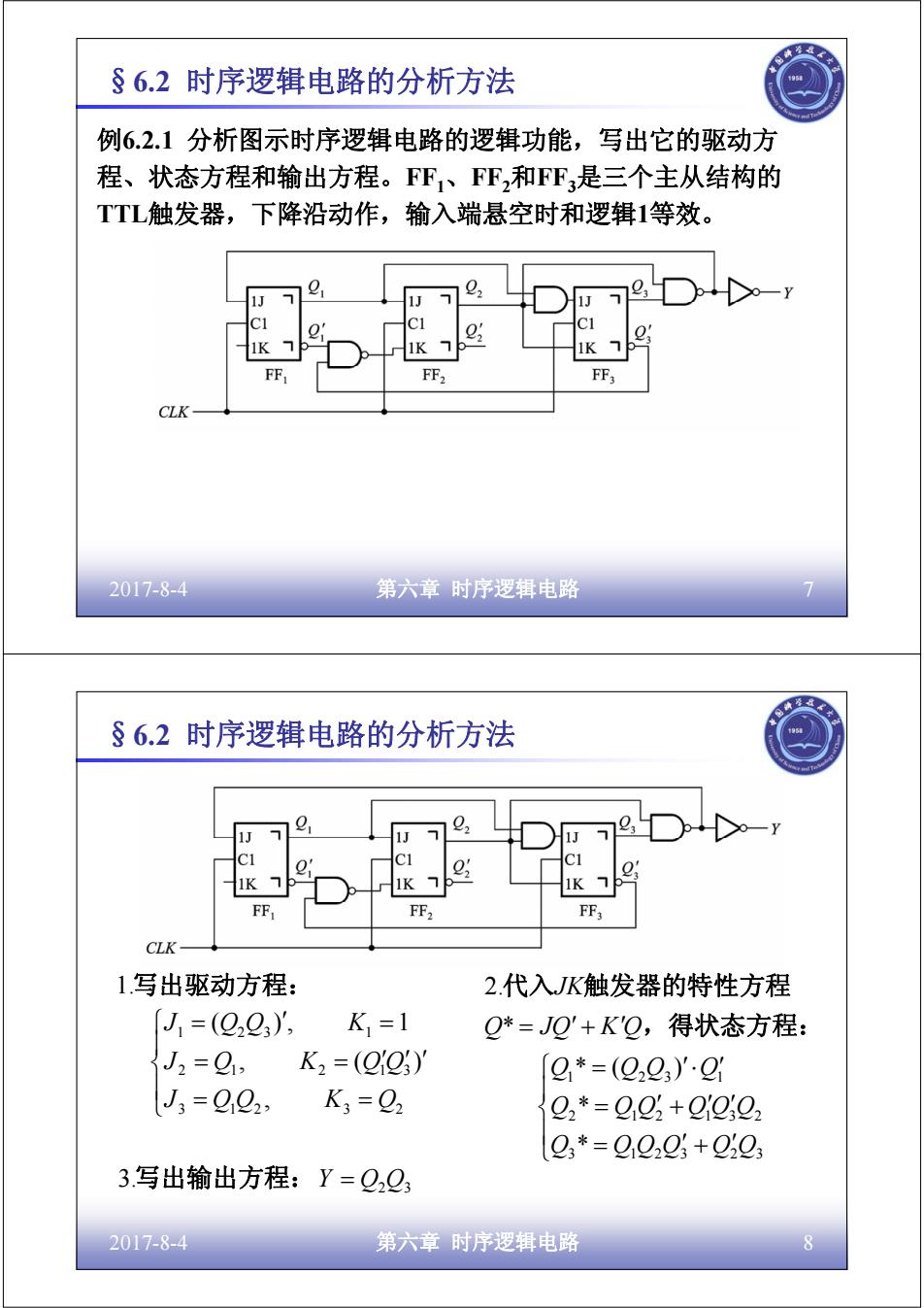

§6.2时序逻辑电路的分析方法 例6.2.1分析图示时序逻辑电路的逻辑功能,写出它的驱动方 程、状态方程和输出方程。FF、FF,和FF,是三个主从结构的 TTL触发器,下降沿动作,输入端悬空时和逻辑1等效。 1K7 FF FF. FF CLK 2017-8-4 第六章时序逻辑电路 §6.2时序逻辑电路的分析方法 0 1K7 FF, FF, CLK 1写出驱动方程: 2.代入JK触发器的特性方程 J1=(9223), K=1 Q*=JQ'+KQ,得状态方程: J2=Q, K2=(gO)1 Q*=(932)'·Q J3=Q02, K,=Q2 92*=9Q2+Q00 Q3*=QQ2Q3+Q30 3.写出输出方程:Y=Q2Q3 2017-8-4 第六章时序逻辑电路 82017-8-4 第六章 时序逻辑电路 7 §6.2 时序逻辑电路的分析方法 例6.2.1 分析图示时序逻辑电路的逻辑功能,写出它的驱动方 程、状态方程和输出方程。FF1、FF2和FF3是三个主从结构的 TTL触发器,下降沿动作,输入端悬空时和逻辑1等效。 2017-8-4 第六章 时序逻辑电路 8 §6.2 时序逻辑电路的分析方法 1.写出驱动方程: ⎪ ⎩ ⎪ ⎨ ⎧ = = = = ′ ′ ′ = ′ = 3 1 2 3 2 2 1 2 1 3 1 2 3 1 , , ( ) ( ) , 1 J Q Q K Q J Q K Q Q J Q Q K ,得状态方程: 代入 触发器的特性方程 Q JQ K Q JK * = ′ + ′ 2. ⎪ ⎩ ⎪ ⎨ ⎧ = ′ + ′ = ′ + ′ ′ = ′⋅ ′ 3 1 2 3 2 3 2 1 2 1 3 2 1 2 3 1 * * * ( ) Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q 2 3 3.写出输出方程:Y = Q Q