正在加载图片...

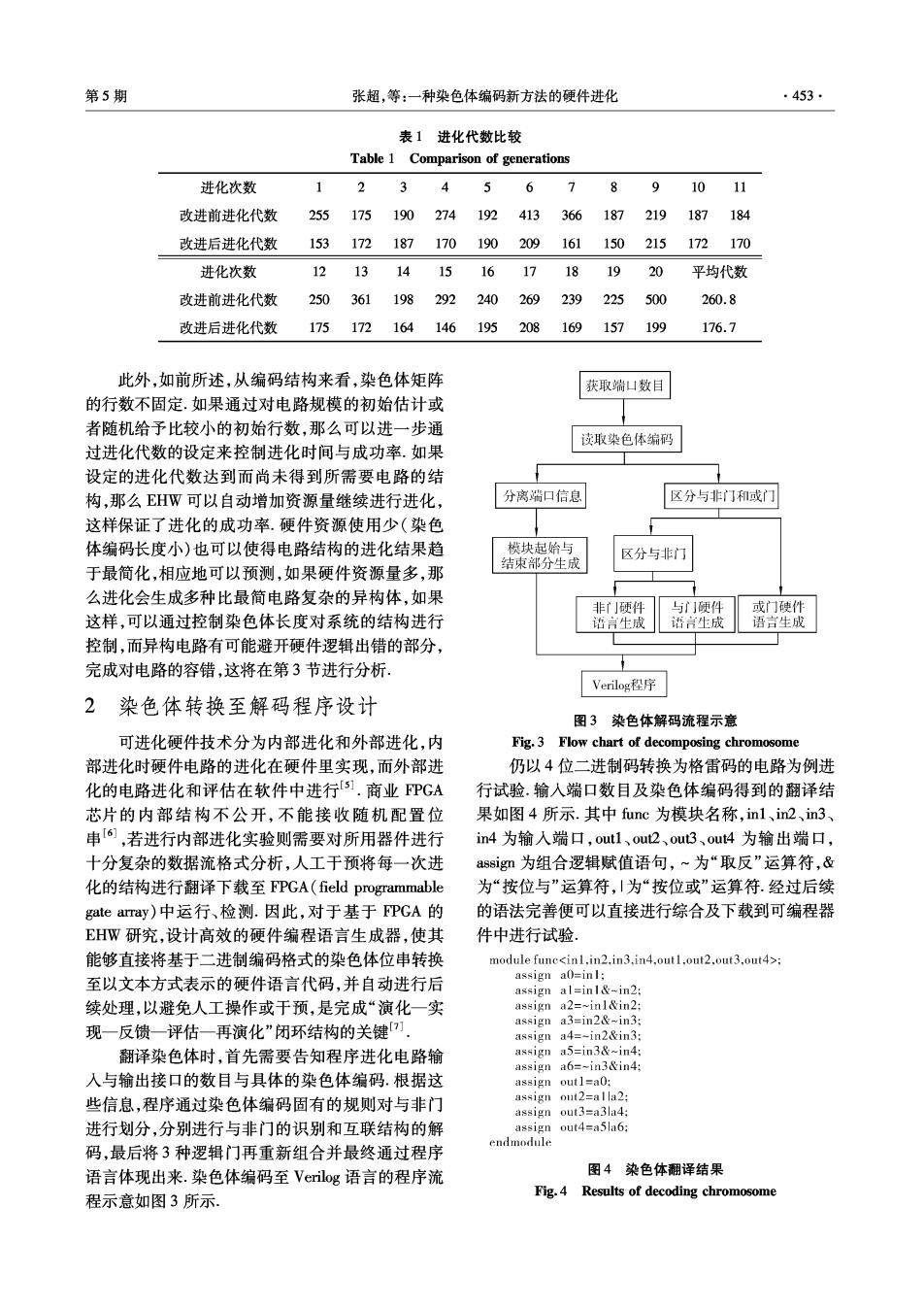

第5期 张超,等:一种染色体编码新方法的硬件进化 ·453· 表1进化代数比较 Table 1 Comparison of generations 进化次数 3 4 5 67 8910 11 改进前进化代数 255 175190274192413366187219187184 改进后进化代数 153 172 187170 190209 161150 215 172170 进化次数 12 13 14 15 16 17 18 19 20 平均代数 改进前进化代数 250361198 292240 269 239 225 500 260.8 改进后进化代数 175172164146195 208 169 157 199 176.7 此外,如前所述,从编码结构来看,染色体矩阵 获取端凵数目 的行数不固定.如果通过对电路规模的初始估计或 者随机给予比较小的初始行数,那么可以进一步通 读取染色体编码 过进化代数的设定来控制进化时间与成功率.如果 设定的进化代数达到而尚未得到所需要电路的结 构,那么EHW可以自动增加资源量继续进行进化, 分离瑞口信息 区分与非门和或门 这样保证了进化的成功率.硬件资源使用少(染色 体编码长度小)也可以使得电路结构的进化结果趋 模块起始与 区分与非门 结束部分生成 于最简化,相应地可以预测,如果硬件资源量多,那 么进化会生成多种此最简电路复杂的异构体,如果 非门硬件 与]硬件 或门使件 这样,可以通过控制染色体长度对系统的结构进行 语言生成 话言生成 语言生成 控制,而异构电路有可能避开硬件逻辑出错的部分, 完成对电路的容错,这将在第3节进行分析。 Verilog程序 2染色体转换至解码程序设计 图3染色体解码流程示意 可进化硬件技术分为内部进化和外部进化,内 Fig.3 Flow chart of decomposing chromosome 部进化时硬件电路的进化在硬件里实现,而外部进 仍以4位二进制码转换为格雷码的电路为例进 化的电路进化和评估在软件中进行51.商业PGA 行试验.输入端口数目及染色体编码得到的翻译结 芯片的内部结构不公开,不能接收随机配置位 果如图4所示.其中func为模块名称,inl、in2、in3、 串6),若进行内部进化实验则需要对所用器件进行 in4为输人端口,out1、out2、ou3、out4为输出端口, 十分复杂的数据流格式分析,人工干预将每一次进 assign为组合逻辑赋值语句,~为“取反”运算符,& 化的结构进行翻译下载至FPGA(field programmable 为“按位与”运算符,|为“按位或”运算符.经过后续 gate array)中运行、检测.因此,对于基于FPGA的 的语法完善便可以直接进行综合及下载到可编程器 EHW研究,设计高效的硬件编程语言生成器,使其 件中进行试验: 能够直接将基于二进制编码格式的染色体位串转换 module func<inl.in2.in3.in4,out1.out2,out3.out4>: 至以文本方式表示的硬件语言代码,并自动进行后 assign a0=inl: assign al=in1&-in2: 续处理,以避免人工操作或干预,是完成“演化一实 assign a2=~inl&in2: 现一反馈一评估一再演化”闭环结构的关键可 assign a3=in2&~in3: assign a4=-in2&in3: 翻译染色体时,首先需要告知程序进化电路输 assign a5=in3&~in4: assign a6=-in3&in4; 入与输出接口的数目与具体的染色体编码.根据这 assign outl=a0; 些信息,程序通过染色体编码固有的规则对与非门 assign out2=alla2: assign out3=a3la4: 进行划分,分别进行与非门的识别和互联结构的解 assign out4=a5la6; endmodule 码,最后将3种逻辑门再重新组合并最终通过程序 语言体现出来.染色体编码至Verilog语言的程序流 图4染色体翻译结果 程示意如图3所示 Fig.4 Results of decoding chromosome