正在加载图片...

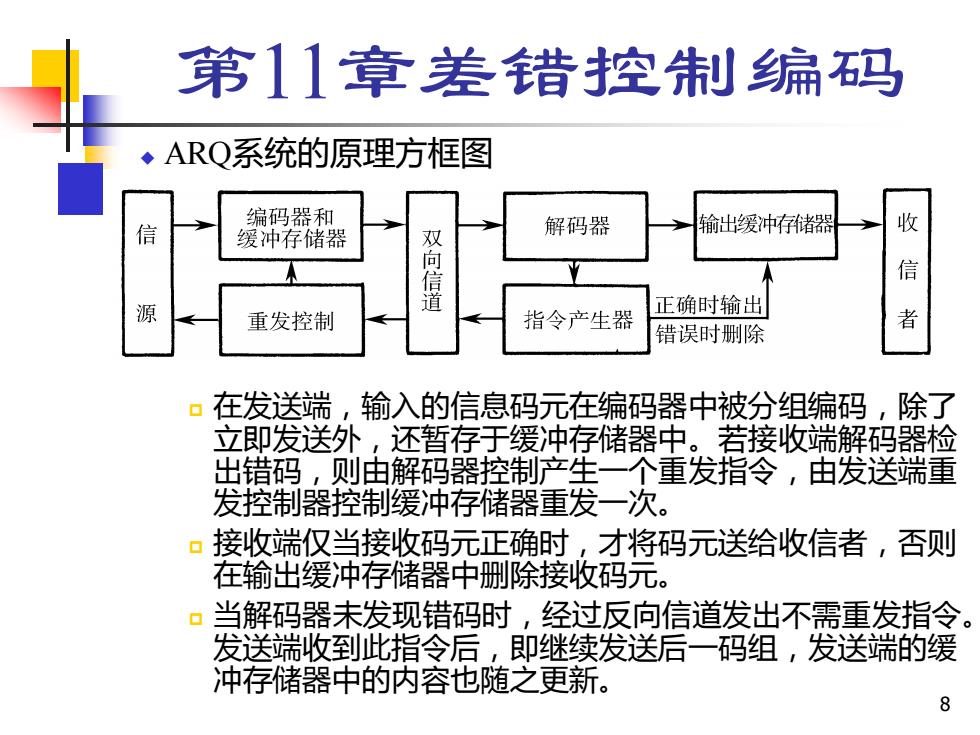

第1】章差错控制编玛 ◆ARQ系统的原理方框图 编码器和 信 输出缓冲存储器 收 缓冲存储器 解码器 向信道 信 源 正确时输出 重发控制 指令产生器 者 错误时删除 在发送端,输入的信息码元在编码器中被分组编码,除了 立即发送外,还暂存于缓冲存储器中。若接收端解码器检 出错码,则由解码器控制产生一个重发指令,由发送端重 发控制器控制缓冲存储器重发一次。 ▣接收端仅当接收码元正确时,才将码元送给收信者,否则 在输出缓冲存储器中删除接收码元。 当解码器未发现错码时,经过反向信道发出不需重发指令。 发送端收到此指令后,即继续发送后一码组,发送端的缓 冲存储器中的内容也随之更新。 8 8 第11章差错控制编码 ◆ ARQ系统的原理方框图 在发送端,输入的信息码元在编码器中被分组编码,除了 立即发送外,还暂存于缓冲存储器中。若接收端解码器检 出错码,则由解码器控制产生一个重发指令,由发送端重 发控制器控制缓冲存储器重发一次。 接收端仅当接收码元正确时,才将码元送给收信者,否则 在输出缓冲存储器中删除接收码元。 当解码器未发现错码时,经过反向信道发出不需重发指令。 发送端收到此指令后,即继续发送后一码组,发送端的缓 冲存储器中的内容也随之更新