正在加载图片...

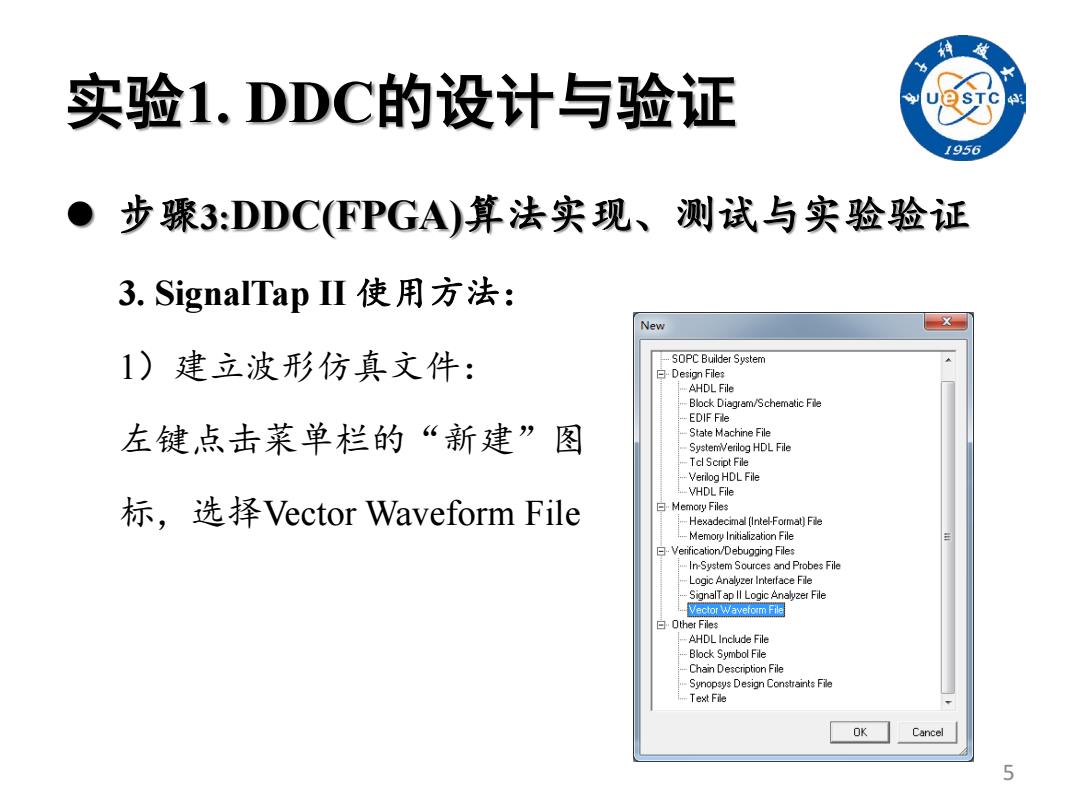

实验1.DDC的设计与验证 L956 步骤3:DDC(FPGA)算法实现、测试与实验验证 3.SignalTapⅡ使用方法: New 1)建立波形仿真文件: SOPC Builder System ▣-Design Files AHDL File Block Diagram/Schematic File EDIF Fle 左键点击菜单栏的“新建”图 State Machine File SystemVerilog HDL File Tcl Script File -Veriloo HDL File VHDL File 标,选择Vector Waveform File ▣.Memory Files Hexadecimal (Intel-Format]File .-Memory Initialization File Verification/Debugging Files In-System Sources and Probes File Logic Analyzer Interface File SignalTap ll Logic Analyzer File Vector Wayeform File ▣.Other Files -AHDL Include File Block Symbol File Chain Description File Synopsys Design Constraints File Text File OK Cancel 55 步骤3:DDC(FPGA)算法实现、测试与实验验证 3. SignalTap II 使用方法: 1)建立波形仿真文件: 左键点击菜单栏的“新建”图 标,选择Vector Waveform File 实验1. DDC的设计与验证