实验1.DDC的设计与验证 1956 。实验1设计任务: 将中频频率为f6的中频正弦信号经AD采样后下变频到0.1MHz 并将数据率降到400Ksps; 中频频率范围[10.2MHz:0.1MHz:12.1MHz],根据实验小 组序号选择设计的频点,如第1组,选择1号频点f0,=102MHz 第20组,选择20号频点:,=12.1MHz 参考步骤1和步骤2,完成设计的前两个步骤。(3学时) 2

2 实验1设计任务: 将中频频率为 的中频正弦信号经A/D采样后下变频到 , 并将数据率降到 ; 中频频率范围 ,根据实验小 组序号选择设计的频点,如第1组,选择1号频点 第20组,选择20号频点: 参考步骤1和步骤2,完成设计的前两个步骤。(3学时) 0f [10.2MHz : 0.1MHz : 12.1MHz] 0.1MHz 400Ksps 1 f0 =10.2MHz 20 f0 =12.1MHz 实验1. DDC的设计与验证

实验1.DDC的设计与验证 1956 实验步骤 √步骤1:设计具体的DDC实现结构与系统工作参数 √步骤2:利用MATLAB进行DDC模块设计仿真与验证 √步骤3:DDC(FPGA)算法实现、测试与实验验证 3

3 实验步骤 步骤1:设计具体的DDC实现结构与系统工作参数 步骤2:利用MATLAB进行DDC模块设计仿真与验证 步骤3:DDC(FPGA)算法实现、测试与实验验证 实验1. DDC的设计与验证

实验1.DDC的设计与验证 Tc 1956 实验步骤 步骤3:DDC(FPGA)算法实现、测试与实验验证 √QuartusIⅡ使用指南 √用QuartusIⅡ自带IP核辅助实现设计 √利用SignalTap IⅡ进行时序仿真与测试的方法 √硬件模块功能实现与测试 4

4 实验步骤 步骤3: DDC (FPGA) 算法实现、测试与实验验证 QuartusII 使用指南 用 QuartusII 自带IP核辅助实现设计 利用SignalTap II 进行时序仿真与测试的方法 硬件模块功能实现与测试 实验1. DDC的设计与验证

实验1.DDC的设计与验证 L956 步骤3:DDC(FPGA)算法实现、测试与实验验证 3.SignalTapⅡ使用方法: New 1)建立波形仿真文件: SOPC Builder System ▣-Design Files AHDL File Block Diagram/Schematic File EDIF Fle 左键点击菜单栏的“新建”图 State Machine File SystemVerilog HDL File Tcl Script File -Veriloo HDL File VHDL File 标,选择Vector Waveform File ▣.Memory Files Hexadecimal (Intel-Format]File .-Memory Initialization File Verification/Debugging Files In-System Sources and Probes File Logic Analyzer Interface File SignalTap ll Logic Analyzer File Vector Wayeform File ▣.Other Files -AHDL Include File Block Symbol File Chain Description File Synopsys Design Constraints File Text File OK Cancel 5

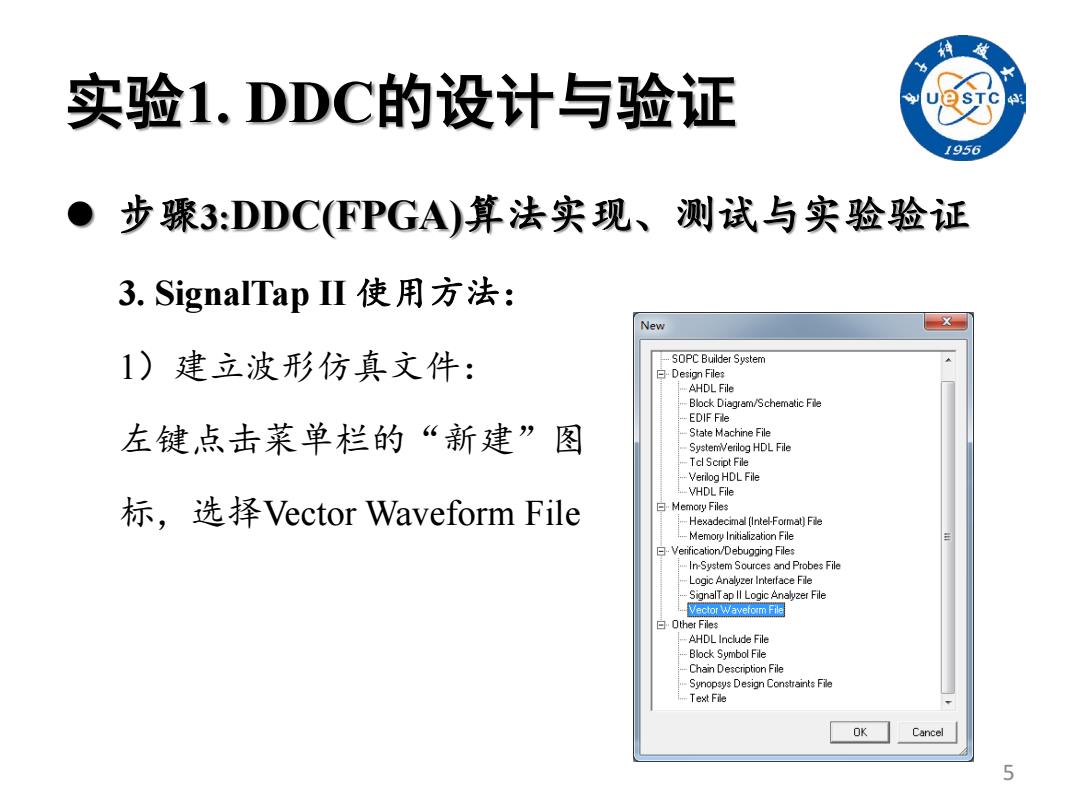

5 步骤3:DDC(FPGA)算法实现、测试与实验验证 3. SignalTap II 使用方法: 1)建立波形仿真文件: 左键点击菜单栏的“新建”图 标,选择Vector Waveform File 实验1. DDC的设计与验证

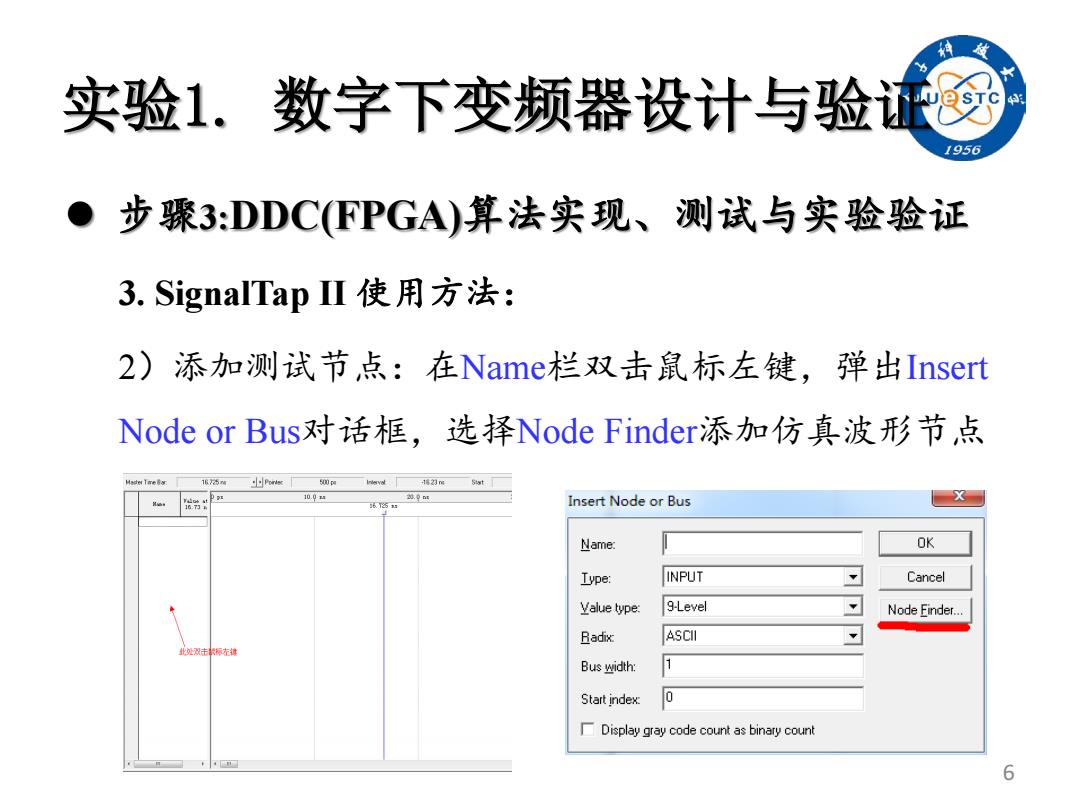

实验1.数字下变频器设计与验证 1956 步骤3:DDC(FPGA)算法实现、测试与实验验证 3.SignalTapⅡ使用方法: 2)添加测试节点:在Name栏双击鼠标左键,弹出Insert Node or Bus对话框,选择Node Finder添加仿真波形节点 500 10.0 Insert Node or Bus X Name: OK Iype: INPUT Cancel Value type: 9-Level Node Finder... Radix: ASCII 此处双击长标本键 Bus width: Start index: 0 Display gray code count as binary count 6

实验1. 数字下变频器设计与验证 6 步骤3:DDC(FPGA)算法实现、测试与实验验证 3. SignalTap II 使用方法: 2)添加测试节点:在Name栏双击鼠标左键,弹出Insert Node or Bus对话框,选择Node Finder添加仿真波形节点

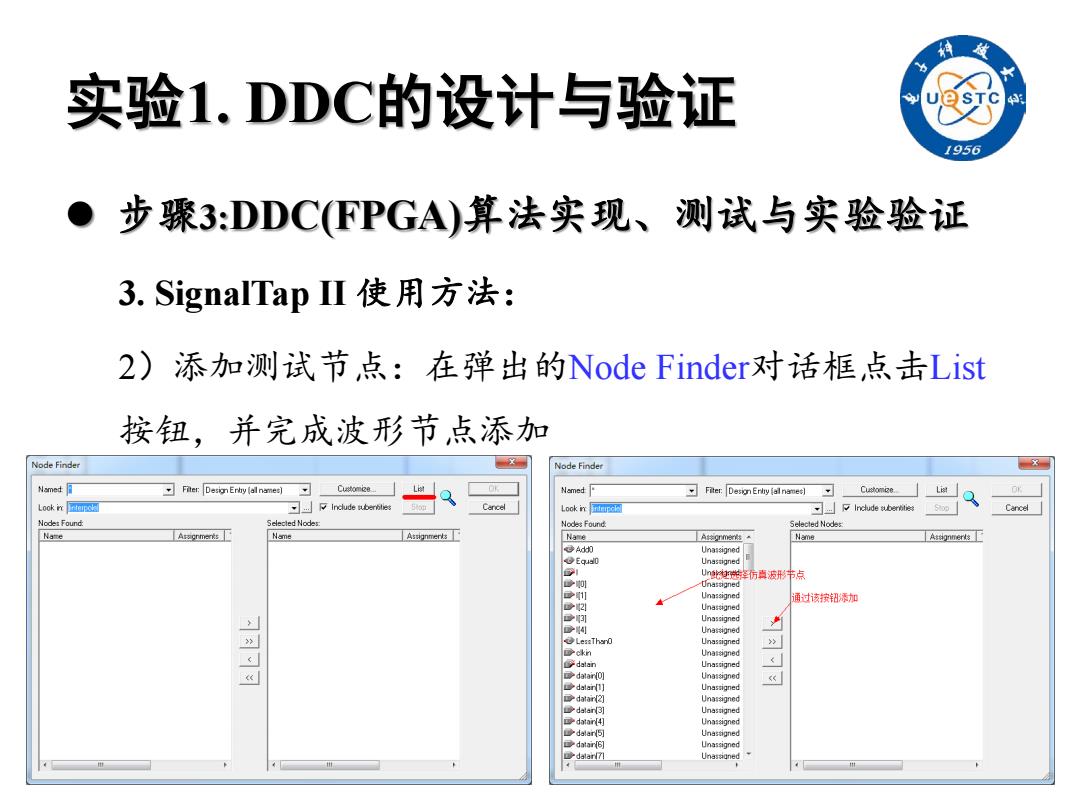

实验1.DDC的设计与验证 L956 步骤3:DDC(FPGA)算法实现、测试与实验验证 3.SignalTapⅡ使用方法: 2)添加测试节,点:在弹出的Node Finder对话框,点击List 按钮,并完成波形节点添加 Node Finder Node Finder Named Fiter:Desin Erly (al names) Customize L Named Fiter:Desion Erlry (al namee] L Look ix s 习Include 55 Look in图 。7 Include beities 30 Cancel Node:Found: Selected Nodes Nodes Found Selected Nodes A2 orments工 Name Assignmerts Name A9nmet” Name Assignmer格冒 Unaisigned Equso Unastigned 1 Un生洗经伤真波形节点 口1 Unassigned 诵过该按钮添加 Unassigned Unassigned 心同 Unassigned Le: Unassigned ckn Unatsigned datain(0] dalar(1] Unassigned ydat。n3 Unastigned datar(4] Unassgned dtar6 Unassigned dalar☑

7 步骤3:DDC(FPGA)算法实现、测试与实验验证 3. SignalTap II 使用方法: 2)添加测试节点:在弹出的Node Finder对话框点击List 按钮,并完成波形节点添加 实验1. DDC的设计与验证

实验1.DDC的设计与验证 L956 步骤3:DDC(FPGA)算法实现、测试与实验验证 3.SignalTapⅡ使用方法: 3)初始化输入信号: 图 Master Time Bar 16725s Pointer: 100ps Intervat 1663s Start: kA 10.0ns 20.0n 30.0 Yane 光® 16 16.725n5 回 A [J 少6 clkin 纳令 7 datain O][O] 炬点 司22 ▣dataout 00 37 i_clkic A 三烟 对于输入信号可以设置初始值 汇烟 炬器 及置常量 c 用于设置时钟信号 炬海 跟! 8

8 步骤3:DDC(FPGA)算法实现、测试与实验验证 3. SignalTap II 使用方法: 3)初始化输入信号: 实验1. DDC的设计与验证

实验1.DDC的设计与验证 L956 步骤3:DDC(FPGA)算法实现、测试与实验验证 3.SignalTapⅡ使用方法: 4)选择菜单栏中Processing->Simulator Tool,开始仿真: Simulator Tool 此处选择时序仿真 ▣可x9 Simulation mode: Functional Generate Functional Simulation Nelst Functional Master Time Bar. 16.825ns Pointer: 61025ns Intervab 59343ns End: 510.0ns 1.15as 1.47us 1.79us 2.43us 细 830.0ns 2.11us 2.751 Hane 0 elkin 1 回1 司7 回datain 司22 回tenpI)1 D37 i_clkin 038 曰dataout Overwrite simulation input fie with simulation results Generate Signal Activity Fle Generate VCD File 点击Star t开始仿直 0装 0000:00 Stait Stop 1Open Report 9

9 步骤3:DDC(FPGA)算法实现、测试与实验验证 3. SignalTap II 使用方法: 4)选择菜单栏中Processing -> Simulator Tool,开始仿真: 实验1. DDC的设计与验证

实验1.DDC的设计与验证 Tc 1956 实验步骤 步骤3:DDC(FPGA)算法实现、测试与实验验证 √QuartusIⅡ使用指南 √用QuartusIⅡ自带IP核辅助实现设计 √利用SignalTap IⅡ进行时序仿真与测试的方法 √硬件模块功能实现与测试 10

10 实验步骤 步骤3:DDC(FPGA)算法实现、测试与实验验证 QuartusII 使用指南 用 QuartusII 自带IP核辅助实现设计 利用SignalTap II 进行时序仿真与测试的方法 硬件模块功能实现与测试 实验1. DDC的设计与验证

实验1.DDC的设计与验证 Tc 1956 )实验步骤 步骤3:DDC(FPGA)算法实现、测试与实验验证 √硬件模块功能实现与测试 >AD/DA测试 >NCO实现与测试 >信号变频实现与测试 >第一级抽取(HB滤波)实现与测试 >第二级抽取(HB滤波)实现与测试 >第三级抽取(FIR滤波)实现与测试 11

11 实验步骤 步骤3:DDC(FPGA)算法实现、测试与实验验证 硬件模块功能实现与测试 AD/DA测试 NCO实现与测试 信号变频实现与测试 第一级抽取(HB滤波)实现与测试 第二级抽取(HB滤波)实现与测试 第三级抽取(FIR滤波)实现与测试 实验1. DDC的设计与验证