实验1.DDC的设计与验证 1956 。实验1设计任务: 将中频频率为f)的中频正弦信号经A/D采样后下变频到0.IMz 并将数据率降到400Ksps; 中频频率范围[10.2MHz:0.1MHz:12.1MHz],根据实验小 组序号选择设计的频点,如第1组,选择1号频点f0,=102MHz 第20组,选择20号频,点:f0,=12.1MHz 参考步骤1和步骤2,完成设计的前两个步骤。(3学时) 2

2 实验1设计任务: 将中频频率为 的中频正弦信号经A/D采样后下变频到 , 并将数据率降到 ; 中频频率范围 ,根据实验小 组序号选择设计的频点,如第1组,选择1号频点 第20组,选择20号频点: 参考步骤1和步骤2,完成设计的前两个步骤。(3学时) 0f [10.2MHz : 0.1MHz : 12.1MHz] 0.1MHz 400Ksps 1 f0 =10.2MHz 20 f0 =12.1MHz 实验1. DDC的设计与验证

实验1.DDC的设计与验证 Tc 1956 实验步骤 √步骤1:设计具体的DDC实现结构与系统工作参数 √步骤2:利用MATLAB进行DDC模块设计仿真与验证 √步骤3:DDC(FPGA)算法实现、测试与实验验证 3

3 实验步骤 步骤1:设计具体的DDC实现结构与系统工作参数 步骤2:利用MATLAB进行DDC模块设计仿真与验证 步骤3:DDC(FPGA)算法实现、测试与实验验证 实验1. DDC的设计与验证

实验1.DDC的设计与验证 Tc 1956 实验步骤 步骤3:DDC(FPGA)算法实现、测试与实验验证 √参考资料 √QuartusIⅡ使用指南 √用QuartusII自带IP核辅助实现设计 4

4 实验步骤 步骤3:DDC(FPGA)算法实现、测试与实验验证 参考资料 QuartusII 使用指南 用 QuartusII 自带IP核辅助实现设计 实验1. DDC的设计与验证

实验1.DDC的设计与验证 L956 ●步骤3:DDC(FPGA)算法实现、测试与实验验证 参考资料 ●】 HDL语言编程参考书籍 1) 《VHDL实用教程》,潘松,电子科技大学出版社 2) 《Verilog数字系统设计教程》,夏宇闻,北京航天航空大学出版社 Quartus]Ⅱ软件使用参考资料 l)网络资源:http:www.altera.com.cn/support/software/sof-quartus.html 2)参考书籍:《Altera FPGA/CPLD设计》(基础篇、高级篇),人民邮电出版社 5

5 步骤3:DDC(FPGA)算法实现、测试与实验验证 参考资料 HDL 语言编程参考书籍 1) 《VHDL 实用教程》,潘松,电子科技大学出版社 2) 《Verilog 数字系统设计教程》,夏宇闻,北京航天航空大学出版社 QuartusII 软件使用参考资料 1) 网络资源:http://www.altera.com.cn/support/software/sof-quartus.html 2) 参考书籍:《Altera FPGA/CPLD 设计》(基础篇、高级篇),人民邮电出版社 实验1. DDC的设计与验证

实验1.DDC的设计与验证 S Tc 1956 实验步骤 步骤3:DDC(FPGA)算法实现、测试与实验验证 √QuartusIⅡ使用指南 >设计流程 >设计文件输入 >创建QuartusIⅡ工程 >编译设计 >管脚约束 6

6 实验步骤 步骤3:DDC(FPGA)算法实现、测试与实验验证 QuartusII 使用指南 设计流程 设计文件输入 创建QuartusII工程 编译设计 管脚约束 实验1. DDC的设计与验证

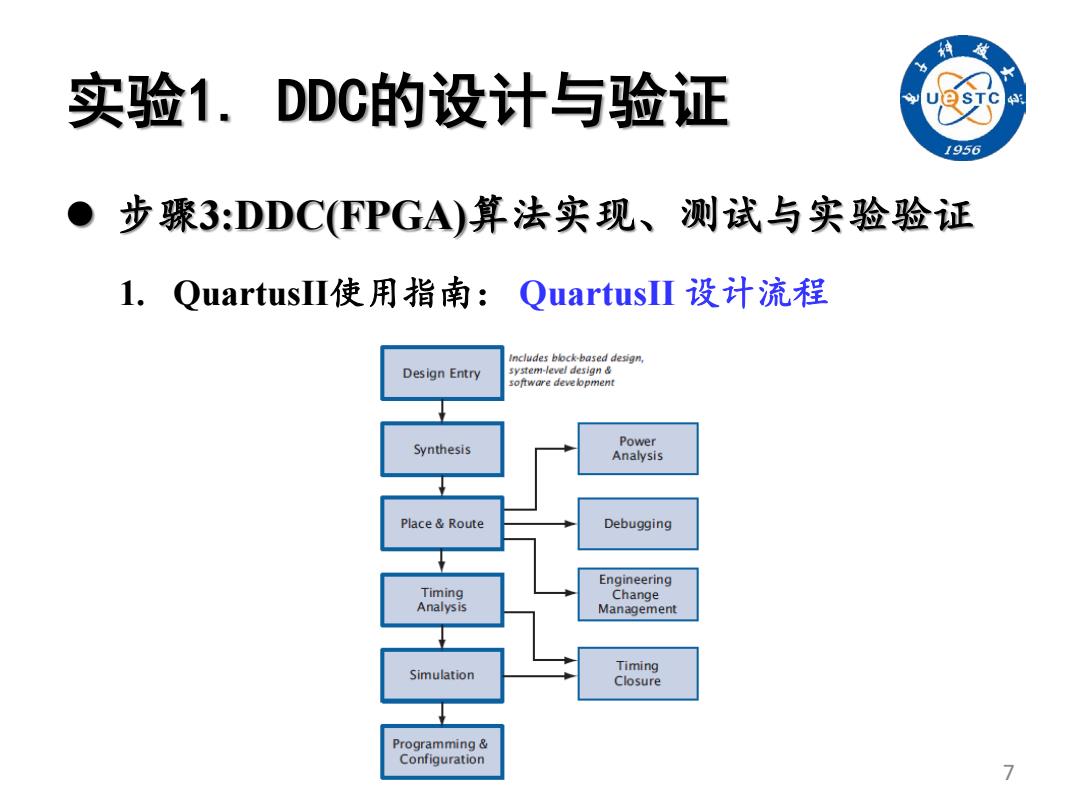

实验1.DDC的设计与验证 L956 步骤3:DDC(FPGA)算法实现、测试与实验验证 1.QuartusIⅡ使用指南: QuartusⅡ设计流程 Includes block-based design, Design Entry system-level design software develpment Power Synthesis Analysis Place Route Debugging Engineering Timing Change Analysis Management Timing Simulation Closure Programming Configuration 7

7 步骤3:DDC(FPGA)算法实现、测试与实验验证 1. QuartusII使用指南: QuartusII 设计流程 实验1. DDC的设计与验证

实验1.DDC的设计与验证 L956 步骤3:DDC(FPGA)算法实现、测试与实验验证 1.Quartus]Ⅱ使用指南:Quartus]Ⅲ工程设计文件输入 QuartusⅡ工程由所有设计文件和与设计有关的设置组成。 设计文件及其产生方法: √Quartus IⅡBlock Editor √Quartus IⅡText Editor Mega Wizard Plug-In Manager:Megafunctions、LPM、IlP核 Quartus IⅡSymbol Editor:单元符号(Primitives)块 System-level design entry with Altera SOPC Builder or DSP Builder software 8

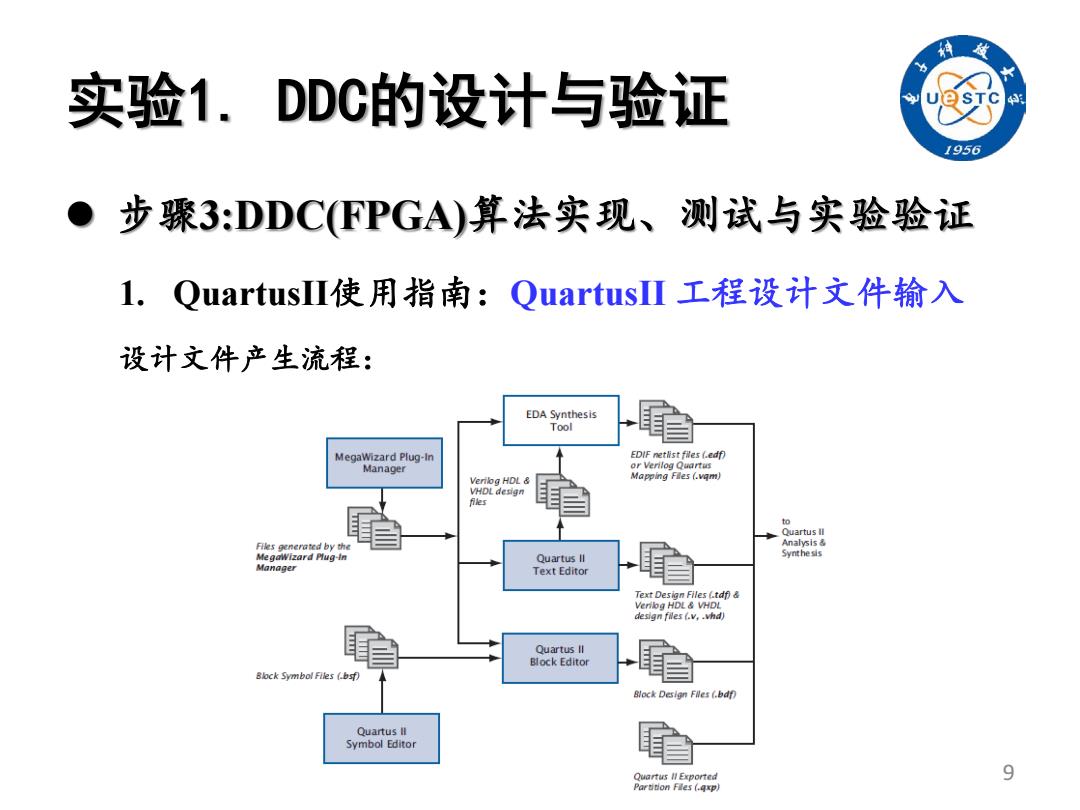

8 步骤3:DDC(FPGA)算法实现、测试与实验验证 1. QuartusII使用指南:QuartusII 工程设计文件输入 QuartusII 工程由所有设计文件和与设计有关的设置组成。 设计文件及其产生方法: Quartus II Block Editor Quartus II Text Editor MegaWizard Plug-In Manager:Megafunctions、LPM、IP核 Quartus II Symbol Editor:单元符号(Primitives)块 System-level design entry with Altera SOPC Builder or DSP Builder software 实验1. DDC的设计与验证

实验1.DDC的设计与验证 L956 步骤3:DDC(FPGA)算法实现、测试与实验验证 1.QuartusⅡ使用指南: QuartusII工程设计文件输入 设计文件产生流程: EDA Synthesis Tool Megawizard Plug-In EDIF netlist fies (.edf) Manager or Verilog Quartus Verila HDL Mapping Fles (.vqm) VHDL design to Quartus ll Flles generated by the Analysis& Me gawizard Plug-in Quartus ll Synthe sis Manager Text Editor Text Design Files (.tdf Veribg HDL VHDL design fies (.v,.vhd) Quartus ll Block Editor Block Design FNes (.bdf) Quartus ll Symbol Editor Quartus ll Exported 9 Partition Fles(.qxp)

9 步骤3:DDC(FPGA)算法实现、测试与实验验证 1. QuartusII使用指南:QuartusII 工程设计文件输入 设计文件产生流程: 实验1. DDC的设计与验证

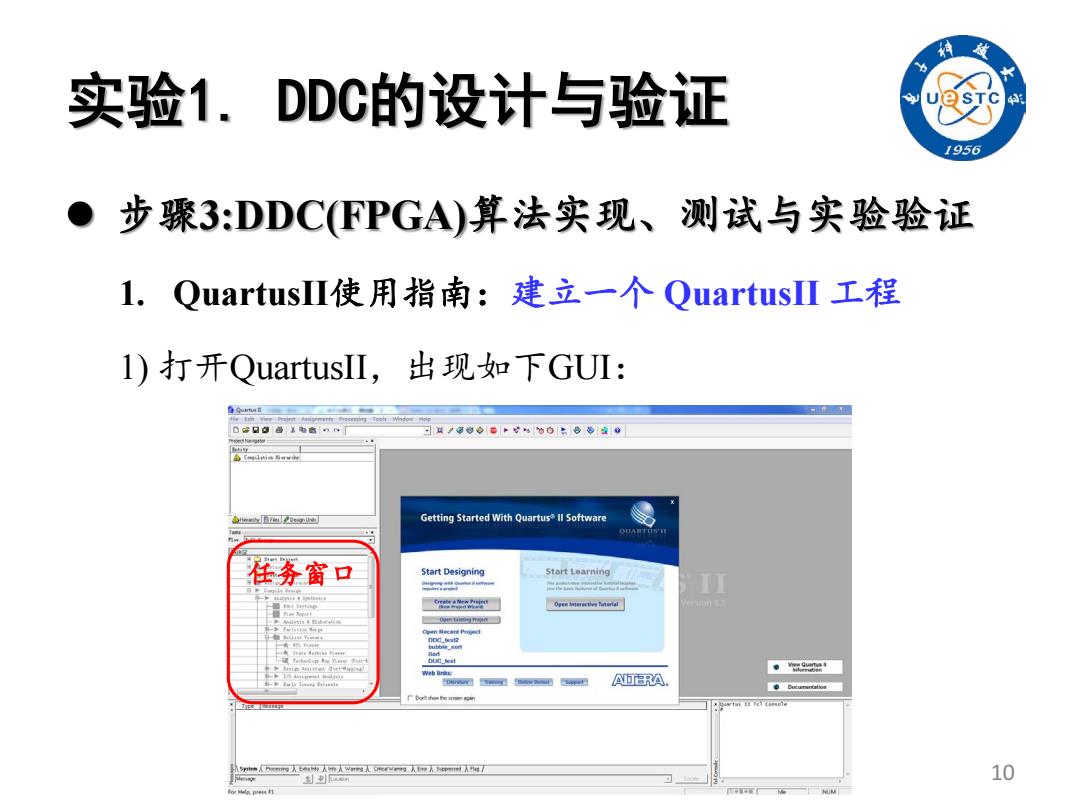

实验1.DDC的设计与验证 L956 步骤3:DDC(FPGA)算法实现、测试与实验验证 1.QuartusIⅡ使用指南:建立一个QuartusⅡ工程 1)打开QuartusIⅡ,出现如下GUI: 过7g白◇。·物06820 Getting Started With Quartus ll Software 任务窗口 Start Designing Start Learning 6 。9 ADERA. Bocurtartalios 10

10 步骤3:DDC(FPGA)算法实现、测试与实验验证 1. QuartusII使用指南:建立一个 QuartusII 工程 1) 打开QuartusII,出现如下GUI: 任务窗口 实验1. DDC的设计与验证

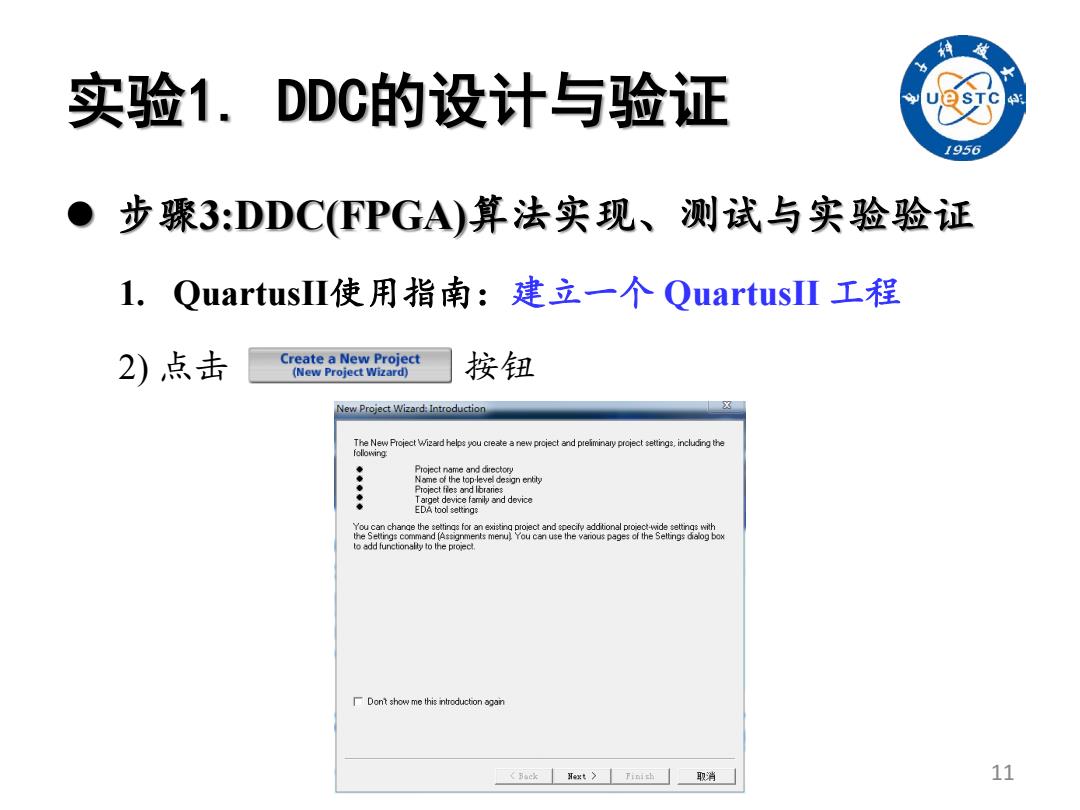

实验1.DDG的设计与验证 L956 步骤3:DDC(FPGA)算法实现、测试与实验验证 1.QuartusIⅡ使用指南:建立一个QuartusⅡ工程 2)点击 Create a New Project (New Project Wizard) 按钮 New Project Wizard:Introduction The New Project Wizard helps you create a new projec following Project name and directory Name of the top-level design enbty Project fies and lbraries Target device famil and device EDA tool settnge You can chanae the settings for an existing proiect and specify addhonal proiect-wide settings with the Settings command (Assignments menul You can use the various pages of the Seltings dalog box to add funchonally to the proect. Dont show me this introduction agan <Back Hext Finith 取消 11

11 步骤3:DDC(FPGA)算法实现、测试与实验验证 1. QuartusII使用指南:建立一个 QuartusII 工程 2) 点击 按钮 实验1. DDC的设计与验证