第4章低温多晶硅薄膜晶体管 简介 4.1多晶硅半导体的物理基础 4.2 LTPS TFT的工作原理与特性 4.3 LTPS TFT中的关键材料技术 4.4非晶硅晶化技术

第4章 低温多晶硅薄膜晶体管 简介 4.1 多晶硅半导体的物理基础 4.2 LTPS TFT的工作原理与特性 4.3 LTPS TFT中的关键材料技术 4.4 非晶硅晶化技术

简介 p-Si TFT分为低温与高温TFT两类。LTPS TFT-LCD器件要比 HTPS TFT-LCD器件具有更低的成本,更简单的工艺和更大的应 用范围 LTPS与HTPS TFT-LCD的比较 性能 LTPS HTPS 工艺温度(C) 900 基板 玻璃 石英 晶化方法 ELA SPC 栅极绝缘层制造方法 PECVD 热处理 基础工艺 非晶硅TFT Si-LSI 应用 直视显示,投影显示 投影显示

简介 • p-Si TFT分为低温与高温TFT两类。LTPS TFT-LCD器件要比 HTPS TFT-LCD器件具有更低的成本,更简单的工艺和更大的应 用范围 性能 LTPS HTPS 工艺温度(℃) 900 基板 玻璃 石英 晶化方法 ELA SPC 栅极绝缘层制造方法 PECVD 热处理 基础工艺 非晶硅TFT Si-LSI 应用 直视显示,投影显示 投影显示 LTPS与HTPS TFT-LCD的比较

多晶硅与非晶硅性能比较 性能参数 非晶硅 多晶硅 迁移率 ≤1cm2Vs 几十~几百 沉积温度 ≤300C ≤600℃(低温多晶硅) 光敏性 高 低 玻璃基底 可用 可用(低温多晶硅) TFT类型 N-ch N-ch,P-ch TFT体积 大 小

多晶硅与非晶硅性能比较 性能参数 非晶硅 多晶硅 迁移率 ≤1cm2 /V·s 几十~几百 沉积温度 ≤300℃ ≤600℃(低温多晶硅) 光敏性 高 低 玻璃基底 可用 可用(低温多晶硅) TFT类型 N-ch N-ch, P-ch TFT体积 大 小

LTPS-TFT发展的动力 多晶硅迁移率高,导通电流lON大,液晶象素的充电速 度快 ,多晶硅TFT尺寸小,寄生电容小 p-ch TFT可行,可将周边LS集成到显示屏基片上,减 少引出端数量,提高可靠性,降低成本

LTPS-TFT发展的动力 • 多晶硅迁移率高,导通电流ION大,液晶象素的充电速 度快 • 多晶硅TFT尺寸小,寄生电容小 • p-ch TFT可行,可将周边LSI集成到显示屏基片上,减 少引出端数量,提高可靠性,降低成本

LTPS-TFT发展历史 ,对LTPS TFT-LCD技术的研究起始于上世纪80年代中期 ,1996年,SANY0率先量产小型LTPS面板,6.35cm屏对角线的产品 问世; 1998年,日本东芝公司开始批量生产LTPS TFT--LCD器件,其尺寸 已达38.1cm,分辨率也达到了UXGA(1600×1200)级 ·1999年LTPS-TFT驱动AMOLED已有重大突破 2000以来,基于LTPS-TFT的中小尺寸LCD、OLED显示器大规 模应用

LTPS-TFT发展历史 • 对LTPS TFT-LCD技术的研究起始于上世纪80年代中期 • 1996年,SANYO率先量产小型LTPS面板,6.35cm屏对角线的产品 问世; • 1998年,日本东芝公司开始批量生产LTPS TFT-LCD器件,其尺寸 已达38.1cm,分辨率也达到了UXGA(1600×1200)级 • 1999年LTPS-TFT驱动AMOLED已有重大突破 • 2000以来,基于LTPS-TFT的中小尺寸LCD、OLED显示器大规 模应用

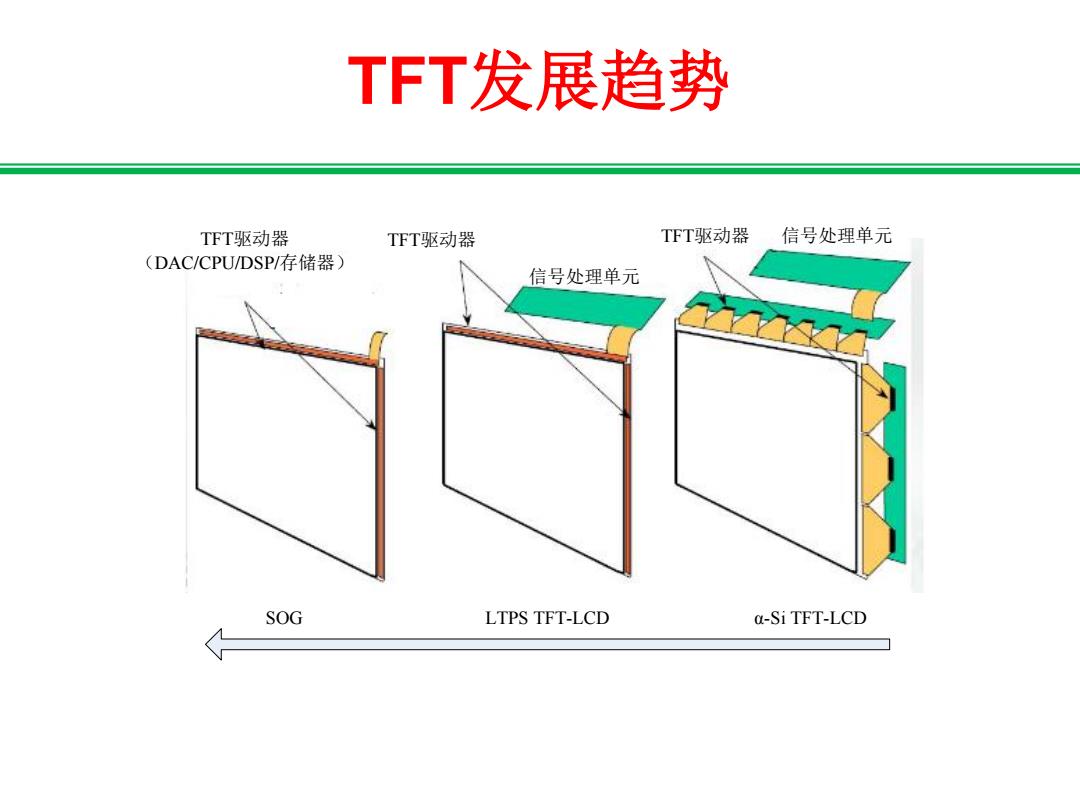

TFT发展趋势 TFT驱动器 TFT驱动器 TFT驱动器 信号处理单元 (DAC/CPU/DSP/存储器) 信号处理单元 SOG LTPS TFT-LCD a-Si TFT-LCD

TFT发展趋势 SOG LTPS TFT-LCD α-Si TFT-LCD TFT驱动器 (DAC/CPU/DSP/存储器) TFT驱动器 TFT驱动器 信号处理单元 信号处理单元

4.1多晶硅半导体的物理基础 4.1.1多晶硅薄膜结构与形貌 多晶硅由大量小晶粒组成,每一个晶粒可看作一块小单晶体,它们具有不同的晶 向,彼此由晶界连接。晶界是晶粒间的过度区,结构复杂,原子呈无序排列,其 厚度通常为几个原子层。 20eneH■e发0.0Ke00 生长方向 晶粒 yokoha SEI 10.CkV x60.000 100mm HO 7om 晶界 晶界 (a) (b)

4.1 多晶硅半导体的物理基础 4.1.1多晶硅薄膜结构与形貌 多晶硅由大量小晶粒组成,每一个晶粒可看作一块小单晶体,它们具有不同的晶 向,彼此由晶界连接。晶界是晶粒间的过度区,结构复杂,原子呈无序排列,其 厚度通常为几个原子层

4.1.2多晶硅的简化能带结构 1.晶界陷阱模型 (1)多晶硅薄膜中晶粒大小一致,是长度为L的立方体结构,周围被晶界包围,与晶粒 长度L相比,晶界厚度忽略不计: (2)总的掺杂浓度为ND,是单一n型(或p型)掺杂。以替位方式掺入晶粒内的掺杂浓 度为N©,且具有与单晶硅类似的激活能,对于非重掺杂情况,杂质在室温下全部电离: (3)分凝在晶界处的杂质浓度为NG,且全部为非电离状态,不影响多晶硅电导率; (4)处于晶界的陷阱面密度为Nt,陷阱能级Et是分离的(以能带中央为零点),在未 俘获载流子时为电中性。 NG 杂质分凝 参与导带 杂质在晶粒间界处分凝,直到晶粒 Np 间界处得到饱和为止。分凝在晶界 的杂质在电学上是不激活的 NGB

4.1.2 多晶硅的简化能带结构 (1)多晶硅薄膜中晶粒大小一致,是长度为L的立方体结构,周围被晶界包围,与晶粒 长度L相比,晶界厚度忽略不计; (2)总的掺杂浓度为ND,是单一n型(或p型)掺杂。以替位方式掺入晶粒内的掺杂浓 度为NG,且具有与单晶硅类似的激活能,对于非重掺杂情况,杂质在室温下全部电离; (3)分凝在晶界处的杂质浓度为NGB,且全部为非电离状态,不影响多晶硅电导率; (4)处于晶界的陷阱面密度为Nt,陷阱能级Et是分离的(以能带中央为零点),在未 俘获载流子时为电中性。 1. 晶界陷阱模型 杂质分凝 杂质在晶粒间界处分凝,直到晶粒 间界处得到饱和为止。分凝在晶界 的杂质在电学上是不激活的 ND NG NGB N NT s 参与导带

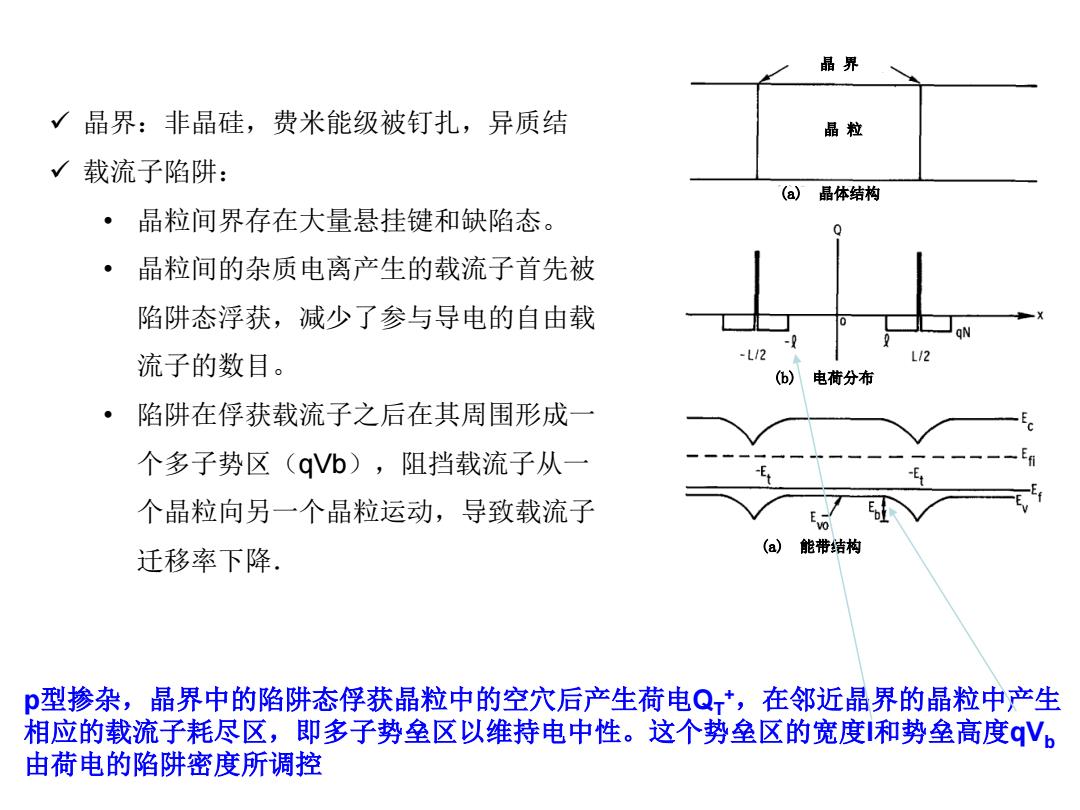

晶界 √晶界:非晶硅,费米能级被钉扎,异质结 晶粒 载流子陷阱: (a)晶体结构 ·晶粒间界存在大量悬挂键和缺陷态。 晶粒间的杂质电离产生的载流子首先被 陷阱态浮获,减少了参与导电的自由载 流子的数日。 L/2 L12 (6)电荷分布 ·陷阱在俘获载流子之后在其周围形成一 个多子势区(qVb),阻挡载流子从一 个晶粒向另一个晶粒运动,导致载流子 E- (a) 能带结构 迁移率下降. 型参杂,晶界中的陷阱态俘获晶粒中的空穴后产生荷电Q+,在邻近晶界的晶粒中产生 相应的载流子耗尽区,即多子势垒区以维持电中性。这个势垒区的宽度和势垒高度qV 由荷电的陷阱密度所调控

晶界:非晶硅,费米能级被钉扎,异质结 载流子陷阱: • 晶粒间界存在大量悬挂键和缺陷态。 • 晶粒间的杂质电离产生的载流子首先被 陷阱态浮获,减少了参与导电的自由载 流子的数目。 • 陷阱在俘获载流子之后在其周围形成一 个多子势区(qVb),阻挡载流子从一 个晶粒向另一个晶粒运动,导致载流子 迁移率下降. 晶 界 晶 粒 (a) 晶体结构 (b) 电荷分布 (a) 能带结构 p型掺杂,晶界中的陷阱态俘获晶粒中的空穴后产生荷电QT +,在邻近晶界的晶粒中产生 相应的载流子耗尽区,即多子势垒区以维持电中性。这个势垒区的宽度l和势垒高度qVb 由荷电的陷阱密度所调控

4.1.3多晶硅薄膜中载流子的传输 ()晶界对多晶硅载流子输运过程的影响: >由于晶界的杂质分凝,使晶粒内的掺杂浓度低于均匀掺杂情况下的掺杂浓 度,减少了有效载流子浓度: >载流子被晶界陷阱俘获,减少了自由载流子数目; >陷阱俘获载流子形成晶粒内耗尽区,使载流子从一个晶粒向另一个晶粒的 输运需要通过热发射或隧穿耗尽区的势垒来进行,载流子迁移率降低

由于晶界的杂质分凝,使晶粒内的掺杂浓度低于均匀掺杂情况下的掺杂浓 度,减少了有效载流子浓度; 载流子被晶界陷阱俘获,减少了自由载流子数目; 陷阱俘获载流子形成晶粒内耗尽区,使载流子从一个晶粒向另一个晶粒的 输运需要通过热发射或隧穿耗尽区的势垒来进行,载流子迁移率降低。 (1) 晶界对多晶硅载流子输运过程的影响: 4.1.3多晶硅薄膜中载流子的传输