正在加载图片...

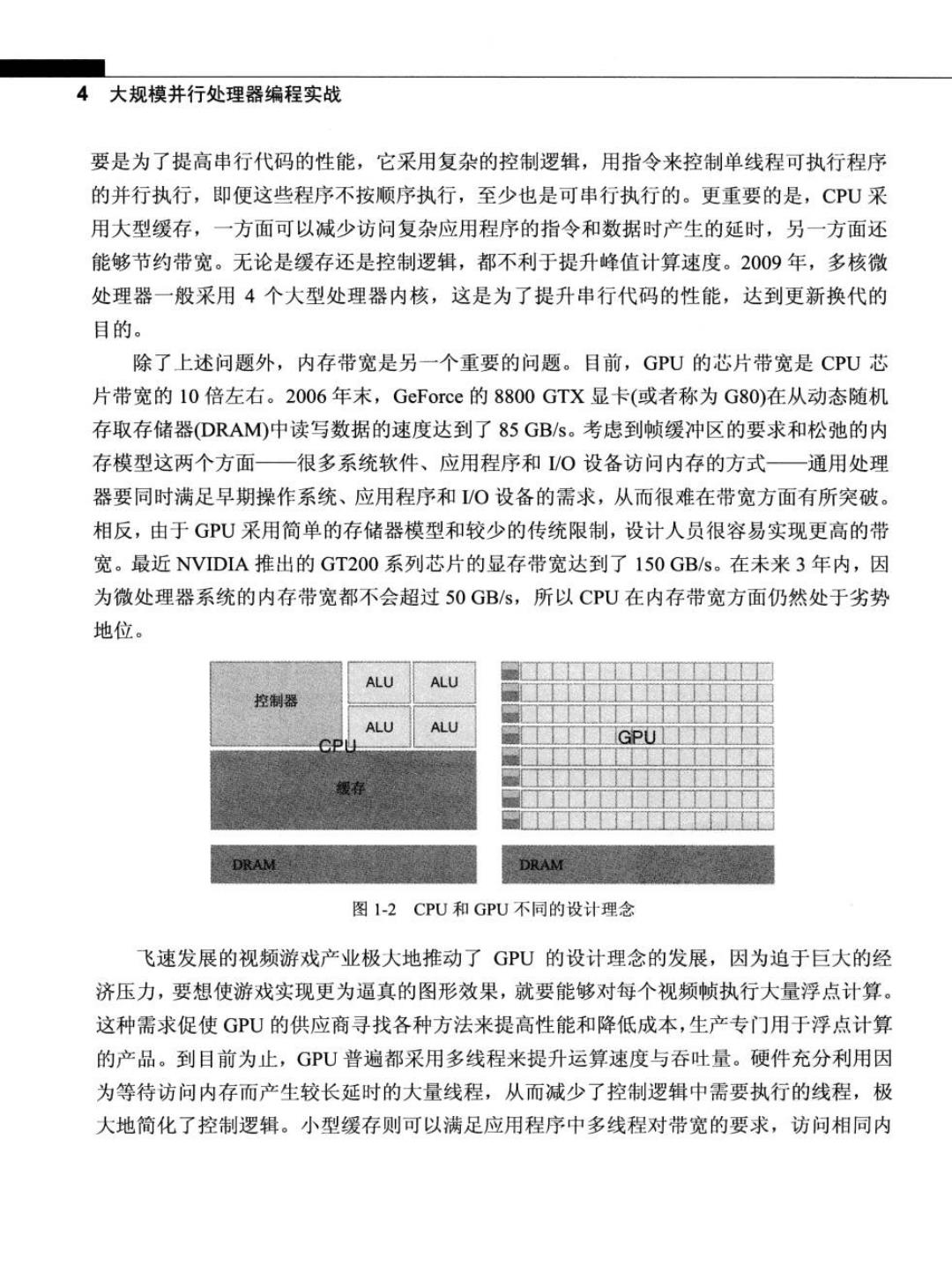

4大规模并行处理器编程实战 要是为了提高串行代码的性能,它采用复杂的控制逻辑,用指令来控制单线程可执行程序 的并行执行,即便这些程序不按顺序执行,至少也是可串行执行的。更重要的是,CPU采 用大型缓存,一方面可以减少访问复杂应用程序的指令和数据时产生的延时,另一方面还 能够节约带宽。无论是缓存还是控制逻辑,都不利于提升峰值计算速度。2009年,多核微 处理器一般采用4个大型处理器内核,这是为了提升串行代码的性能,达到更新换代的 目的。 除了上述问题外,内存带宽是另一个重要的问题。目前,GPU的芯片带宽是CPU芯 片带宽的10倍左右。2006年末,GeForce的8800GTX显卡(或者称为G80)在从动态随机 存取存储器(DRAM)中读写数据的速度达到了85GB/s。考虑到帧缓冲区的要求和松弛的内 存模型这两个方面一很多系统软件、应用程序和/O设备访问内存的方式一通用处理 器要同时满足早期操作系统、应用程序和/O设备的需求,从而很难在带宽方面有所突破。 相反,由于GPU采用简单的存储器模型和较少的传统限制,设计人员很容易实现更高的带 宽。最近NVIDIA推出的GT200系列芯片的显存带宽达到了150GB/s。在未来3年内,因 为微处理器系统的内存带宽都不会超过50GB/s,所以CPU在内存带宽方面仍然处于劣势 地位。 ALU ALU 控制器 ALU ALU DRAM 图1-2CPU和GPU不同的设计理念 飞速发展的视频游戏产业极大地推动了GPU的设计理念的发展,因为迫于巨大的经 济压力,要想使游戏实现更为逼真的图形效果,就要能够对每个视频帧执行大量浮点计算。 这种需求促使GU的供应商寻找各种方法来提高性能和降低成本,生产专门用于浮点计算 的产品。到目前为止,GPU普遍都采用多线程来提升运算速度与吞吐量。硬件充分利用因 为等待访问内存而产生较长延时的大量线程,从而减少了控制逻辑中需要执行的线程,极 大地简化了控制逻辑。小型缓存则可以满足应用程序中多线程对带宽的要求,访问相同内