正在加载图片...

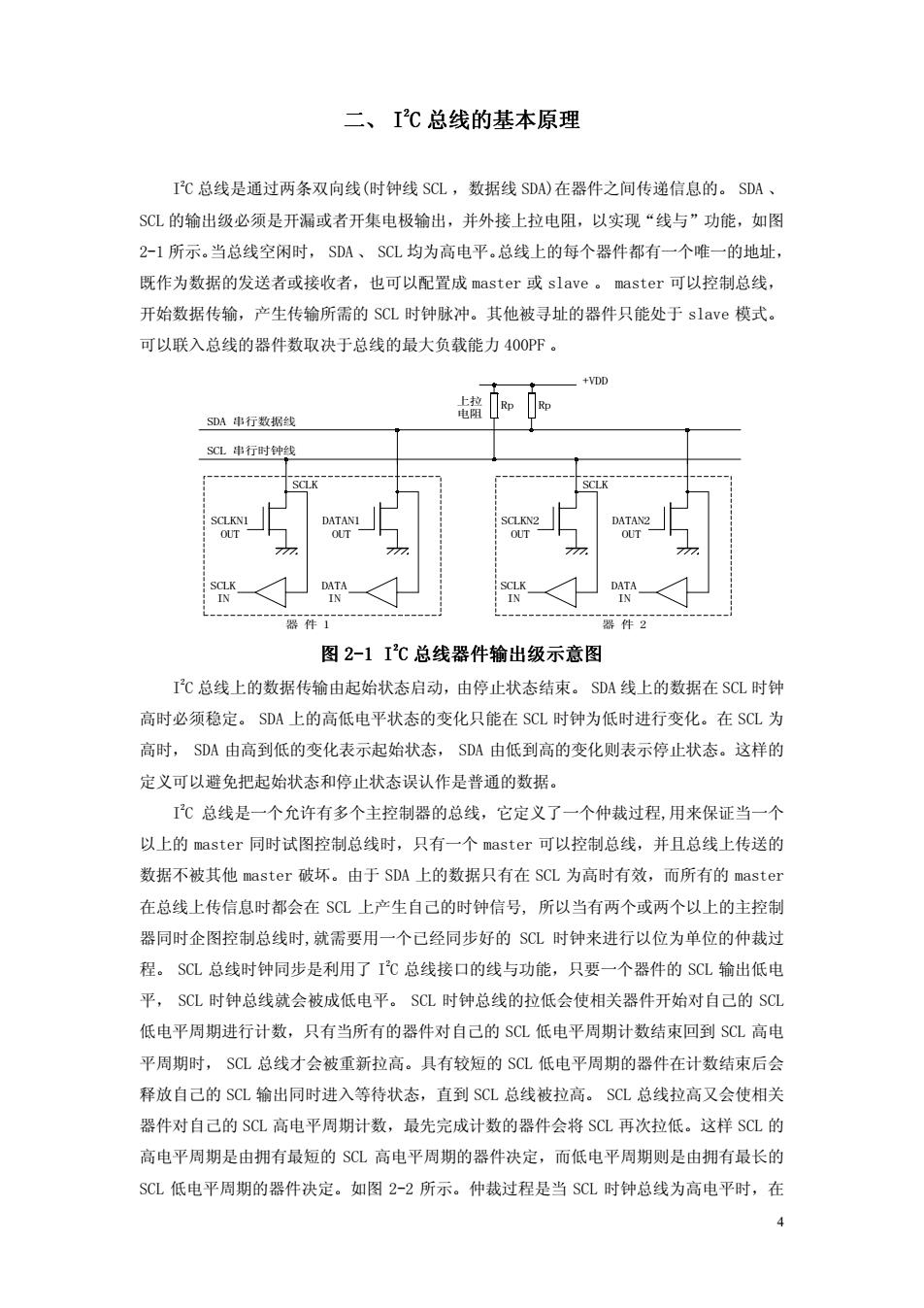

二、I℃总线的基本原理 I℃总线是通过两条双向线(时钟线SCL,数据线SDA)在器件之间传递信息的。SDA、 $CL的输出级必须是开漏或者开集电极输出,并外接上拉电阻,以实现“线与”功能,如图 2-1所示。当总线空闲时,SDA、SCL均为高电平。总线上的每个器件都有一个唯一的地址, 既作为数据的发送者或接收者,也可以配置成master或slave。master可以控制总线, 开始数据传输,产生传输所需的SCL时钟脉冲。其他被寻址的器件只能处于slave模式。 可以联入总线的器件数取决于总线的最大负载能力400P℉。 +VDD 电 SDA串行数据线 SCL串行时钟线 SCLK SCLK SCLKNI DATANI SCLKN2 DATAN2 OUT OUT OUT OUT 777 77 77 DATA SCLK DATA IN IN IN 器件1 器件2 图2-1I℃总线器件输出级示意图 I℃总线上的数据传输由起始状态启动,由停止状态结束。SDA线上的数据在SCL时钟 高时必须稳定。SDA上的高低电平状态的变化只能在SCL时钟为低时进行变化。在SCL为 高时,SDA由高到低的变化表示起始状态,SDA由低到高的变化则表示停止状态。这样的 定义可以避免把起始状态和停止状态误认作是普通的数据。 ℃总线是一个允许有多个主控制器的总线,它定义了一个仲裁过程,用来保证当一个 以上的master同时试图控制总线时,只有一个master可以控制总线,并且总线上传送的 数据不被其他master破坏。由于SDA上的数据只有在SCL为高时有效,而所有的master 在总线上传信息时都会在SCL上产生自己的时钟信号,所以当有两个或两个以上的主控制 器同时企图控制总线时,就需要用一个己经同步好的SCL时钟来进行以位为单位的仲裁过 程。SCL总线时钟同步是利用了I℃总线接口的线与功能,只要一个器件的SCL输出低电 平,SCL时钟总线就会被成低电平。SCL时钟总线的拉低会使相关器件开始对自己的SCL 低电平周期进行计数,只有当所有的器件对自己的SCL低电平周期计数结束回到SCL高电 平周期时,SCL总线才会被重新拉高。具有较短的SCL低电平周期的器件在计数结束后会 释放自己的SCL输出同时进入等待状态,直到SCL总线被拉高。SCL总线拉高又会使相关 器件对自己的SCL高电平周期计数,最先完成计数的器件会将SCL再次拉低。这样SCL的 高电平周期是由拥有最短的$CL高电平周期的器件决定,而低电平周期则是由拥有最长的 SCL低电平周期的器件决定。如图2-2所示。仲裁过程是当SCL时钟总线为高电平时,在

67 cdB> f

« e

eF ¤¥¬f¡g

% e

< f

Ahiâjkâ

lD Imn5o2pÑÒÚ~ kjg +P%RqrB e

< f s9÷-%I

t ¤uÄv

·¨ HI9

«

ãwkxê)5#$Ù Oyüz{ k y|z % Oyüz{ )5WX â7

«¬ïî¬+,

f B>}~%§¨

¤NÒ]Ð y|z % )5ÀM

¤

/Ð

0Ò nKK

%

I

«¬7uv;uvp% e

I

«F f B> ÷Bhi,% e

I

֓-uv

NÒF f B>9ìB8%F f 9 ÷B e

֓

P7uv e

ì÷

QPuv%

,)5°±×7uv[uvI6

«%

89ÄSUWX

,7O)àR 5I

Oyüz{ ©B~WXBNÄ Oyüz{ )5WXDEI¬w

«

Oyüz{ %Ð e

I

«NÄF f 9÷BÄÊÅ+Ä

Oyüz{ FI¬¡gBuF f Iïî

B>¡¢O +5RÄk5I

UWX ©B~WXBO,-"#©ª`

f B>)859¾

7 % f B>©ª

2ÑÒN- ¤

f ì - f B>Ùì-% f B>

mì'34 ¤â7

f ì-?@8

NÄR+Ä

¤

f ì-?@

p f ÷ -?@B f :*m÷%ÃÄ

f ì-?@

¤F

p? ¡A

f ©BM¢£uvÓ f m÷% f m÷Z'34 ¤

f ÷-?@

¤®Ù

¤¥ f ܦmì% f

÷-?@§Ä

f ÷-?@

¤,Åì-?@Q§Ä=

f ì-?@

¤,%Ú~ kjk +P%7R f B>9÷-BF

�����������������������������������������