正在加载图片...

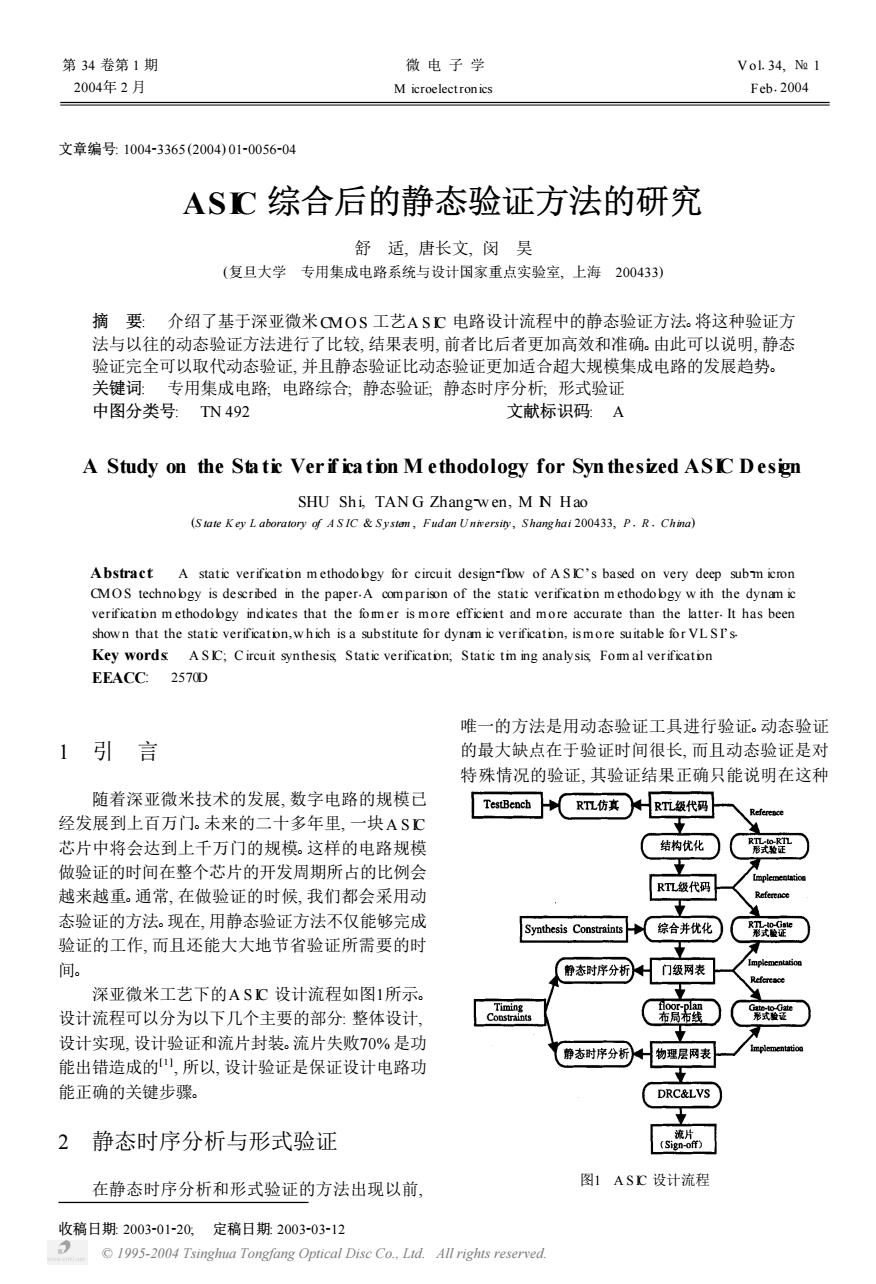

第34卷第1期 微电子学 Vol.34,01 2004年2月 M icroelectronics Feb.2004 文章编号:1004-3365(2004)01-0056-04 ASC综合后的静态验证方法的研究 舒适,唐长文,闵昊 (复旦大学专用集成电路系统与设计国家重点实验室,上海200433) 摘要:介绍了基于深亚微米QMOS工艺ASC电路设计流程中的静态验证方法。将这种验证方 法与以往的动态验证方法进行了比较,结果表明,前者比后者更加高效和准确。由此可以说明,静态 验证完全可以取代动态验证,并且静态验证比动态验证更加适合超大规模集成电路的发展趋势。 关键词:专用集成电路,电路综合,静态验证静态时序分析,形式验证 中图分类号:TN492 文献标识码A A Study on the Static Ver if ication M ethodology for Syn thesized ASIC Design SHU Shi,TAN G Zhangwen,M N Hao (S tate Key L aboratory of A SIC Systen,Fudan University,Shanghai 200433,P.R.China) Abstract A static verification methodobgy for circuit design-fbw of ASIC's based on very deep subm icron CMOS technobgy is described in the paper.A comparison of the static verification methodobgy w ith the dynam ic verification methodobgy indicates that the fomer is more efficient and more accurate than the latter.It has been shown that the static verificaton,w hich is a substitute for dynam ic verificaton,ismore suitable for VLSI's Key words ASC;Circuit synthesis Static verificaton;Static tm ing analysis Fomal verificaton EEACC:2570D 唯一的方法是用动态验证工具进行验证。动态验证 1 引言 的最大缺点在于验证时间很长,而且动态验证是对 特殊情况的验证,其验证结果正确只能说明在这种 随着深亚微米技术的发展,数字电路的规模己 TestBench RTL仿真 HRT级代码 Reference 经发展到上百万门。未来的二十多年里,一块ASC 7 芯片中将会达到上千万门的规模。这样的电路规模 结构优化 做验证的时间在整个芯片的开发周期所占的比例会 越来越重。通常,在做验证的时候,我们都会采用动 RTL级代码 态验证的方法。现在,用静态验证方法不仅能够完成 Synthesis Constraints 综合并优化 验证的工作,而且还能大大地节省验证所需要的时 间。 静态时序分析 门级网表 深亚微米工艺下的ASC设计流程如图1所示。 Timing floor-plan 设计流程可以分为以下几个主要的部分:整体设计, Constraints 布局布线 设计实现,设计验证和流片封装。流片失败70%是功 静态时序分析 物理层网表 能出错造成的),所以,设计验证是保证设计电路功 能正确的关键步骤。 DRC&LVS 2静态时序分析与形式验证 流片 (Sign-off) 在静态时序分析和形式验证的方法出现以前, 图1ASC设计流程 收稿日期2003-01-20,定稿日期2003-03-12 C1995-2004 Tsinghua Tongfang Optical Disc Co..Ltd.All rights reserved.收稿日期: 2003201220; 定稿日期: 2003203212 文章编号: 100423365 (2004) 0120056204 ASIC 综合后的静态验证方法的研究 舒 适, 唐长文, 闵 昊 (复旦大学 专用集成电路系统与设计国家重点实验室, 上海 200433) 摘 要: 介绍了基于深亚微米CM O S 工艺A S IC 电路设计流程中的静态验证方法。将这种验证方 法与以往的动态验证方法进行了比较, 结果表明, 前者比后者更加高效和准确。由此可以说明, 静态 验证完全可以取代动态验证, 并且静态验证比动态验证更加适合超大规模集成电路的发展趋势。 关键词: 专用集成电路; 电路综合; 静态验证; 静态时序分析; 形式验证 中图分类号: TN 492 文献标识码: A A Study on the Sta tic Ver if ica tion M ethodology for Syn thesized ASIC D esign SHU Sh i, TAN G Zhang2w en, M IN H ao (S tate K ey L aboratory of A S IC & S y stem , Fud an U niversity , S hanghai 200433, P 1 R 1 China) Abstract: A static verification m ethodology for circuit design2flow of A S IC’s based on very deep sub2m icron CM O S technology is described in the paper1A comparison of the static verification m ethodology w ith the dynam ic verification m ethodology indicates that the form er is more efficient and more accurate than the latter1It has been show n that the static verification,w h ich is a substitute for dynam ic verification, ismore suitable for VL S I’s1 Key words: A S IC; C ircuit synthesis; Static verification; Static tim ing analysis; Form al verification EEACC: 2570D 1 引 言 随着深亚微米技术的发展, 数字电路的规模已 经发展到上百万门。未来的二十多年里, 一块A S IC 芯片中将会达到上千万门的规模。这样的电路规模 做验证的时间在整个芯片的开发周期所占的比例会 越来越重。通常, 在做验证的时候, 我们都会采用动 态验证的方法。现在, 用静态验证方法不仅能够完成 验证的工作, 而且还能大大地节省验证所需要的时 间。 深亚微米工艺下的A S IC 设计流程如图1所示。 设计流程可以分为以下几个主要的部分: 整体设计, 设计实现, 设计验证和流片封装。流片失败70% 是功 能出错造成的[ 1 ] , 所以, 设计验证是保证设计电路功 能正确的关键步骤。 2 静态时序分析与形式验证 在静态时序分析和形式验证的方法出现以前, 唯一的方法是用动态验证工具进行验证。动态验证 的最大缺点在于验证时间很长, 而且动态验证是对 特殊情况的验证, 其验证结果正确只能说明在这种 图1 A S IC 设计流程 第 34 卷第 1 期 2004年 2 月 微 电 子 学 M icroelect ronics V ol134, № 1 Feb12004 © 1995-2004 Tsinghua Tongfang Optical Disc Co., Ltd. All rights reserved