正在加载图片...

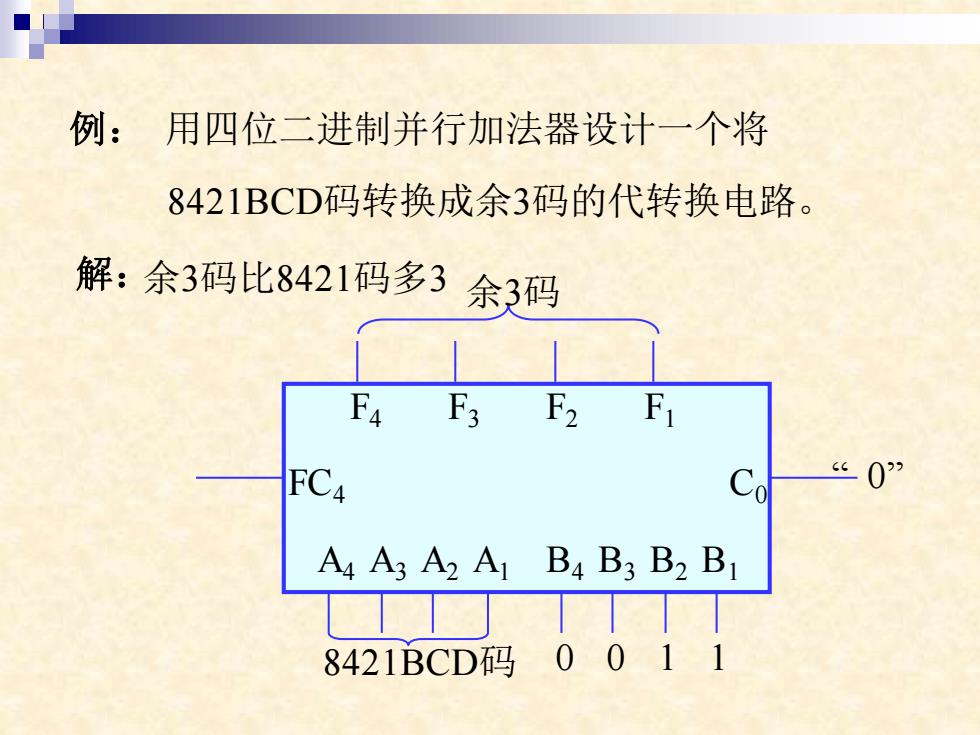

例:用四位二进制并行加法器设计一个将 8421BCD码转换成余3码的代转换电路。 解:余3码比8421码多3 余3码 F4 F3 F2 F1 FC4 Co 0” A4 A3 A2 A B4 B3 B2 B1 8421BCD码0011例: 用四位二进制并行加法器设计一个将 8421BCD码转换成余3码的代转换电路。 余3码比8421码多3 A4 A3 A2 A1 B4 B3 B2 B1 F4 F3 F2 F1 余3码 FC4 C0 8421BCD码 0 0 1 1 “ 0” 解: