正在加载图片...

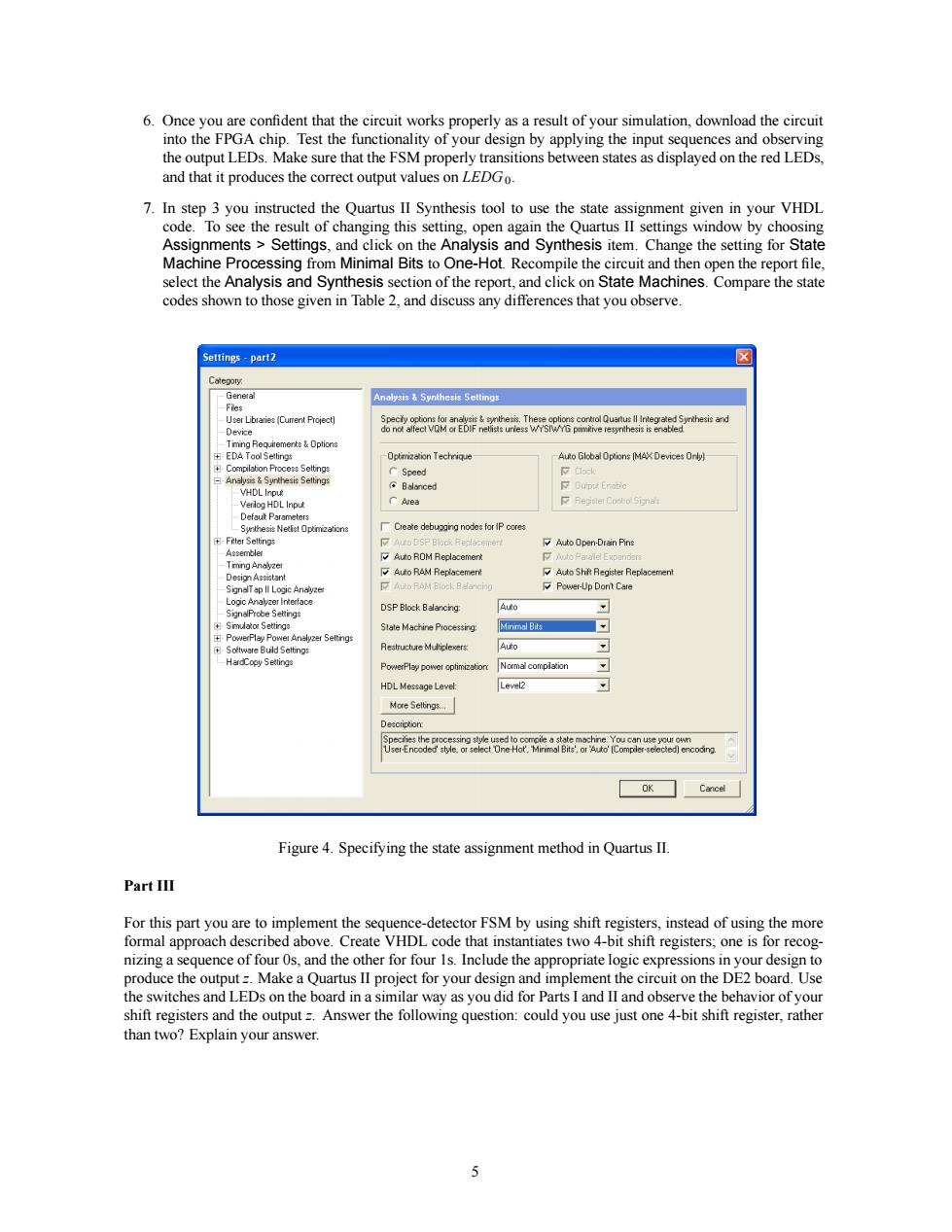

6.Once onfident that the download the circui the output LEDs.Make sure that the FSM properly transitions between states as displaved on the red LEDs and that it produces the correct output values on LEDGo. nts>Settinas and clict Machine Processing from Minimal Bits to One-Hot Recompile the circuit and then open the report file. Settines-pert2 Auto Open-Orain Pre o8aao8m o☐ce Figure 4.Specifying the state assignment method in Quartus II Part II For this part you are to implement the sequence-detector FSM by using shift registers,instead of using the more Poqaeneorihdaboe formal approach des Create VHDL code that instantiates two 4-bit shift registers.one is for recog- ur os, d the other for four Is. the switches and LEDs on the board n asimilar way as you did for Parts I and I and observe the behavior of your shift registers and the output=Answer the following question:could you use just one 4-bit shift register,rather than two?Explain your answer. 5 6. Once you are confident that the circuit works properly as a result of your simulation, download the circuit into the FPGA chip. Test the functionality of your design by applying the input sequences and observing the output LEDs. Make sure that the FSM properly transitions between states as displayed on the red LEDs, and that it produces the correct output values on LEDG0. 7. In step 3 you instructed the Quartus II Synthesis tool to use the state assignment given in your VHDL code. To see the result of changing this setting, open again the Quartus II settings window by choosing Assignments > Settings, and click on the Analysis and Synthesis item. Change the setting for State Machine Processing from Minimal Bits to One-Hot. Recompile the circuit and then open the report file, select the Analysis and Synthesis section of the report, and click on State Machines. Compare the state codes shown to those given in Table 2, and discuss any differences that you observe. Figure 4. Specifying the state assignment method in Quartus II. Part III For this part you are to implement the sequence-detector FSM by using shift registers, instead of using the more formal approach described above. Create VHDL code that instantiates two 4-bit shift registers; one is for recognizing a sequence of four 0s, and the other for four 1s. Include the appropriate logic expressions in your design to produce the output z. Make a Quartus II project for your design and implement the circuit on the DE2 board. Use the switches and LEDs on the board in a similar way as you did for Parts I and II and observe the behavior of your shift registers and the output z. Answer the following question: could you use just one 4-bit shift register, rather than two? Explain your answer. 5