正在加载图片...

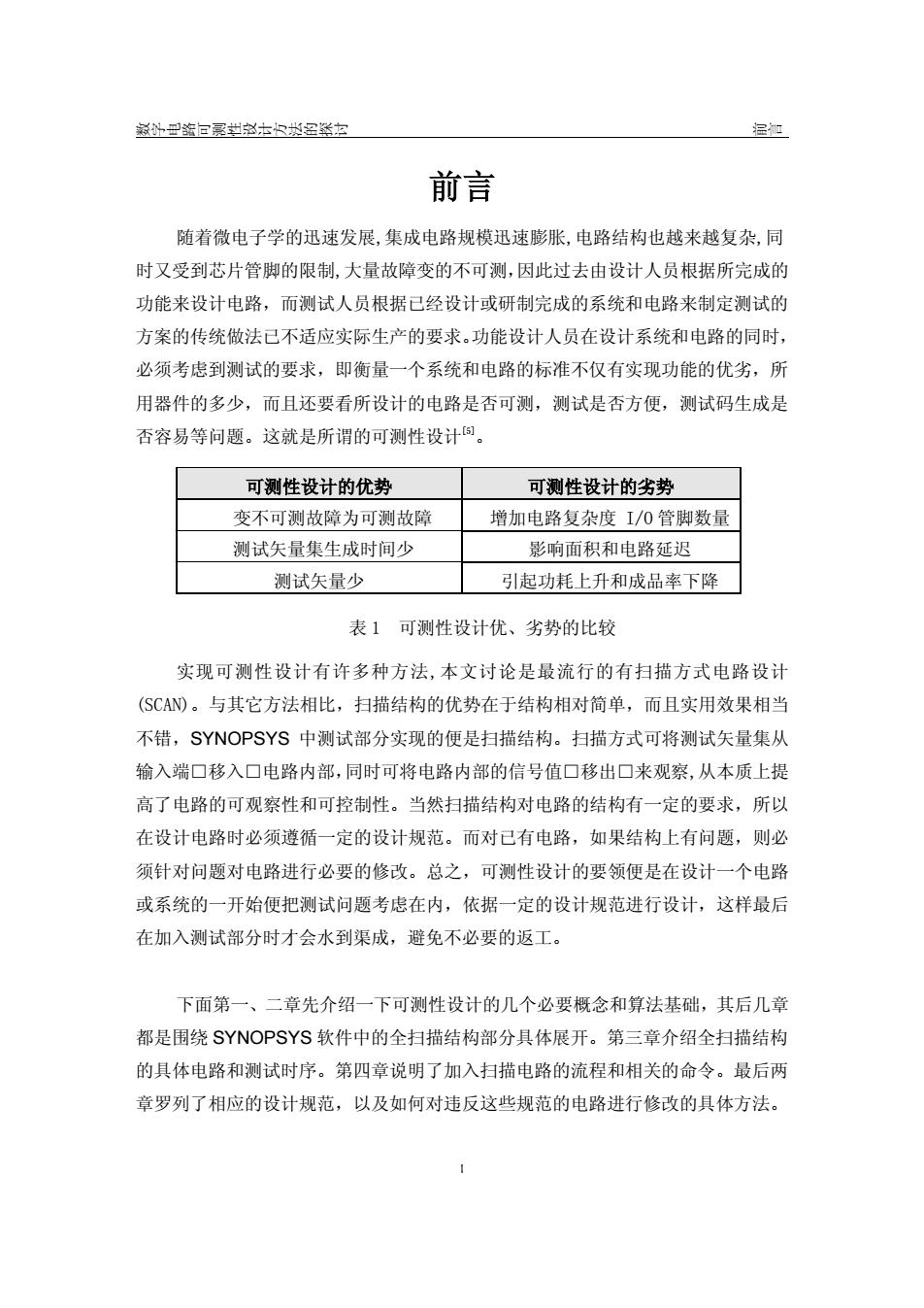

藏州巴资恒录出赵古只兴超张女 福加 前言 随着微电子学的迅速发展,集成电路规模迅速膨胀,电路结构也越来越复杂,同 时又受到芯片管脚的限制,大量故障变的不可测,因此过去由设计人员根据所完成的 功能来设计电路,而测试人员根据已经设计或研制完成的系统和电路来制定测试的 方案的传统做法已不适应实际生产的要求。功能设计人员在设计系统和电路的同时, 必须考虑到测试的要求,即衡量一个系统和电路的标准不仅有实现功能的优劣,所 用器件的多少,而且还要看所设计的电路是否可测,测试是否方便,测试码生成是 否容易等问题。这就是所谓的可测性设计。 可测性设计的优势 可测性设计的劣势 变不可测故障为可测故障 增加电路复杂度I/0管脚数量 测试矢量集生成时间少 影响面积和电路延迟 测试矢量少 引起功耗上升和成品率下降 表1可测性设计优、劣势的比较 实现可测性设计有许多种方法,本文讨论是最流行的有扫描方式电路设计 (SCAN)。与其它方法相比,扫描结构的优势在于结构相对简单,而且实用效果相当 不错,SYNOPSYS中测试部分实现的便是扫描结构。扫描方式可将测试矢量集从 输入端口移入口电路内部,同时可将电路内部的信号值口移出口来观察,从本质上提 高了电路的可观察性和可控制性。当然扫描结构对电路的结构有一定的要求,所以 在设计电路时必须遵循一定的设计规范。而对已有电路,如果结构上有问题,则必 须针对问题对电路进行必要的修改。总之,可测性设计的要领便是在设计一个电路 或系统的一开始便把测试问题考虑在内,依据一定的设计规范进行设计,这样最后 在加入测试部分时才会水到渠成,避免不必要的返工。 下面第一、二章先介绍一下可测性设计的几个必要概念和算法基础,其后几章 都是围绕SYNOPSYS软件中的全扫描结构部分具体展开。第三章介绍全扫描结构 的具体电路和测试时序。第四章说明了加入扫描电路的流程和相关的命令。最后两 章罗列了相应的设计规范,以及如何对违反这些规范的电路进行修改的具体方法。数 字 电 路 可 测 性 设 计 方 法 的 探 讨 前 言 I 前言 随着微电子学的迅速发展,集成电路规模迅速膨胀,电路结构也越来越复杂,同 时又受到芯片管脚的限制,大量故障变的不可测,因此过去由设计人员根据所完成的 功能来设计电路,而测试人员根据已经设计或研制完成的系统和电路来制定测试的 方案的传统做法已不适应实际生产的要求。功能设计人员在设计系统和电路的同时, 必须考虑到测试的要求,即衡量一个系统和电路的标准不仅有实现功能的优劣,所 用器件的多少,而且还要看所设计的电路是否可测,测试是否方便,测试码生成是 否容易等问题。这就是所谓的可测性设计[5]。 可测性设计的优势 可测性设计的劣势 变不可测故障为可测故障 增加电路复杂度 I/O 管脚数量 测试矢量集生成时间少 影响面积和电路延迟 测试矢量少 引起功耗上升和成品率下降 表 1 可测性设计优、劣势的比较 实现可测性设计有许多种方法,本文讨论是最流行的有扫描方式电路设计 (SCAN)。与其它方法相比,扫描结构的优势在于结构相对简单,而且实用效果相当 不错,SYNOPSYS 中测试部分实现的便是扫描结构。扫描方式可将测试矢量集从 输入端□移入□电路内部,同时可将电路内部的信号值□移出□来观察,从本质上提 高了电路的可观察性和可控制性。当然扫描结构对电路的结构有一定的要求,所以 在设计电路时必须遵循一定的设计规范。而对已有电路,如果结构上有问题,则必 须针对问题对电路进行必要的修改。总之,可测性设计的要领便是在设计一个电路 或系统的一开始便把测试问题考虑在内,依据一定的设计规范进行设计,这样最后 在加入测试部分时才会水到渠成,避免不必要的返工。 下面第一、二章先介绍一下可测性设计的几个必要概念和算法基础,其后几章 都是围绕 SYNOPSYS 软件中的全扫描结构部分具体展开。第三章介绍全扫描结构 的具体电路和测试时序。第四章说明了加入扫描电路的流程和相关的命令。最后两 章罗列了相应的设计规范,以及如何对违反这些规范的电路进行修改的具体方法