正在加载图片...

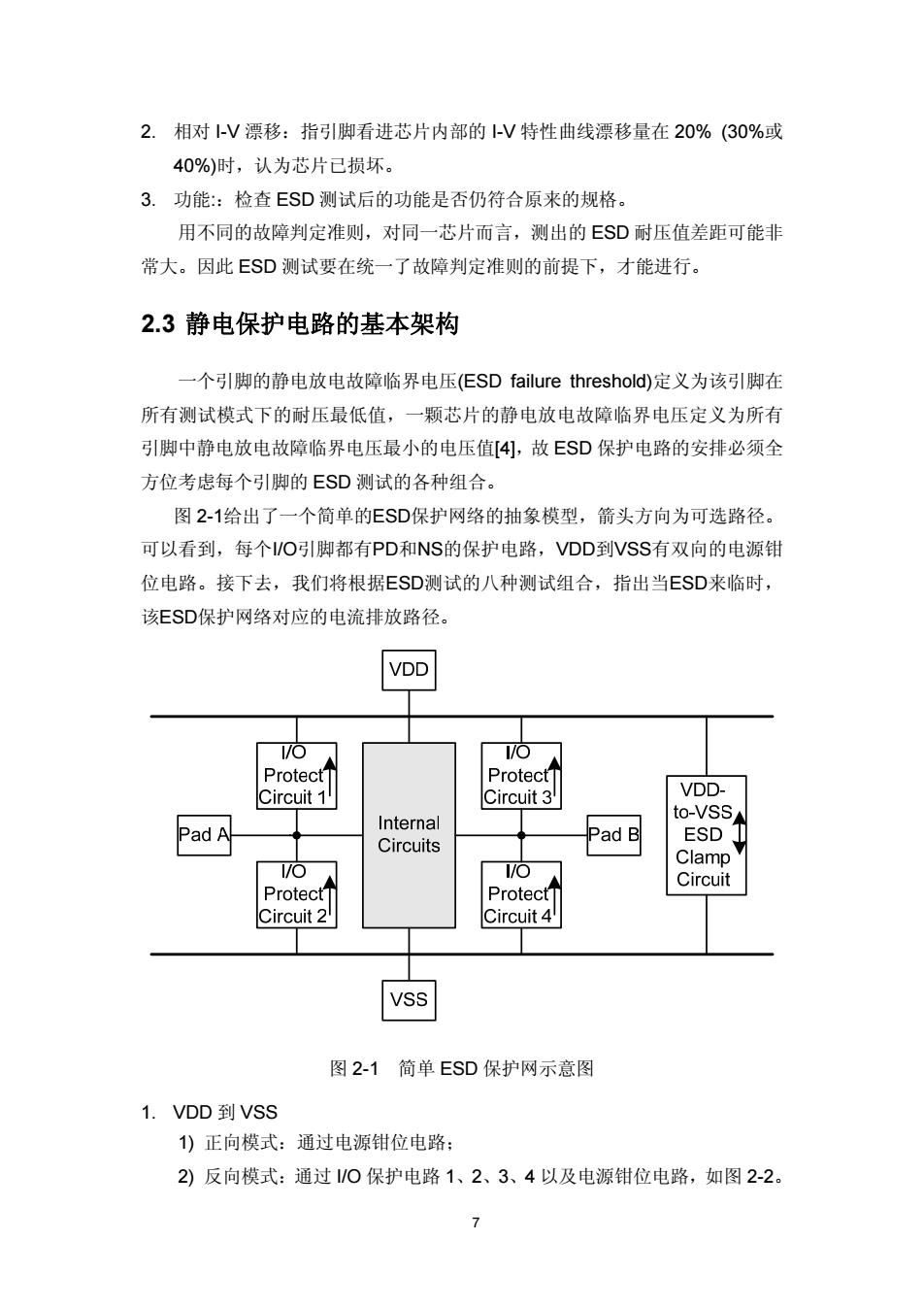

2.相对-V漂移:指引脚看进芯片内部的-V特性曲线漂移量在20%(30%或 40%)时,认为芯片己损坏。 3.功能:检查ESD测试后的功能是否仍符合原来的规格。 用不同的故障判定准则,对同一芯片而言,测出的ESD耐压值差距可能非 常大。因此ESD测试要在统一了故障判定准则的前提下,才能进行。 2.3静电保护电路的基本架构 一个引脚的静电放电故障临界电压(ESD failure threshold)定义为该引脚在 所有测试模式下的耐压最低值,一颗芯片的静电放电故障临界电压定义为所有 引脚中静电放电故障临界电压最小的电压值[4],故ESD保护电路的安排必须全 方位考虑每个引脚的ESD测试的各种组合。 图2-1给出了一个简单的ESD保护网络的抽象模型,箭头方向为可选路径。 可以看到,每个/O引脚都有PD和NS的保护电路,VDD到VSS有双向的电源钳 位电路。接下去,我们将根据ESD测试的八种测试组合,指出当ESD来临时, 该ESD保护网络对应的电流排放路径。 VDD VO I/O ProtectT ProtectT Circuit 1 Circuit 3 VDD- Internal to-VSS Pad A Pad B Circuits ESD 1 I/○ Clamp Circuit Protect Protect] Circuit 2 Circuit 4 Vss 图2-1简单ESD保护网示意图 1.VDD到VSS 1)正向模式:通过电源钳位电路: 2)反向模式:通过/O保护电路1、2、3、4以及电源钳位电路,如图2-2。2. 相对 I-V 漂移:指引脚看进芯片内部的 I-V 特性曲线漂移量在 20% (30%或 40%)时,认为芯片已损坏。 3. 功能::检查 ESD 测试后的功能是否仍符合原来的规格。 用不同的故障判定准则,对同一芯片而言,测出的 ESD 耐压值差距可能非 常大。因此 ESD 测试要在统一了故障判定准则的前提下,才能进行。 2.3 静电保护电路的基本架构 一个引脚的静电放电故障临界电压(ESD failure threshold)定义为该引脚在 所有测试模式下的耐压最低值,一颗芯片的静电放电故障临界电压定义为所有 引脚中静电放电故障临界电压最小的电压值[4],故 ESD 保护电路的安排必须全 方位考虑每个引脚的 ESD 测试的各种组合。 图 2-1给出了一个简单的ESD保护网络的抽象模型,箭头方向为可选路径。 可以看到,每个I/O引脚都有PD和NS的保护电路,VDD到VSS有双向的电源钳 位电路。接下去,我们将根据ESD测试的八种测试组合,指出当ESD来临时, 该ESD保护网络对应的电流排放路径。 图 2-1 简单 ESD 保护网示意图 1. VDD 到 VSS 1) 正向模式:通过电源钳位电路; 2) 反向模式:通过 I/O 保护电路 1、2、3、4 以及电源钳位电路,如图 2-2。 7