正在加载图片...

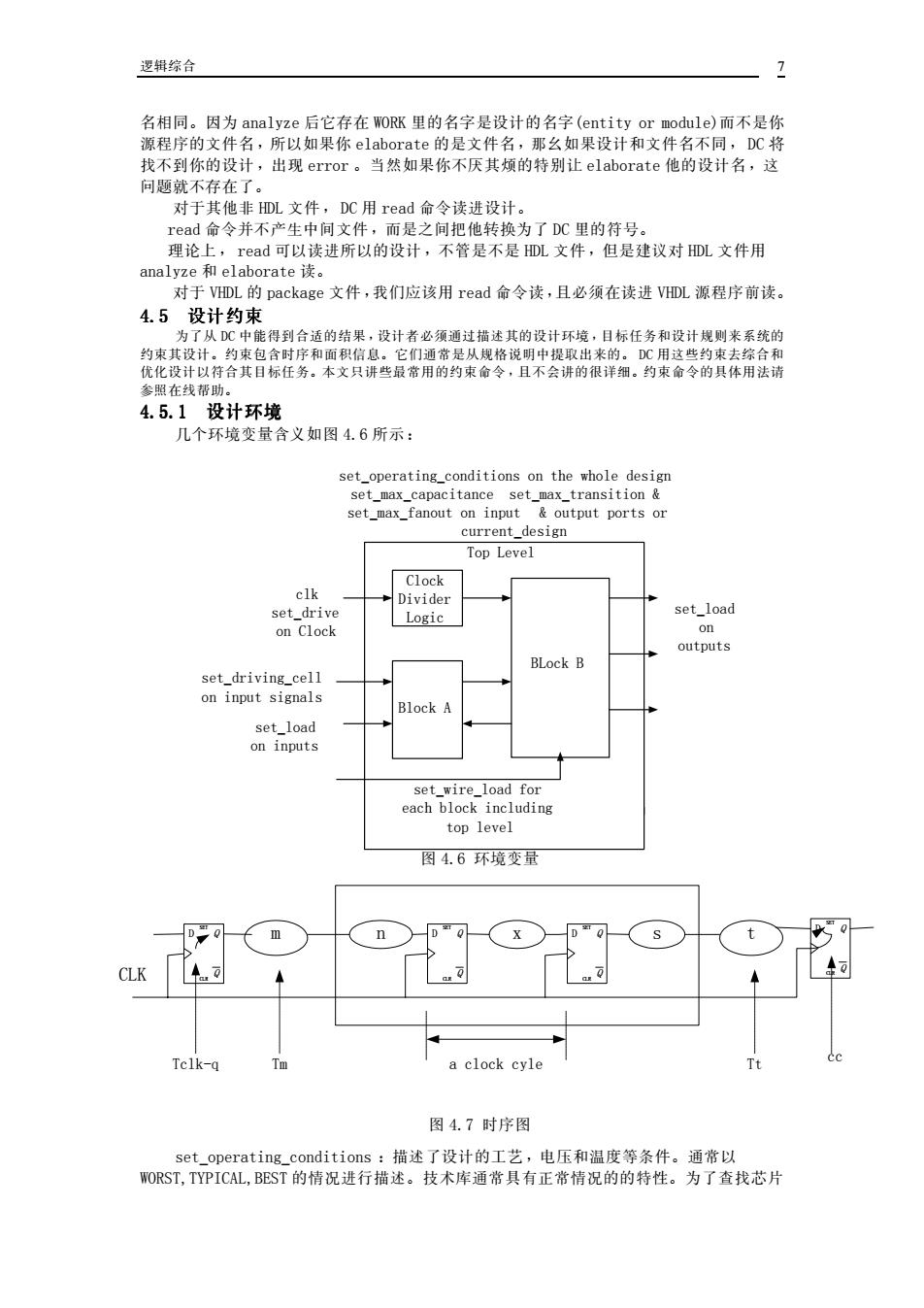

逻辑综合 名相同。因为analyze后它存在WOK里的名字是设计的名字(entity or module)而不是你 源程序的文件名,所以如果你elaborate的是文件名,那么如果设计和文件名不同,DC将 找不到你的设计,出现error。当然如果你不厌其烦的特别让elaborate他的设计名,这 问题就不存在了。 对于其他非DL文件,DC用read命令读进设计。 read命令并不产生中间文件,而是之间把他转换为了DC里的符号。 理论上,read可以读进所以的设计,不管是不是DL文件,但是建议对DL文件用 analyze和elaborate读。 对于VHDL的package文件,我们应该用read命令读,且必须在读进VHDL源程序前读。 4.5设计约束 为了从DC中能得到合适的结果,设计者必须通过描述其的设计环境,目标任务和设计规则来系统的 约束其设计。约束包合时序和面积信息。它们通常是从规格说明中提取出来的。DC用这些约束去综合和 优化设计以符合其目标任务。本文只讲些最常用的约束命令,且不会讲的很详细。约束命令的具体用法请 参照在线帮助。 4.5.1设计环境 几个环境变量含义如图4.6所示: set_operating_conditions on the whole design set_max_capacitance set_max_transition& set max fanout on input output ports or current_design Top Level Clock clk Divider set_drive Logic set_load on Clock on outputs BLock B set_driving_cell on input signals Block A set_load on inputs set_wireload for each block including top level 图4.6环境变量 n CLK .0 Tclk-q a clock cyle 图4.7时序图 set_operating_conditions:描述了设计的工艺,电压和温度等条件。通常以 WORST,TYPICAL,BEST的情况进行描述。技术库通常具有正常情况的的特性。为了查找芯片逻辑综合 7 名相同。因为 analyze 后它存在 WORK 里的名字是设计的名字(entity or module)而不是你 源程序的文件名,所以如果你 elaborate 的是文件名,那幺如果设计和文件名不同, DC 将 找不到你的设计,出现 error 。当然如果你不厌其烦的特别让 elaborate 他的设计名,这 问题就不存在了。 对于其他非 HDL 文件, DC 用 read 命令读进设计。 read 命令并不产生中间文件,而是之间把他转换为了 DC 里的符号。 理论上, read 可以读进所以的设计,不管是不是 HDL 文件,但是建议对 HDL 文件用 analyze 和 elaborate 读。 对于 VHDL 的 package 文件,我们应该用 read 命令读,且必须在读进 VHDL 源程序前读。 4.5 设计约束 为了从 DC 中能得到合适的结果,设计者必须通过描述其的设计环境,目标任务和设计规则来系统的 约束其设计。约束包含时序和面积信息。它们通常是从规格说明中提取出来的。 DC 用这些约束去综合和 优化设计以符合其目标任务。本文只讲些最常用的约束命令,且不会讲的很详细。约束命令的具体用法请 参照在线帮助。 4.5.1 设计环境 几个环境变量含义如图 4.6 所示: 图 4.6 环境变量 图 4.7 时序图 set_operating_conditions :描述了设计的工艺,电压和温度等条件。通常以 WORST,TYPICAL,BEST 的情况进行描述。技术库通常具有正常情况的的特性。为了查找芯片 Top Level BLock B Clock Divider Logic Block A clk set_drive on Clock set_driving_cell on input signals set_load on inputs set_wire_load for each block including top level set_load on outputs set_operating_conditions on the whole design set_max_capacitance set_max_transition & set_max_fanout on input & output ports or current_design D Q Q SET CLR D Q Q SET CLR D n x s Q Q SET CLR D Q Q SET CLR m t CLK Tclk-q Tm a clock cyle Tt cc