正在加载图片...

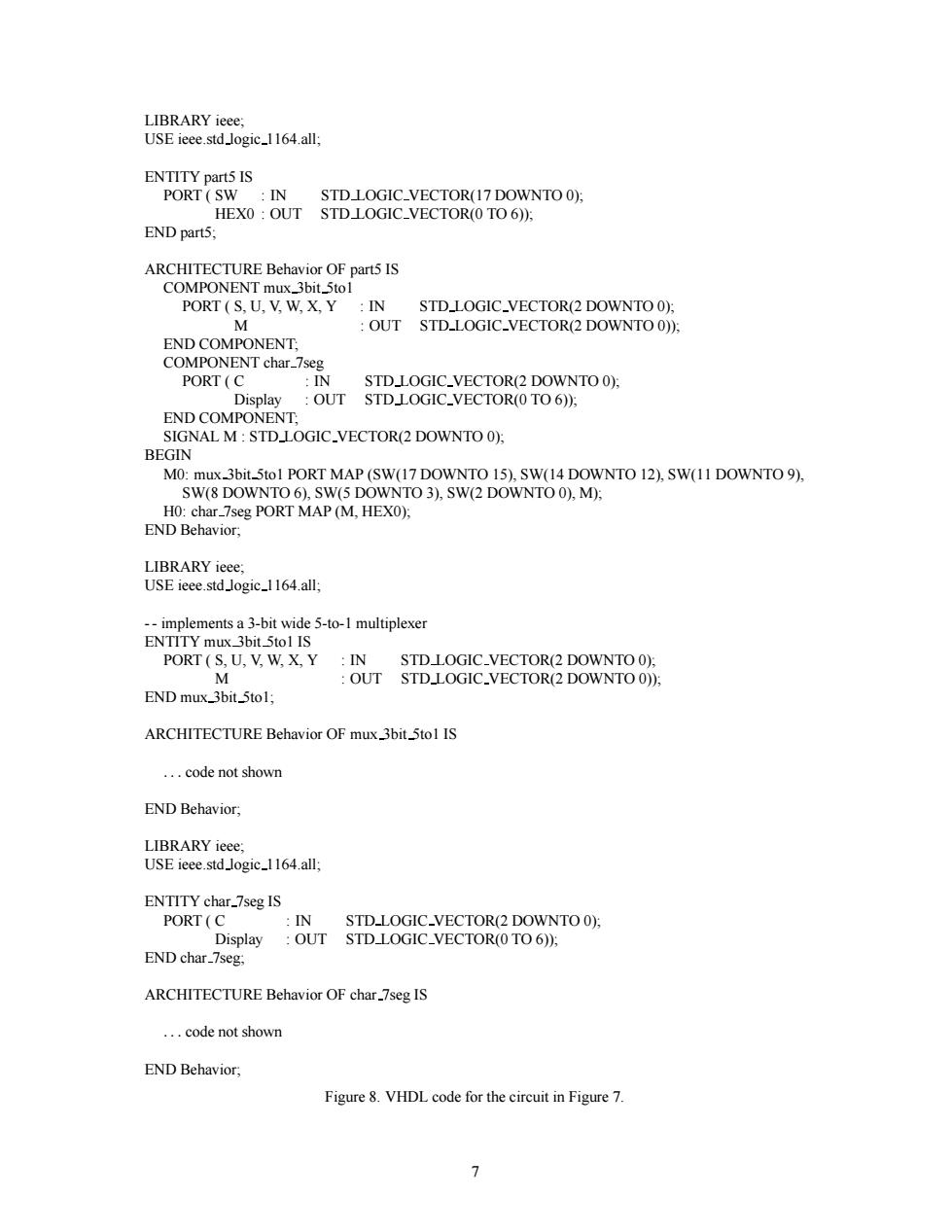

USE ieee.std Jogic-1164.all; ENTITY part5 IS END part5: Beh PORT (S.U.V.W.X.Y IN STD LOGIC_VECTOR(2 DOWNTO 0): OUT STD-LOGIC-VECTOR(2 DOWNTO 0)): END COMPONENT. NI char_ PORT(C STDLOGIC_VECTOR(2 DOWNTO 0): Display OUT STDLOGIC_VECTOR(O TO 6)); END COMPO NE OGIC_VECTOR(2 DOWNTO 0). BEGIN MO:mux.3bit_5to1 PORT MAP (SW(17 DOWNTO 15),SW(14 DOWNTO 12),SW(11 DOWNTO 9). SW(8 DOWNTO 6),SW(5 DOWNTO 3),SW(2 DOWNTO 0),M); LIBRARY ieee. USE ieee.std Jlogic_1164.all PORT (S,U,V,W.X,Y IN STDLOGIC_VECTOR(2 DOWNTO 0) END: ARCHITECTURE Behavior OF mux.3bit.5to1 IS ..code not showr END Behavior: ENTITY char_7seg IS PORT (C IN STD-LOGIC_VECTOR(2 DOWNTO 0). OUT STD-LOGIC_VECTOR(OTO6)) ARCHITECTURE Behavior OF char-7seg IS ..code not shown END Behavior, Figure 8.VHDL code for the circuit in Figure 7. LIBRARY ieee; USE ieee.std logic 1164.all; ENTITY part5 IS PORT ( SW : IN STD LOGIC VECTOR(17 DOWNTO 0); HEX0 : OUT STD LOGIC VECTOR(0 TO 6)); END part5; ARCHITECTURE Behavior OF part5 IS COMPONENT mux 3bit 5to1 PORT ( S, U, V, W, X, Y : IN STD LOGIC VECTOR(2 DOWNTO 0); M : OUT STD LOGIC VECTOR(2 DOWNTO 0)); END COMPONENT; COMPONENT char 7seg PORT ( C : IN STD LOGIC VECTOR(2 DOWNTO 0); Display : OUT STD LOGIC VECTOR(0 TO 6)); END COMPONENT; SIGNAL M : STD LOGIC VECTOR(2 DOWNTO 0); BEGIN M0: mux 3bit 5to1 PORT MAP (SW(17 DOWNTO 15), SW(14 DOWNTO 12), SW(11 DOWNTO 9), SW(8 DOWNTO 6), SW(5 DOWNTO 3), SW(2 DOWNTO 0), M); H0: char 7seg PORT MAP (M, HEX0); END Behavior; LIBRARY ieee; USE ieee.std logic 1164.all; - - implements a 3-bit wide 5-to-1 multiplexer ENTITY mux 3bit 5to1 IS PORT ( S, U, V, W, X, Y : IN STD LOGIC VECTOR(2 DOWNTO 0); M : OUT STD LOGIC VECTOR(2 DOWNTO 0)); END mux 3bit 5to1; ARCHITECTURE Behavior OF mux 3bit 5to1 IS ... code not shown END Behavior; LIBRARY ieee; USE ieee.std logic 1164.all; ENTITY char 7seg IS PORT ( C : IN STD LOGIC VECTOR(2 DOWNTO 0); Display : OUT STD LOGIC VECTOR(0 TO 6)); END char 7seg; ARCHITECTURE Behavior OF char 7seg IS ... code not shown END Behavior; Figure 8. VHDL code for the circuit in Figure 7. 7