第八章可编程逻辑器件DigitalElectronics

Digital Electronics 1 第八章 可编程逻辑器件

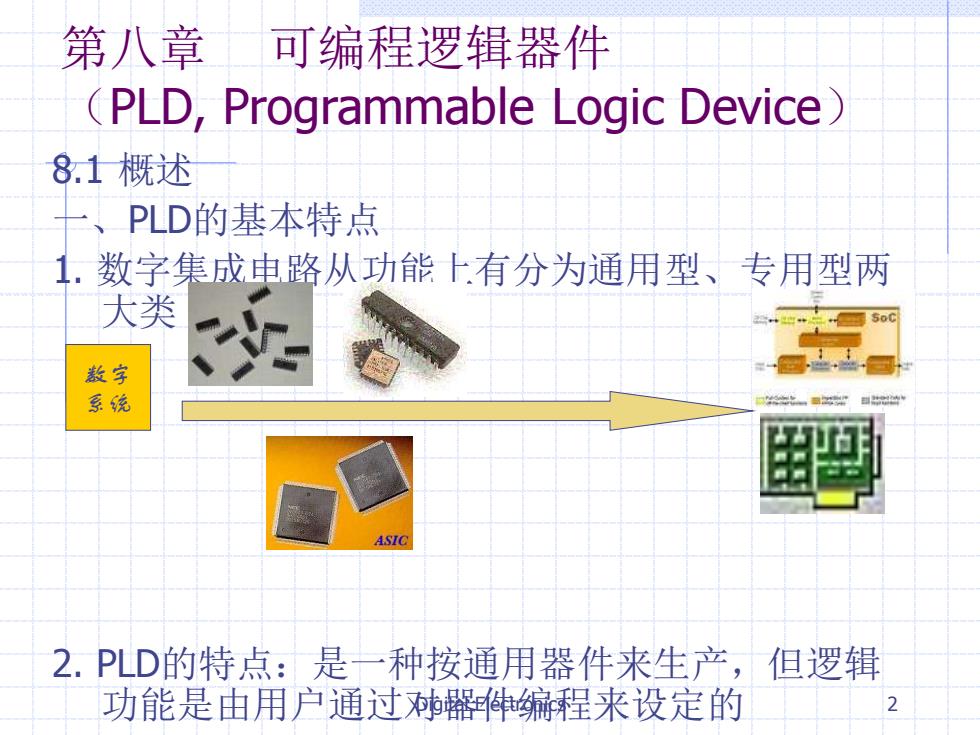

第八章可编程逻辑器件(PLD,ProgrammableLogicDevice)8.1概述一、PLD的基本特点1.数字集成电路从功能上有分为通用型、专用型两大类数字系统2.PLD的特点:是一种按通用器件来生产,但逻辑功能是由用户通过器你编程来设定的

Digital Electronics 2 第八章 可编程逻辑器件 (PLD, Programmable Logic Device) 8.1 概述 一、PLD的基本特点 1. 数字集成电路从功能上有分为通用型、专用型两 大类 2. PLD的特点:是一种按通用器件来生产,但逻辑 功能是由用户通过对器件编程来设定的 数字 系统

二、PLD的发展和分类PROM是最早的PLD1.PAL可编程阵列逻辑2.FPLA现场可编程阵列逻辑3.GAL通用阵列逻辑4.EPLD可擦除的可编程逻辑器件5.FPGA现场可编程门阵列6.ISP-PLD在系统可编程的PLDDigitalElectronics3

Digital Electronics 3 二、PLD的发展和分类 PROM是最早的PLD 1. PAL 可编程阵列逻辑 2. FPLA 现场可编程阵列逻辑 3. GAL 通用阵列逻辑 4. EPLD 可擦除的可编程逻辑器件 5. FPGA 现场可编程门阵列 6.ISP-PLD 在系统可编程的PLD

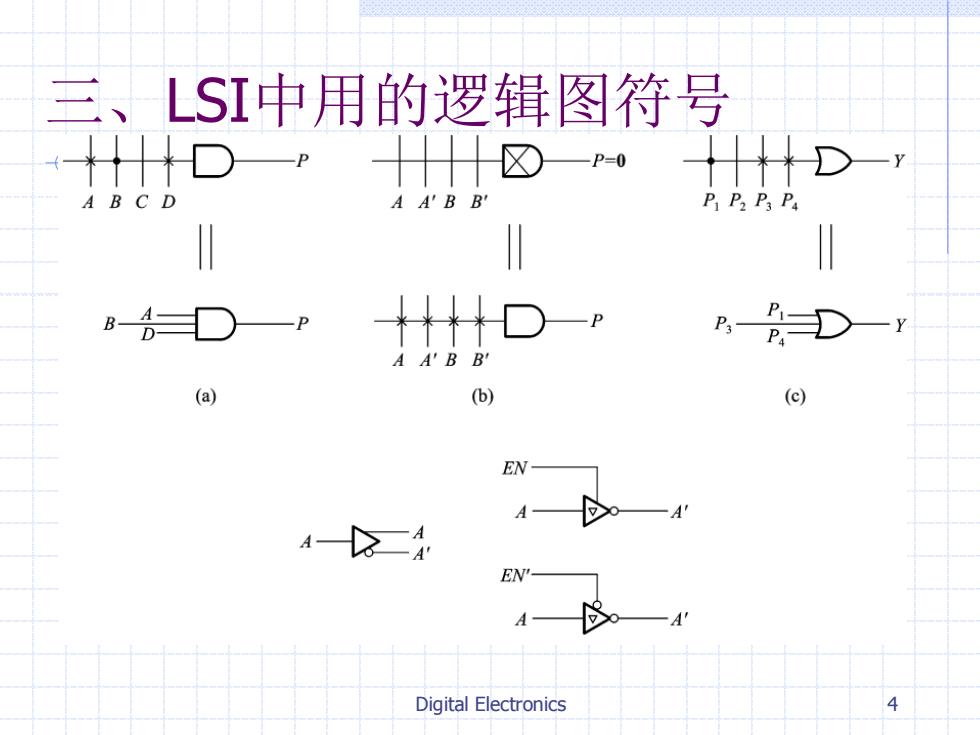

三、LSI中用的逻辑图符号区DO-P=0PPPP4BCDAABB'1111Pi**口-FAB-DP3一P4-AABB'(b)(a)(c)EN>SEN'Digital ElectronicsS

Digital Electronics 4 三、LSI中用的逻辑图符号

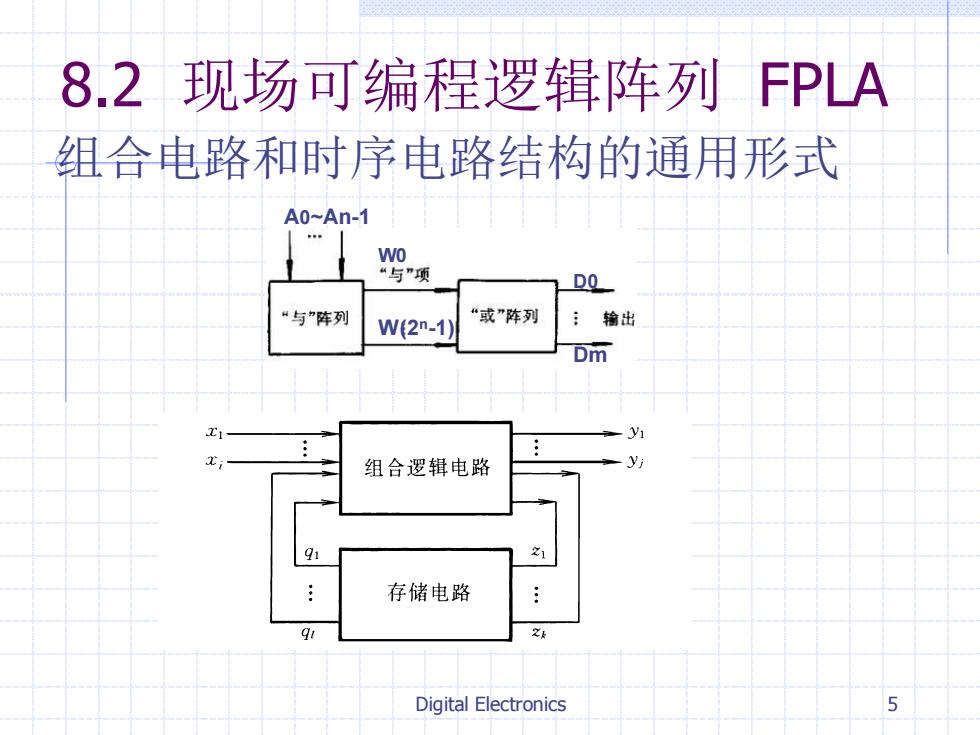

8.2现场可编程逻辑阵列FPLA组合电路和时序电路结构的通用形式A0~An-1WO“与"项DO“或"阵列“与"阵列主输出W(2n-1)Dmr1y1::yia组合逻辑电路q1Z1.存储电路:qt215Digital Electronics

Digital Electronics 5 8.2 现场可编程逻辑阵列 FPLA 组合电路和时序电路结构的通用形式 A0~An-1 W0 W(2n-1) D0 Dm

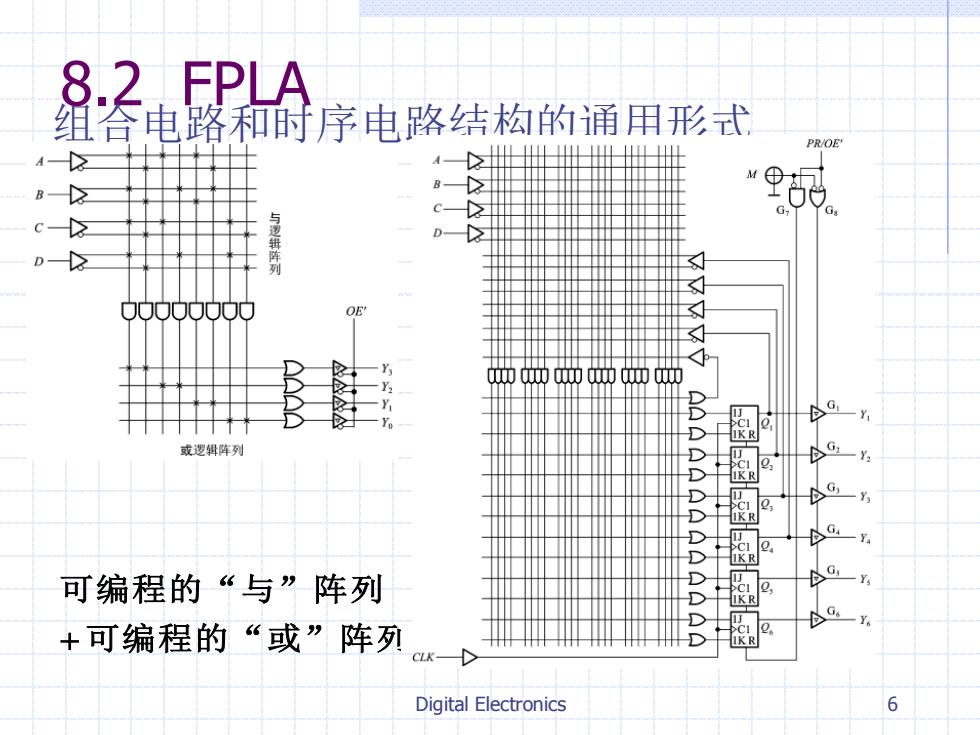

8.2 FPLA组合电路和时序电路结构的通用形式PRIOE4-“甲BB-V与迎辑阵列公C-D-OOOOOOOOE'RPO本KAY000000000000NG-YaaaaeYAe或逻辑阵列YQDy-YGY可编程的“与”阵列LGY+可编程的“或”阵列CLK-6Digital Electronics

Digital Electronics 6 8.2 FPLA 组合电路和时序电路结构的通用形式 可编程的“或”阵列 可编程的“与”阵列 +

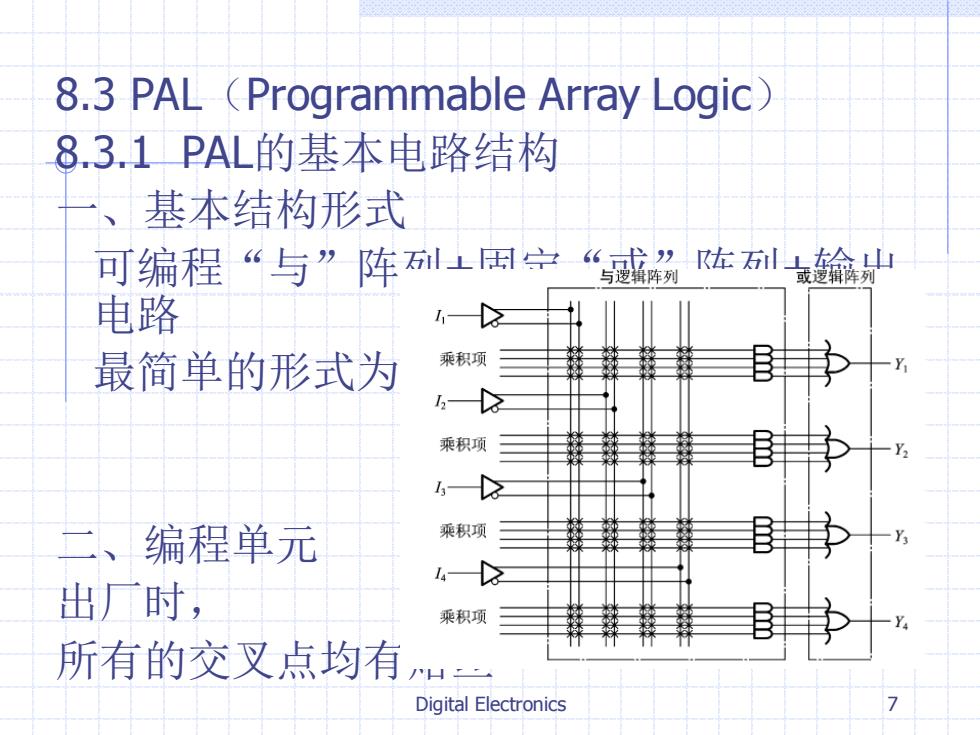

8.3PAL(ProgrammableArrayLogic)8.3.1PAL的基本电路结构、基本结构形式可编程“与”阵列上宁“”陈列输山逻摄阵陈发或逻辑阵列电路乘积项月一最简单的形式为2A乘积项BIY1乘积项BBD-Y编程单元14—之出厂时,乘积项2所有的交又点均有Digital Electronics

Digital Electronics 7 8.3 PAL(Programmable Array Logic) 8.3.1 PAL的基本电路结构 一、基本结构形式 可编程“与”阵列+固定“或”阵列+输出 电路 最简单的形式为: 二、编程单元 出厂时, 所有的交叉点均有熔丝

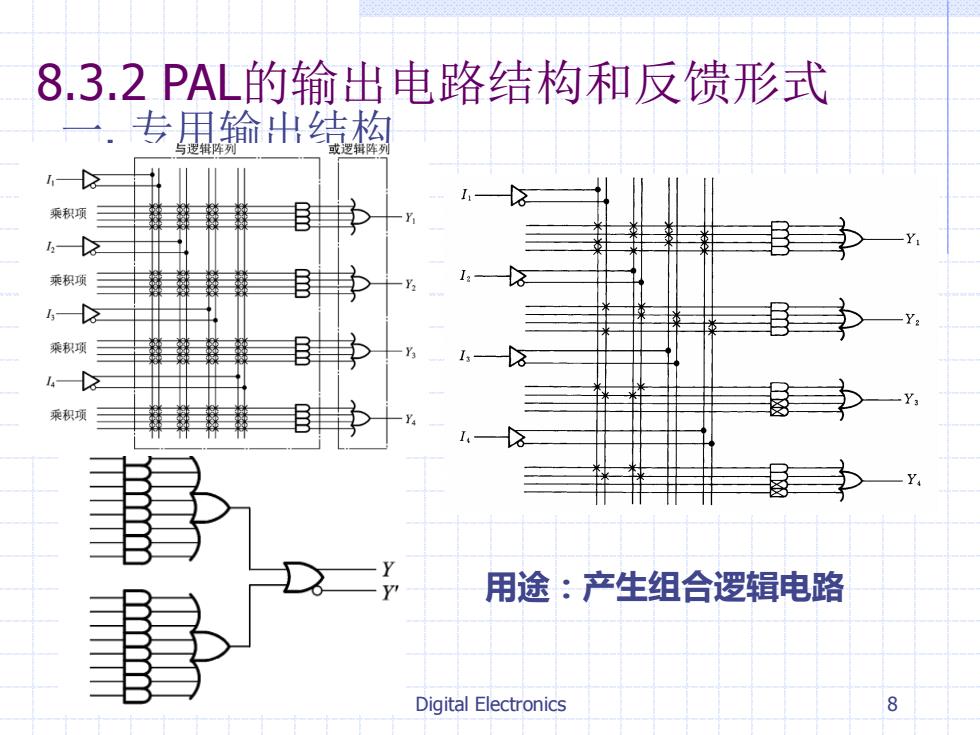

8.3.2PAL的输出电路结构和反馈形式专用输出结构X乘积项-7乘积项B.乘积项A乘积项I.-用途:产生组合逻辑电路Digital Electronics

Digital Electronics 8 8.3.2 PAL的输出电路结构和反馈形式 一. 专用输出结构 用途:产生组合逻辑电路

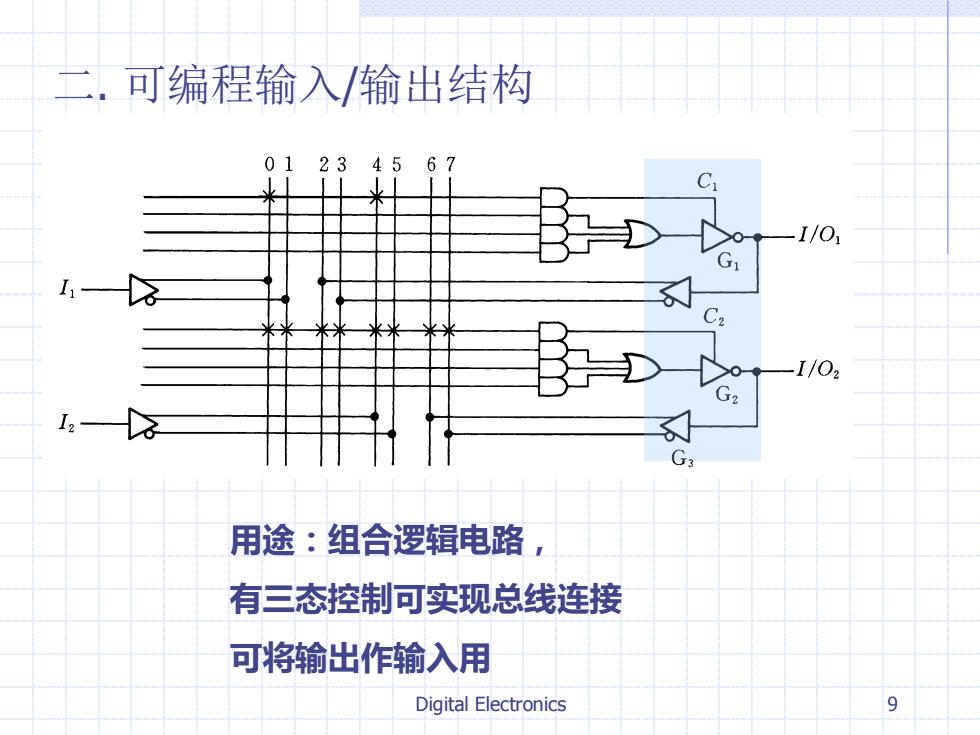

可编程输入/输出结构01234567H-1/0voGII,---1/02G2I2—AG3用途:组合逻辑电路有三态控制可实现总线连接可将输出作输入用9Digital Electronics

Digital Electronics 9 二. 可编程输入/输出结构 用途:组合逻辑电路, 有三态控制可实现总线连接 可将输出作输入用

三.寄存器输出结构CLKOEFFQDIDg'>C1Q'文I.9,FF2Q2D2ID-Q24>C1QL2Q2用途:产生时序逻辑电路10DigitalElectronics

Digital Electronics 10 三. 寄存器输出结构 用途:产生时序逻辑电路