正在加载图片...

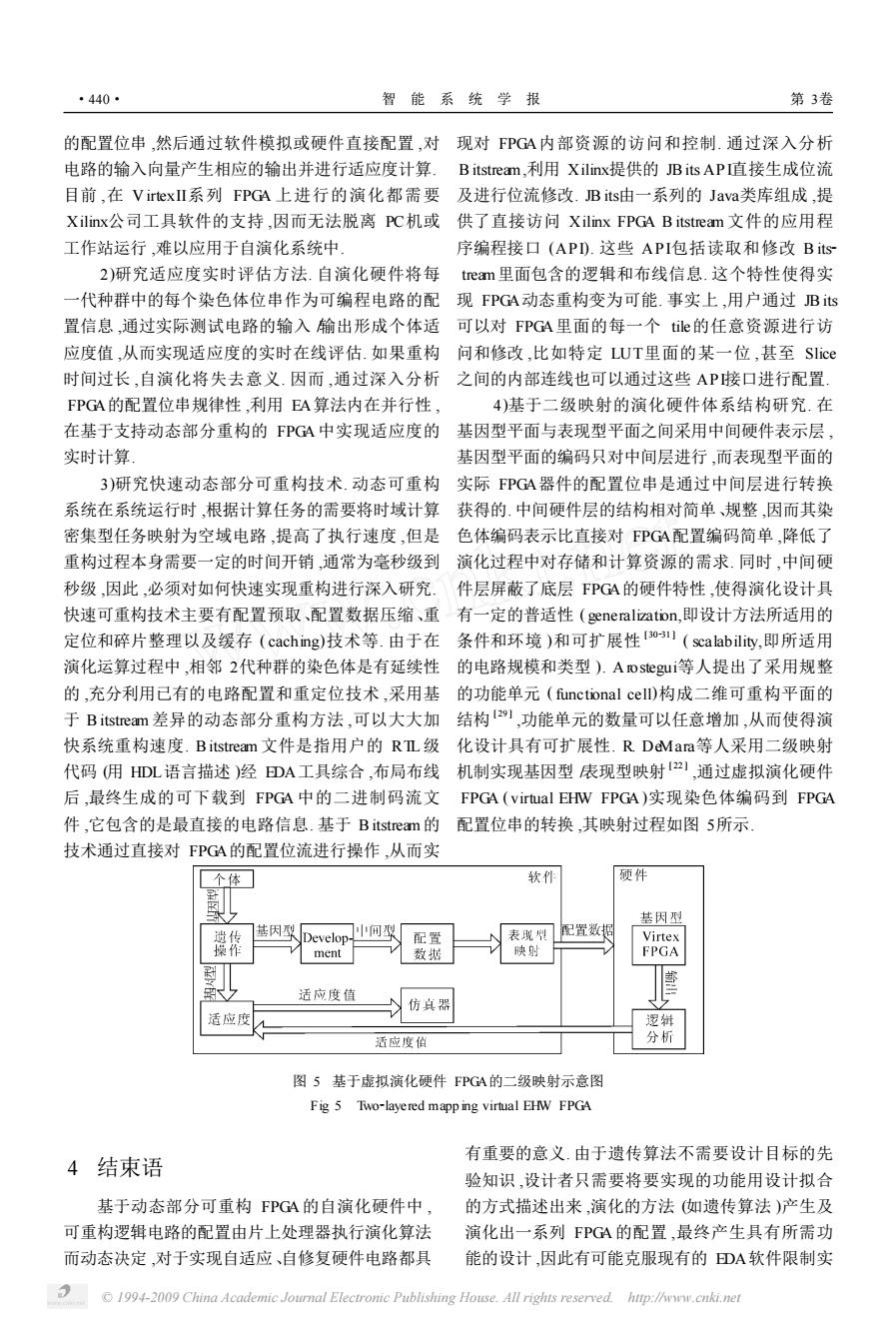

·440· 智能系统学报 第3卷 的配置位串,然后通过软件模拟或硬件直接配置,对现对FPGA内部资源的访问和控制.通过深入分析 电路的输入向量产生相应的输出并进行适应度计算.Bitstream,利用X ilinx提供的B its API直接生成位流 目前,在V irtexⅡ系列FPGA上进行的演化都需要及进行位流修改.Bits由一系列的Java类库组成,提 X ilinx公司工具软件的支持,因而无法脱离PC机或供了直接访问Xilinx FPGA B itstream文件的应用程 工作站运行,难以应用于自演化系统中 序编程接口(AP).这些API包括读取和修改Bits 2)研究适应度实时评估方法.自演化硬件将每team里面包含的逻辑和布线信息.这个特性使得实 一代种群中的每个染色体位串作为可编程电路的配现FPGA动态重构变为可能.事实上,用户通过Bs 置信息,通过实际测试电路的输入输出形成个体适可以对FPGA里面的每一个tle的任意资源进行访 应度值,从而实现适应度的实时在线评估.如果重构问和修改,比如特定UT里面的某一位,甚至Slic 时间过长,自演化将失去意义.因而,通过深入分析之间的内部连线也可以通过这些AP接口进行配置, FPGA的配置位串规律性,利用EA算法内在并行性, 4)基于二级映射的演化硬件体系结构研究.在 在基于支持动态部分重构的FPGA中实现适应度的基因型平面与表现型平面之间采用中间硬件表示层, 实时计算 基因型平面的编码只对中间层进行,而表现型平面的 3)研究快速动态部分可重构技术.动态可重构实际FPGA器件的配置位串是通过中间层进行转换 系统在系统运行时,根据计算任务的需要将时域计算获得的.中间硬件层的结构相对简单、规整,因而其染 密集型任务映射为空域电路,提高了执行速度,但是色体编码表示比直接对FPGA配置编码简单,降低了 重构过程本身需要一定的时间开销,通常为毫秒级到演化过程中对存储和计算资源的需求.同时,中间硬 秒级,因此,必须对如何快速实现重构进行深入研究.件层屏蔽了底层℉PGA的硬件特性,使得演化设计具 快速可重构技术主要有配置预取、配置数据压缩、重有一定的普适性(generalization,.即设计方法所适用的 定位和碎片整理以及缓存(caching)技术等.由于在条件和环境)和可扩展性o3](abiity,即所适用 演化运算过程中,相邻2代种群的染色体是有延续性的电路规模和类型).A rostegui等人提出了采用规整 的,充分利用已有的电路配置和重定位技术,采用基的功能单元(functional cell)构成二维可重构平面的 于Bitstream差异的动态部分重构方法,可以大大加结构29),功能单元的数量可以任意增加,从而使得演 快系统重构速度.Bitstream文件是指用户的RTL级化设计具有可扩展性.R.DeMara等人采用二级映射 代码(佣HDL语言描述)经DA工具综合,布局布线机制实现基因型俵现型映射2),通过虚拟演化硬件 后,最终生成的可下载到FPGA中的二进制码流文FPGA(virtual EHW FPGA)实现染色体编码到FPGA 件,它包含的是最直接的电路信息.基于Bitstream的 配置位串的转换,其映射过程如图5所示 技术通过直接对FPGA的配置位流进行操作,从而实 个 软件 硬件 基因型 遗传 基因型 Develop- 何型 配置 表现型 配置数据 Virtex 操作 ment 数据 映射 FPGA 到 适应度值 仿真器 适应度 逻拼 适应度伯 分析 图5基于虚拟演化硬件FPGA的二级映射示意图 Fig 5 Two-layered mapp ing virtual EHW FPGA 4结束语 有重要的意义.由于遗传算法不需要设计目标的先 验知识,设计者只需要将要实现的功能用设计拟合 基于动态部分可重构FPGA的自演化硬件中, 的方式描述出来,演化的方法(如遗传算法)产生及 可重构逻辑电路的配置由片上处理器执行演化算法 演化出一系列PGA的配置,最终产生具有所需功 而动态决定,对于实现自适应、自修复硬件电路都具 能的设计,因此有可能克服现有的DA软件限制实 1994-2009 China Academic Journal Electronic Publishing House.All rights reserved.http://www.cnki.net的配置位串 ,然后通过软件模拟或硬件直接配置 ,对 电路的输入向量产生相应的输出并进行适应度计算. 目前 ,在 V irtexII系列 FPGA 上进行的演化都需要 Xilinx公司工具软件的支持 ,因而无法脱离 PC机或 工作站运行 ,难以应用于自演化系统中. 2)研究适应度实时评估方法. 自演化硬件将每 一代种群中的每个染色体位串作为可编程电路的配 置信息 ,通过实际测试电路的输入 /输出形成个体适 应度值 ,从而实现适应度的实时在线评估. 如果重构 时间过长 ,自演化将失去意义. 因而 ,通过深入分析 FPGA的配置位串规律性 ,利用 EA算法内在并行性 , 在基于支持动态部分重构的 FPGA中实现适应度的 实时计算. 3)研究快速动态部分可重构技术. 动态可重构 系统在系统运行时 ,根据计算任务的需要将时域计算 密集型任务映射为空域电路 ,提高了执行速度 ,但是 重构过程本身需要一定的时间开销 ,通常为毫秒级到 秒级 ,因此 ,必须对如何快速实现重构进行深入研究. 快速可重构技术主要有配置预取、配置数据压缩、重 定位和碎片整理以及缓存 ( caching)技术等. 由于在 演化运算过程中 ,相邻 2代种群的染色体是有延续性 的 ,充分利用已有的电路配置和重定位技术 ,采用基 于 Bitstream 差异的动态部分重构方法 ,可以大大加 快系统重构速度. Bitstream 文件是指用户的 RTL 级 代码 (用 HDL语言描述 )经 EDA工具综合 ,布局布线 后 ,最终生成的可下载到 FPGA 中的二进制码流文 件 ,它包含的是最直接的电路信息. 基于 Bitstream的 技术通过直接对 FPGA的配置位流进行操作 ,从而实 现对 FPGA内部资源的访问和控制. 通过深入分析 B itstream,利用 Xilinx提供的 JBits API直接生成位流 及进行位流修改. JB its由一系列的 Java类库组成 ,提 供了直接访问 Xilinx FPGA B itstream 文件的应用程 序编程接口 (API). 这些 API包括读取和修改 B its2 tream里面包含的逻辑和布线信息. 这个特性使得实 现 FPGA动态重构变为可能. 事实上 ,用户通过 JB its 可以对 FPGA里面的每一个 tile的任意资源进行访 问和修改 ,比如特定 LUT里面的某一位 ,甚至 Slice 之间的内部连线也可以通过这些 API接口进行配置. 4)基于二级映射的演化硬件体系结构研究. 在 基因型平面与表现型平面之间采用中间硬件表示层 , 基因型平面的编码只对中间层进行 ,而表现型平面的 实际 FPGA器件的配置位串是通过中间层进行转换 获得的. 中间硬件层的结构相对简单、规整 ,因而其染 色体编码表示比直接对 FPGA配置编码简单 ,降低了 演化过程中对存储和计算资源的需求. 同时 ,中间硬 件层屏蔽了底层 FPGA的硬件特性 ,使得演化设计具 有一定的普适性 ( generalization,即设计方法所适用的 条件和环境 )和可扩展性 [ 30231 ] ( scalability,即所适用 的电路规模和类型 ). A rostegui等人提出了采用规整 的功能单元 ( functional cell)构成二维可重构平面的 结构 [ 29 ] ,功能单元的数量可以任意增加 ,从而使得演 化设计具有可扩展性. R. DeMara等人采用二级映射 机制实现基因型 /表现型映射 [ 22 ] ,通过虚拟演化硬件 FPGA ( virtual EHW FPGA )实现染色体编码到 FPGA 配置位串的转换 ,其映射过程如图 5所示. 图 5 基于虚拟演化硬件 FPGA的二级映射示意图 Fig. 5 Two2layered mapp ing virtual EHW FPGA 4 结束语 基于动态部分可重构 FPGA的自演化硬件中 , 可重构逻辑电路的配置由片上处理器执行演化算法 而动态决定 ,对于实现自适应、自修复硬件电路都具 有重要的意义. 由于遗传算法不需要设计目标的先 验知识 ,设计者只需要将要实现的功能用设计拟合 的方式描述出来 ,演化的方法 (如遗传算法 )产生及 演化出一系列 FPGA的配置 ,最终产生具有所需功 能的设计 ,因此有可能克服现有的 EDA软件限制实 ·440· 智 能 系 统 学 报 第 3卷 © 1994-2009 China Academic Journal Electronic Publishing House. All rights reserved. http://www.cnki.net