正在加载图片...

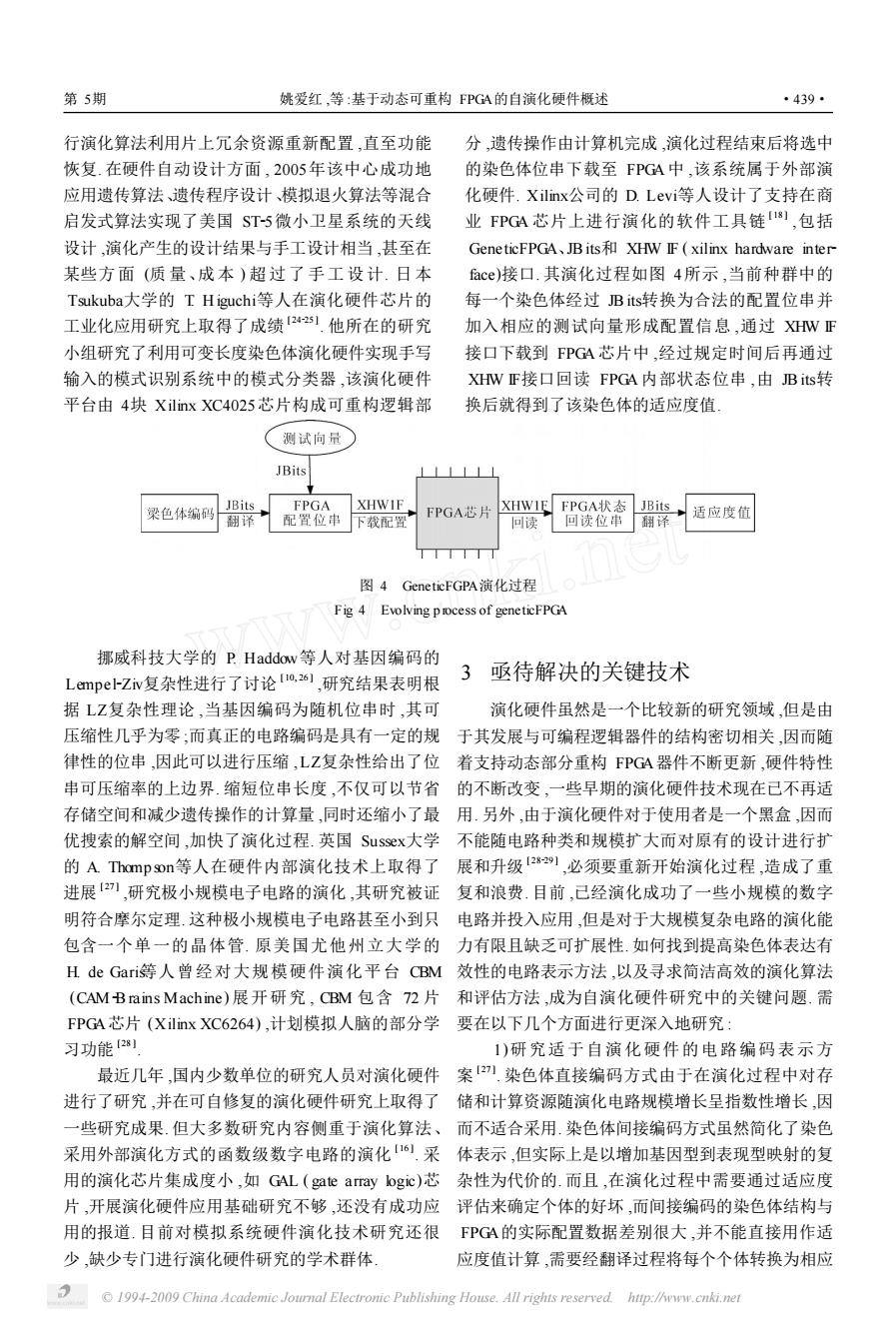

第5期 姚爱红,等:基于动态可重构FPGA的自演化硬件概述 ·439· 行演化算法利用片上冗余资源重新配置,直至功能 分,遗传操作由计算机完成,演化过程结束后将选中 恢复.在硬件自动设计方面,2005年该中心成功地 的染色体位串下载至FPGA中,该系统属于外部演 应用遗传算法、遗传程序设计、模拟退火算法等混合 化硬件.Xilinx公司的D.Levi等人设计了支持在商 启发式算法实现了美国ST-5微小卫星系统的天线 业FPGA芯片上进行演化的软件工具链,包括 设计,演化产生的设计结果与手工设计相当,甚至在 GeneticFPGA JBits XHW IF xilinx hardware inter- 某些方面(质量、成本)超过了手工设计.日本 fce)接口.其演化过程如图4所示,当前种群中的 Tsukuba大学的T Higuchi等人在演化硬件芯片的 每一个染色体经过Bts转换为合法的配置位串并 工业化应用研究上取得了成绩2421.他所在的研究 加入相应的测试向量形成配置信息,通过HWF 小组研究了利用可变长度染色体演化硬件实现手写 接口下载到FPGA芯片中,经过规定时间后再通过 输入的模式识别系统中的模式分类器,该演化硬件 XHWF接口回读FPGA内部状态位串,由Bits转 平台由4块Xilinx XC4025芯片构成可重构逻辑部 换后就得到了该染色体的适应度值 测试向量) JBits LLLLLI 梁色体编码 IBits EPga XHWIF 配置位串 FPGA芯片 XHWIE FPGA状态 JBits 翻译 下载配置 回读 回读位串 翻译 适应度值 TIII 图4 GeneticFGPA演化过程 Fig 4 Evolving process of geneticFPGA 挪威科技大学的P Haddow等人对基因编码的 Lempel-Ziv复杂性进行了讨论o,21,研究结果表明根 3亟待解决的关键技术 据LZ复杂性理论,当基因编码为随机位串时,其可 演化硬件虽然是一个比较新的研究领域,但是由 压缩性几乎为零;而真正的电路编码是具有一定的规于其发展与可编程逻辑器件的结构密切相关,因而随 律性的位串,因此可以进行压缩,LZ复杂性给出了位着支持动态部分重构FPGA器件不断更新,硬件特性 串可压缩率的上边界.缩短位串长度,不仅可以节省的不断改变,一些早期的演化硬件技术现在己不再适 存储空间和减少遗传操作的计算量,同时还缩小了最用.另外,由于演化硬件对于使用者是一个黑盒,因而 优搜索的解空间,加快了演化过程.英国Susx大学不能随电路种类和规模扩大而对原有的设计进行扩 的A.Thomp son等人在硬件内部演化技术上取得了展和升级28),必须要重新开始演化过程,造成了重 进展21,研究极小规模电子电路的演化,其研究被证复和浪费.目前,已经演化成功了一些小规模的数字 明符合摩尔定理.这种极小规模电子电路甚至小到只电路并投入应用,但是对于大规模复杂电路的演化能 包含一个单一的晶体管.原美国尤他州立大学的力有限且缺乏可扩展性.如何找到提高染色体表达有 H de Garis等人曾经对大规模硬件演化平台CBM效性的电路表示方法,以及寻求简洁高效的演化算法 (CAM B rains Machine)展开研究,CBM包含72片和评估方法,成为自演化硬件研究中的关键问题.需 FPGA芯片(Xilinx XC6264),计划模拟人脑的部分学要在以下几个方面进行更深入地研究: 习功能2] 1)研究适于自演化硬件的电路编码表示方 最近几年,国内少数单位的研究人员对演化硬件案2).染色体直接编码方式由于在演化过程中对存 进行了研究,并在可自修复的演化硬件研究上取得了储和计算资源随演化电路规模增长呈指数性增长,因 一些研究成果.但大多数研究内容侧重于演化算法、而不适合采用.染色体间接编码方式虽然简化了染色 采用外部演化方式的函数级数字电路的演化6).采体表示,但实际上是以增加基因型到表现型映射的复 用的演化芯片集成度小,如G4L(gate array logic)芯杂性为代价的.而且,在演化过程中需要通过适应度 片,开展演化硬件应用基础研究不够,还没有成功应评估来确定个体的好坏,而间接编码的染色体结构与 用的报道.目前对模拟系统硬件演化技术研究还很FPGA的实际配置数据差别很大,并不能直接用作适 少,缺少专门进行演化硬件研究的学术群体 应度值计算,需要经翻译过程将每个个体转换为相应 1994-2009 China Academic Journal Electronic Publishing House.All rights reserved.http://www.cnki.net行演化算法利用片上冗余资源重新配置 ,直至功能 恢复. 在硬件自动设计方面 , 2005年该中心成功地 应用遗传算法、遗传程序设计、模拟退火算法等混合 启发式算法实现了美国 ST25微小卫星系统的天线 设计 ,演化产生的设计结果与手工设计相当 ,甚至在 某些方面 (质 量、成 本 ) 超 过了手工 设计. 日本 Tsukuba大学的 T. H iguchi等人在演化硬件芯片的 工业化应用研究上取得了成绩 [ 24225 ] . 他所在的研究 小组研究了利用可变长度染色体演化硬件实现手写 输入的模式识别系统中的模式分类器 ,该演化硬件 平台由 4块 Xilinx XC4025芯片构成可重构逻辑部 分 ,遗传操作由计算机完成 ,演化过程结束后将选中 的染色体位串下载至 FPGA中 ,该系统属于外部演 化硬件. Xilinx公司的 D. Levi等人设计了支持在商 业 FPGA 芯片上进行演化的软件工具链 [ 18 ] ,包括 GeneticFPGA、JBits和 XHW IF ( xilinx hardware inter2 face)接口. 其演化过程如图 4所示 ,当前种群中的 每一个染色体经过 JBits转换为合法的配置位串并 加入相应的测试向量形成配置信息 ,通过 XHW IF 接口下载到 FPGA芯片中 ,经过规定时间后再通过 XHW IF接口回读 FPGA 内部状态位串 ,由 JBits转 换后就得到了该染色体的适应度值. 图 4 GeneticFGPA演化过程 Fig. 4 Evolving p rocess of geneticFPGA 挪威科技大学的 P. Haddow等人对基因编码的 Lempel2Ziv复杂性进行了讨论 [ 10, 26 ] ,研究结果表明根 据 LZ复杂性理论 ,当基因编码为随机位串时 ,其可 压缩性几乎为零 ;而真正的电路编码是具有一定的规 律性的位串 ,因此可以进行压缩 , LZ复杂性给出了位 串可压缩率的上边界. 缩短位串长度 ,不仅可以节省 存储空间和减少遗传操作的计算量 ,同时还缩小了最 优搜索的解空间 ,加快了演化过程. 英国 Sussex大学 的 A. Thomp son等人在硬件内部演化技术上取得了 进展 [ 27 ] ,研究极小规模电子电路的演化 ,其研究被证 明符合摩尔定理. 这种极小规模电子电路甚至小到只 包含一个单一的晶体管. 原美国尤他州立大学的 H. de Garis等人曾经对大规模硬件演化平台 CBM (CAM2B rains Machine ) 展开研究 , CBM 包含 72 片 FPGA芯片 (Xilinx XC6264) ,计划模拟人脑的部分学 习功能 [ 28 ] . 最近几年 ,国内少数单位的研究人员对演化硬件 进行了研究 ,并在可自修复的演化硬件研究上取得了 一些研究成果. 但大多数研究内容侧重于演化算法、 采用外部演化方式的函数级数字电路的演化 [ 16 ] . 采 用的演化芯片集成度小 ,如 GAL ( gate array logic)芯 片 ,开展演化硬件应用基础研究不够 ,还没有成功应 用的报道. 目前对模拟系统硬件演化技术研究还很 少 ,缺少专门进行演化硬件研究的学术群体. 3 亟待解决的关键技术 演化硬件虽然是一个比较新的研究领域 ,但是由 于其发展与可编程逻辑器件的结构密切相关 ,因而随 着支持动态部分重构 FPGA器件不断更新 ,硬件特性 的不断改变 ,一些早期的演化硬件技术现在已不再适 用. 另外 ,由于演化硬件对于使用者是一个黑盒 ,因而 不能随电路种类和规模扩大而对原有的设计进行扩 展和升级 [ 28229 ] ,必须要重新开始演化过程 ,造成了重 复和浪费. 目前 ,已经演化成功了一些小规模的数字 电路并投入应用 ,但是对于大规模复杂电路的演化能 力有限且缺乏可扩展性. 如何找到提高染色体表达有 效性的电路表示方法 ,以及寻求简洁高效的演化算法 和评估方法 ,成为自演化硬件研究中的关键问题. 需 要在以下几个方面进行更深入地研究 : 1)研究适于自演化硬件的电路编码表示方 案 [ 27 ] . 染色体直接编码方式由于在演化过程中对存 储和计算资源随演化电路规模增长呈指数性增长 ,因 而不适合采用. 染色体间接编码方式虽然简化了染色 体表示 ,但实际上是以增加基因型到表现型映射的复 杂性为代价的. 而且 ,在演化过程中需要通过适应度 评估来确定个体的好坏 ,而间接编码的染色体结构与 FPGA的实际配置数据差别很大 ,并不能直接用作适 应度值计算 ,需要经翻译过程将每个个体转换为相应 第 5期 姚爱红 ,等 :基于动态可重构 FPGA的自演化硬件概述 ·439· © 1994-2009 China Academic Journal Electronic Publishing House. All rights reserved. http://www.cnki.net