正在加载图片...

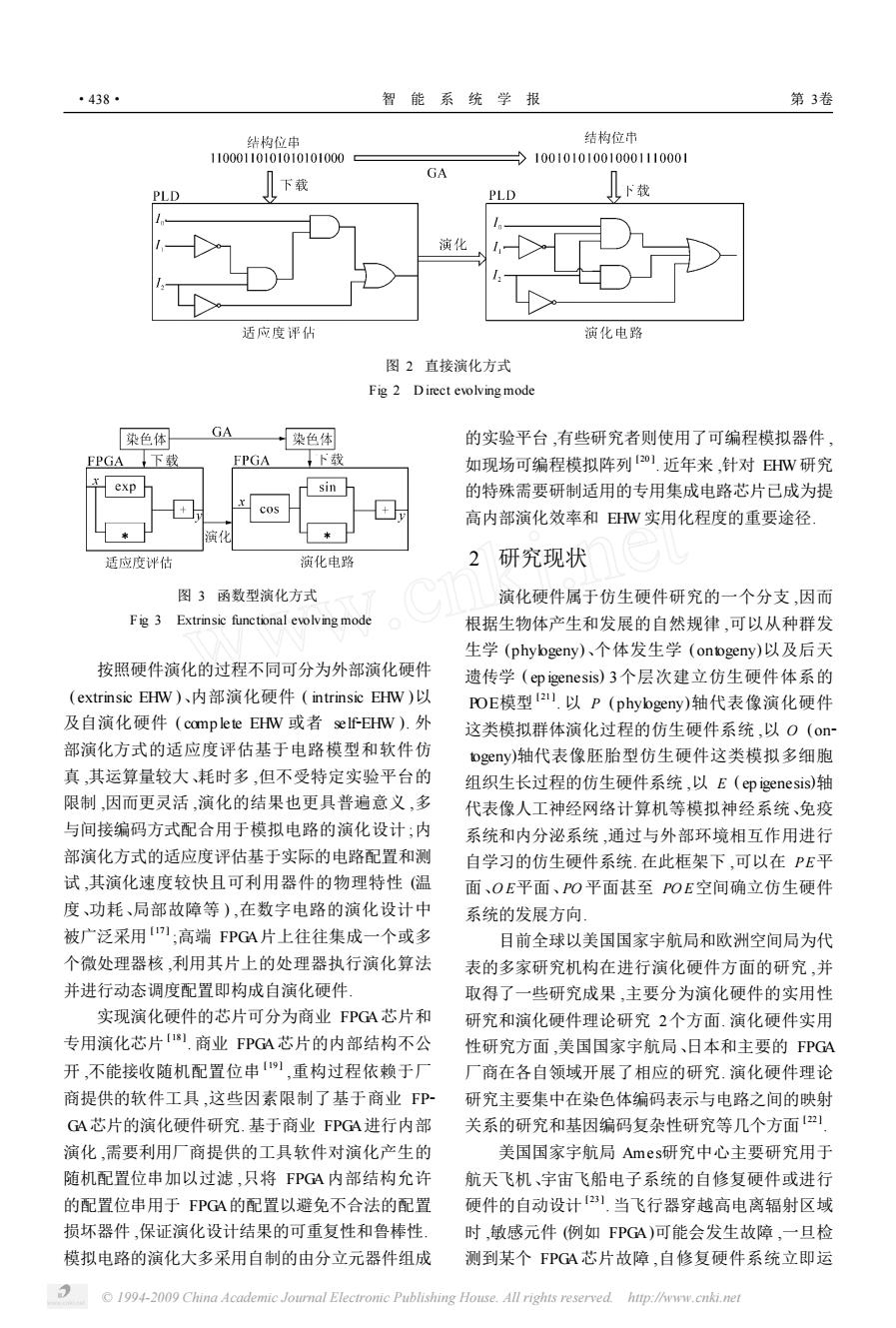

·438- 智能系统学报 第3卷 结构位串 结构位市 11000110101010101000 >100101010010001110001 GA 下载 PLD PLD 卜截 演化 适应度评仙 演化电路 图2直接演化方式 Fig 2 Direct evolving mode 染色体 GA 染色体 的实验平台,有些研究者则使用了可编程模拟器件 FPGA下载 FPGA 下载 如现场可编程模拟阵列2o].近年来,针对EHW研究 exp sin 的特殊需要研制适用的专用集成电路芯片已成为提 cos 高内部演化效率和EHW实用化程度的重要途径 适应度评估 演化电路 2 研究现状 图3函数型演化方式 演化硬件属于仿生硬件研究的一个分支,因而 Fig 3 Extrinsic functional evolving mode 根据生物体产生和发展的自然规律,可以从种群发 生学(phybgeny)、个体发生学(ontogeny)以及后天 按照硬件演化的过程不同可分为外部演化硬件 遗传学(ep igenesis)3个层次建立仿生硬件体系的 (extrinsic EHW)、内部演化硬件(intrinsic EHW)以 oE模型I2).以P(phybgeny)轴代表像演化硬件 及自演化硬件(complete EHW或者se lf-EHW).外 这类模拟群体演化过程的仿生硬件系统,以O(o~ 部演化方式的适应度评估基于电路模型和软件仿 togeny)轴代表像胚胎型仿生硬件这类模拟多细胞 真,其运算量较大、耗时多,但不受特定实验平台的 组织生长过程的仿生硬件系统,以E(ep igenesis)轴 限制,因而更灵活,演化的结果也更具普遍意义,多 代表像人工神经网络计算机等模拟神经系统、免疫 与间接编码方式配合用于模拟电路的演化设计;内 系统和内分泌系统,通过与外部环境相互作用进行 部演化方式的适应度评估基于实际的电路配置和测 自学习的仿生硬件系统.在此框架下,可以在PE平 试,其演化速度较快且可利用器件的物理特性(温 面、OE平面、PO平面甚至POE空间确立仿生硬件 度、功耗、局故障等),在数字电路的演化设计中 系统的发展方向。 被广泛采用1:高端FPGA片上往往集成一个或多 目前全球以美国国家宇航局和欧洲空间局为代 个微处理器核,利用其片上的处理器执行演化算法 表的多家研究机构在进行演化硬件方面的研究,并 并进行动态调度配置即构成自演化硬件 取得了一些研究成果,主要分为演化硬件的实用性 实现演化硬件的芯片可分为商业FPGA芯片和 研究和演化硬件理论研究2个方面.演化硬件实用 专用演化芯片1,商业FPGA芯片的内部结构不公 性研究方面,美国国家宇航局、日本和主要的FPGA 开,不能接收随机配置位串,重构过程依赖于厂 厂商在各自领域开展了相应的研究.演化硬件理论 商提供的软件工具,这些因素限制了基于商业FP- 研究主要集中在染色体编码表示与电路之间的映射 GA芯片的演化硬件研究.基于商业FPGA进行内部 关系的研究和基因编码复杂性研究等几个方面) 演化,需要利用厂商提供的工具软件对演化产生的 美国国家宇航局Ames研究中心主要研究用于 随机配置位串加以过滤,只将FPGA内部结构允许 航天飞机、宇宙飞船电子系统的自修复硬件或进行 的配置位串用于FPGA的配置以避免不合法的配置 硬件的自动设计2).当飞行器穿越高电离辐射区域 损坏器件,保证演化设计结果的可重复性和鲁棒性. 时,敏感元件(例如FPGA)可能会发生故障,一旦检 模拟电路的演化大多采用自制的由分立元器件组成 测到某个FPGA芯片故障,自修复硬件系统立即运 1994-2009 China Academic Journal Electronic Publishing House.All rights reserved http://www.cnki.net图 2 直接演化方式 Fig. 2 D irect evolving mode 图 3 函数型演化方式 Fig. 3 Extrinsic functional evolving mode 按照硬件演化的过程不同可分为外部演化硬件 ( extrinsic EHW )、内部演化硬件 ( intrinsic EHW )以 及自演化硬件 ( comp lete EHW 或者 self2EHW ). 外 部演化方式的适应度评估基于电路模型和软件仿 真 ,其运算量较大、耗时多 ,但不受特定实验平台的 限制 ,因而更灵活 ,演化的结果也更具普遍意义 ,多 与间接编码方式配合用于模拟电路的演化设计 ;内 部演化方式的适应度评估基于实际的电路配置和测 试 ,其演化速度较快且可利用器件的物理特性 (温 度、功耗、局部故障等 ) ,在数字电路的演化设计中 被广泛采用 [ 17 ] ;高端 FPGA片上往往集成一个或多 个微处理器核 ,利用其片上的处理器执行演化算法 并进行动态调度配置即构成自演化硬件. 实现演化硬件的芯片可分为商业 FPGA芯片和 专用演化芯片 [ 18 ] . 商业 FPGA芯片的内部结构不公 开 ,不能接收随机配置位串 [ 19 ] ,重构过程依赖于厂 商提供的软件工具 ,这些因素限制了基于商业 FP2 GA芯片的演化硬件研究. 基于商业 FPGA进行内部 演化 ,需要利用厂商提供的工具软件对演化产生的 随机配置位串加以过滤 ,只将 FPGA 内部结构允许 的配置位串用于 FPGA的配置以避免不合法的配置 损坏器件 ,保证演化设计结果的可重复性和鲁棒性. 模拟电路的演化大多采用自制的由分立元器件组成 的实验平台 ,有些研究者则使用了可编程模拟器件 , 如现场可编程模拟阵列 [ 20 ] . 近年来 ,针对 EHW 研究 的特殊需要研制适用的专用集成电路芯片已成为提 高内部演化效率和 EHW 实用化程度的重要途径. 2 研究现状 演化硬件属于仿生硬件研究的一个分支 ,因而 根据生物体产生和发展的自然规律 ,可以从种群发 生学 (phylogeny)、个体发生学 ( ontogeny)以及后天 遗传学 ( ep igenesis) 3个层次建立仿生硬件体系的 POE模型 [ 21 ] . 以 P ( phylogeny)轴代表像演化硬件 这类模拟群体演化过程的仿生硬件系统 ,以 O (on2 togeny)轴代表像胚胎型仿生硬件这类模拟多细胞 组织生长过程的仿生硬件系统 ,以 E ( ep igenesis)轴 代表像人工神经网络计算机等模拟神经系统、免疫 系统和内分泌系统 ,通过与外部环境相互作用进行 自学习的仿生硬件系统. 在此框架下 ,可以在 PE平 面、O E平面、PO 平面甚至 PO E空间确立仿生硬件 系统的发展方向. 目前全球以美国国家宇航局和欧洲空间局为代 表的多家研究机构在进行演化硬件方面的研究 ,并 取得了一些研究成果 ,主要分为演化硬件的实用性 研究和演化硬件理论研究 2个方面. 演化硬件实用 性研究方面 ,美国国家宇航局、日本和主要的 FPGA 厂商在各自领域开展了相应的研究. 演化硬件理论 研究主要集中在染色体编码表示与电路之间的映射 关系的研究和基因编码复杂性研究等几个方面 [ 22 ] . 美国国家宇航局 Ames研究中心主要研究用于 航天飞机、宇宙飞船电子系统的自修复硬件或进行 硬件的自动设计 [ 23 ] . 当飞行器穿越高电离辐射区域 时 ,敏感元件 (例如 FPGA)可能会发生故障 ,一旦检 测到某个 FPGA芯片故障 ,自修复硬件系统立即运 ·438· 智 能 系 统 学 报 第 3卷 © 1994-2009 China Academic Journal Electronic Publishing House. All rights reserved. http://www.cnki.net