正在加载图片...

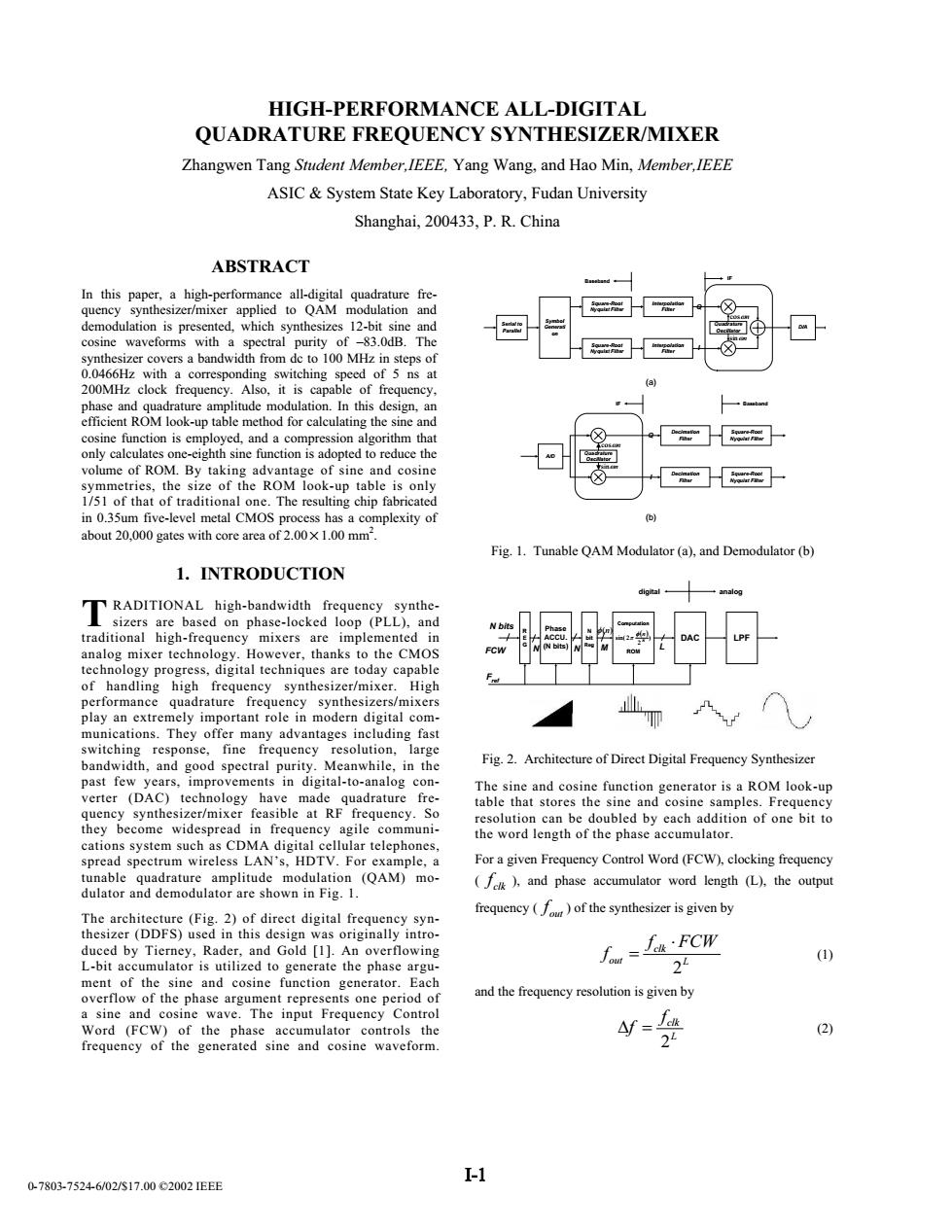

HIGH-PERFORMANCE ALL-DIGITAL QUADRATURE FREQUENCY SYNTHESIZER/MIXER Zhangwen Tang Student Member,IEEE,Yang Wang,and Hao Min,Member,IEEE ASIC System State Key Laboratory,Fudan University Shanghai.200433.P.R.China ABSTRACT In this paper,a high-performance all-digital quadrature fre- quency synthesizer/mixer applied to QAM modulation and demodulation is presented,which synthesizes 12-bit sine and cosine waveforms with a spectral purity of -83.0dB.The synthesizer covers a bandwidth from dc to 100 MHz in steps of 0.0466Hz with a corresponding switching speed of 5 ns at 200MHz clock frequency.Also,it is capable of frequency, (a) phase and quadrature amplitude modulation.In this design,an efficient ROM look-up table method for calculating the sine and cosine function is employed,and a compression algorithm that only calculates one-eighth sine function is adopted to reduce the volume of ROM.By taking advantage of sine and cosine symmetries,the size of the ROM look-up table is only 1/51 of that of traditional one.The resulting chip fabricated in 0.35um five-level metal CMOS process has a complexity of ) about 20,000 gates with core area of 2.00X 1.00 mm Fig.1.Tunable QAM Modulator(a),and Demodulator (b) 1.INTRODUCTION ephme-leled L traditional high-frequency mixers are implemented in analog mixer technology.However,thanks to the CMOS technology progress,digital techniques are today capable of handling high frequency synthesizer/mixer.High performance quadrature frequency synthesizers/mixers play an extremely important role in modern digital com- munications.They offer many advantages including fast switching response,fine frequency resolution,large bandwidth,and good spectral purity.Meanwhile,in the Fig.2.Architecture of Direct Digital Frequency Synthesizer past few years,improvements in digital-to-analog con- The sine and cosine function generator is a ROM look-up verter (DAC)technology have made quadrature fre- table that stores the sine and cosine samples.Frequency quency synthesizer/mixer feasible at RF frequency.So resolution can be doubled by each addition of one bit to they become widespread in frequency agile communi- the word length of the phase accumulator. cations system such as CDMA digital cellular telephones, spread spectrum wireless LAN's,HDTV.For example,a For a given Frequency Control Word(FCW),clocking frequency tunable quadrature amplitude modulation (QAM)mo- ()and phase accumulator word length (L),the output dulator and demodulator are shown in Fig.1. The architecture (Fig.2)of direct digital frequency syn- frequency (of the synthesizer is given by thesizer(DDFS)used in this design was originally intro- duced by Tierney,Rader,and Gold [1].An overflowing -&·FCm (1) L-bit accumulator is utilized to generate the phase argu- 24 ment of the sine and cosine function generator.Each overflow of the phase argument represents one period of and the frequency resolution is given by a sine and cosine wave.The input Frequency Control Word (FCW)of the phase accumulator controls the frequency of the generated sine and cosine waveform. 2 (2) I-1 0-7803-75246/02/S17.00⊙2002IEEEHIGH-PERFORMANCE ALL-DIGITAL QUADRATURE FREQUENCY SYNTHESIZER/MIXER Zhangwen Tang Student Member,IEEE, Yang Wang, and Hao Min, Member,IEEE ASIC & System State Key Laboratory, Fudan University Shanghai, 200433, P. R. China ABSTRACT In this paper, a high-performance all-digital quadrature frequency synthesizer/mixer applied to QAM modulation and demodulation is presented, which synthesizes 12-bit sine and cosine waveforms with a spectral purity of –83.0dB. The synthesizer covers a bandwidth from dc to 100 MHz in steps of 0.0466Hz with a corresponding switching speed of 5 ns at 200MHz clock frequency. Also, it is capable of frequency, phase and quadrature amplitude modulation. In this design, an efficient ROM look-up table method for calculating the sine and cosine function is employed, and a compression algorithm that only calculates one-eighth sine function is adopted to reduce the volume of ROM. By taking advantage of sine and cosine symmetries, the size of the ROM look-up table is only 1/51 of that of traditional one. The resulting chip fabricated in 0.35um five-level metal CMOS process has a complexity of about 20,000 gates with core area of 2.00ᱢ1.00 mm2 . 1. INTRODUCTION RADITIONAL high-bandwidth frequency synthesizers are based on phase-locked loop (PLL), and traditional high-frequency mixers are implemented in analog mixer technology. However, thanks to the CMOS technology progress, digital techniques are today capable of handling high frequency synthesizer/mixer. High performance quadrature frequency synthesizers/mixers play an extremely important role in modern digital communications. They offer many advantages including fast switching response, fine frequency resolution, large bandwidth, and good spectral purity. Meanwhile, in the past few years, improvements in digital-to-analog converter (DAC) technology have made quadrature frequency synthesizer/mixer feasible at RF frequency. So they become widespread in frequency agile communications system such as CDMA digital cellular telephones, spread spectrum wireless LAN’s, HDTV. For example, a tunable quadrature amplitude modulation (QAM) modulator and demodulator are shown in Fig. 1. The architecture (Fig. 2) of direct digital frequency synthesizer (DDFS) used in this design was originally introduced by Tierney, Rader, and Gold [1]. An overflowing L-bit accumulator is utilized to generate the phase argument of the sine and cosine function generator. Each overflow of the phase argument represents one period of a sine and cosine wave. The input Frequency Control Word (FCW) of the phase accumulator controls the frequency of the generated sine and cosine waveform. The sine and cosine function generator is a ROM look-up table that stores the sine and cosine samples. Frequency resolution can be doubled by each addition of one bit to the word length of the phase accumulator. For a given Frequency Control Word (FCW), clocking frequency ( clk f ), and phase accumulator word length (L), the output frequency ( out f ) of the synthesizer is given by 2 clk out L f FCW f (1) and the frequency resolution is given by 2 clk L f ' f (2) T Serial to Parallel Symbol Generati on Square-Root Nyquist Filter Square-Root Nyquist Filter Interpolation Filter Interpolation Filter D/A Quadrature Oscillator sinZn cosZn Baseband IF Q I A/D Quadrature Oscillator IF Decimation Filter Decimation Filter Square-Root Nyquist Filter Square-Root Nyquist Filter Q I Baseband (a) (b) sinZn cosZn Fig. 1. Tunable QAM Modulator (a), and Demodulator (b) R E G Phase ACCU. (N bits) N bit Reg Computation ROM DAC LPF N bits N M L FCW N

) 2 sin( 2 N I n S Fref I(n) digital analog Fig. 2. Architecture of Direct Digital Frequency Synthesizer 0-7803-7523-8/02/$17.00 ©2002 IEEE I-1 0-7803-7524-6/02/$17.00 ©2002 IEEE�