正在加载图片...

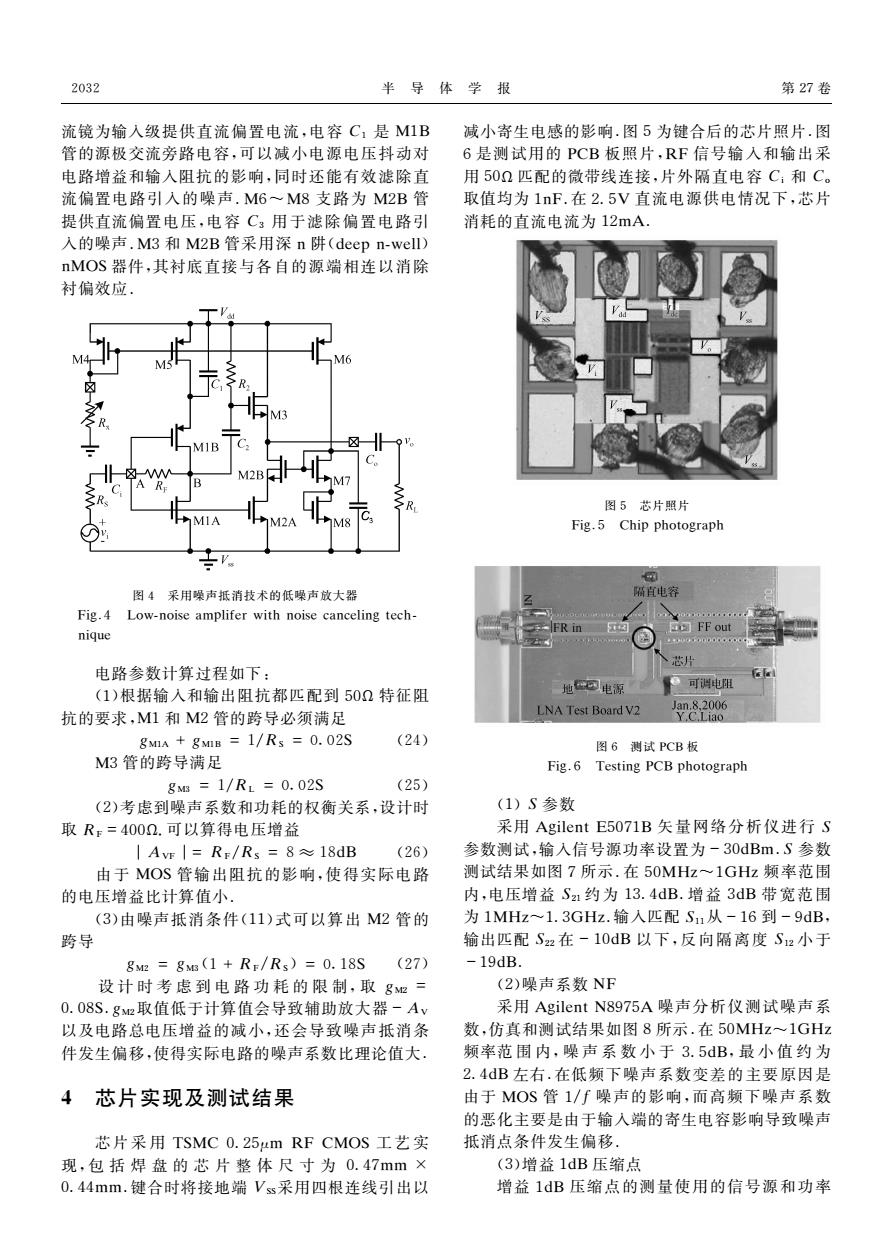

2032 半导体学报 第27卷 流镜为输入级提供直流偏置电流,电容C1是M1B 减小寄生电感的影响.图5为键合后的芯片照片.图 管的源极交流旁路电容,可以减小电源电压抖动对 6是测试用的PCB板照片,RF信号输入和输出采 电路增益和输入阻抗的影响,同时还能有效滤除直 用502匹配的微带线连接,片外隔直电容C:和C。 流偏置电路引入的噪声.M6~M8支路为M2B管 取值均为1nF.在2.5V直流电源供电情况下,芯片 提供直流偏置电压,电容C:用于滤除偏置电路引 消耗的直流电流为12mA. 入的噪声.M3和M2B管采用深n阱(deep n-well) nMOS器件,其衬底直接与各自的源端相连以消除 衬偏效应 M2B 图5芯片照片 Fig.5 Chip photograph 图4采用噪声抵消技术的低噪声放大器 隔直电容 Fig.4 Low-noise amplifer with noise canceling tech FF out nique 。¥040000ae0 芯片 电路参数计算过程如下: (1)根据输入和输出阻抗都匹配到50Ω特征阻 地回电源 P可腾电阻 Jan.82006 抗的要求,M1和M2管的跨导必须满足 LNA Test Board V2 Y.C.Liao 8MA 8MIB 1/Rs 0.02S (24) 图6测试PCB板 M3管的跨导满足 Fig.6 Testing PCB photograph gMs 1/RL 0.02S (25) (2)考虑到噪声系数和功耗的权衡关系,设计时 (1)S参数 取Rr=4002.可以算得电压增益 采用Agilent E5071B矢量网络分析仪进行S |Avw|=RF/Rs=8≈18dB (26) 参数测试,输入信号源功率设置为-30dBm.S参数 由于MOS管输出阻抗的影响,使得实际电路 测试结果如图7所示.在50MHz~1GHz频率范围 的电压增益比计算值小. 内,电压增益S21约为13.4dB.增益3dB带宽范围 (3)由噪声抵消条件(11)式可以算出M2管的 为1MHz~1.3GHz.输入匹配S11从-16到-9dB, 跨导 输出匹配S22在-10dB以下,反向隔离度S2小于 8M2=8s(1+Rr/Rs)=0.18S(27) -19dB. 设计时考虑到电路功耗的限制,取ge= (2)噪声系数NF 0.08S.g2取值低于计算值会导致辅助放大器-Av 采用Agilent N8975A噪声分析仪测试噪声系 以及电路总电压增益的减小,还会导致噪声抵消条 数,仿真和测试结果如图8所示.在50MHz~1GHz 件发生偏移,使得实际电路的噪声系数比理论值大. 频率范围内,噪声系数小于3.5dB,最小值约为 2.4dB左右.在低频下噪声系数变差的主要原因是 4芯片实现及测试结果 由于MOS管1/f噪声的影响,而高频下噪声系数 的恶化主要是由于输入端的寄生电容影响导致噪声 芯片采用TSMC0.25 um RF CMOS工艺实 抵消点条件发生偏移. 现,包括焊盘的芯片整体尺寸为0.47mm× (3)增益1dB压缩点 0.44mm.键合时将接地端Vs采用四根连线引出以 增益1dB压缩点的测量使用的信号源和功率半 导 体 学 报 第27卷 流镜为输入级提供直流偏置电流,电容 犆1 是 犕1犅 管的源极交流旁路电容,可以减小电源电压抖动对 电路增益和输入阻抗的影响,同时还能有效滤除直 流偏置电路引入的噪声.犕6~犕8支路为 犕2犅 管 提供直流偏置电压,电容 犆3 用于滤除偏置电路引 入的噪声.犕3和 犕2犅管采用深狀阱(犱犲犲狆狀狑犲犾犾) 狀犕犗犛器件,其衬底直接与各自的源端相连以消除 衬偏效应. 图4 采用噪声抵消技术的低噪声放大器 犉犻犵.4 犔狅狑狀狅犻狊犲犪犿狆犾犻犳犲狉狑犻狋犺狀狅犻狊犲犮犪狀犮犲犾犻狀犵狋犲犮犺 狀犻狇狌犲 电路参数计算过程如下: (1)根据输入和输出阻抗都匹配到50Ω 特征阻 抗的要求,犕1和 犕2管的跨导必须满足 犵犕1犃 +犵犕1犅 =1/犚犛 =0.02犛 (24) 犕3管的跨导满足 犵犕3 =1/犚犔 =0.02犛 (25) (2)考虑到噪声系数和功耗的权衡关系,设计时 取 犚犉=400Ω.可以算得电压增益 狘犃犞犉狘= 犚犉/犚犛 =8≈18犱犅 (26) 由于 犕犗犛管输出阻抗的影响,使得实际电路 的电压增益比计算值小. (3)由噪声抵消条件(11)式可以算出 犕2管的 跨导 犵犕2 =犵犕3(1+犚犉/犚犛)=0.18犛 (27) 设 计 时 考 虑 到 电 路 功 耗 的 限 制,取 犵犕2 = 008犛.犵犕2取值低于计算值会导致辅助放大器-犃犞 以及电路总电压增益的减小,还会导致噪声抵消条 件发生偏移,使得实际电路的噪声系数比理论值大. 4 芯片实现及测试结果 芯片 采 用 犜犛犕犆025μ犿 犚犉 犆犕犗犛 工 艺 实 现,包 括 焊 盘 的 芯 片 整 体 尺 寸 为 047犿犿 × 044犿犿.键合时将接地端 犞犛犛采用四根连线引出以 减小寄生电感的影响.图5为键合后的芯片照片.图 6是测试用的 犘犆犅 板照片,犚犉 信号输入和输出采 用50Ω 匹配的微带线连接,片外隔直电容 犆犻 和 犆狅 取值均为1狀犉.在25犞 直流电源供电情况下,芯片 消耗的直流电流为12犿犃. 图5 芯片照片 犉犻犵.5 犆犺犻狆狆犺狅狋狅犵狉犪狆犺 图6 测试 犘犆犅板 犉犻犵.6 犜犲狊狋犻狀犵犘犆犅狆犺狅狋狅犵狉犪狆犺 (1)犛 参数 采用 犃犵犻犾犲狀狋犈5071犅 矢量网络分析仪进行 犛 参数测试,输入信号源功率设置为-30犱犅犿.犛 参数 测试结果如图7所示.在50犕犎狕~1犌犎狕频率范围 内,电压增益 犛21 约为134犱犅.增益3犱犅 带宽范围 为1犕犎狕~13犌犎狕.输入匹配犛11从-16到-9犱犅, 输出匹配犛22 在-10犱犅 以下,反向隔离度 犛12 小于 -19犱犅. (2)噪声系数 犖犉 采用 犃犵犻犾犲狀狋犖8975犃 噪声分析仪测试噪声系 数,仿真和测试结果如图8所示.在50犕犎狕~1犌犎狕 频率范 围 内,噪 声 系 数 小 于 35犱犅,最 小 值 约 为 24犱犅左右.在低频下噪声系数变差的主要原因是 由于 犕犗犛管1/犳噪声的影响,而高频下噪声系数 的恶化主要是由于输入端的寄生电容影响导致噪声 抵消点条件发生偏移. (3)增益1犱犅压缩点 增益1犱犅 压缩点的测量使用的信号源和功率 2032