正在加载图片...

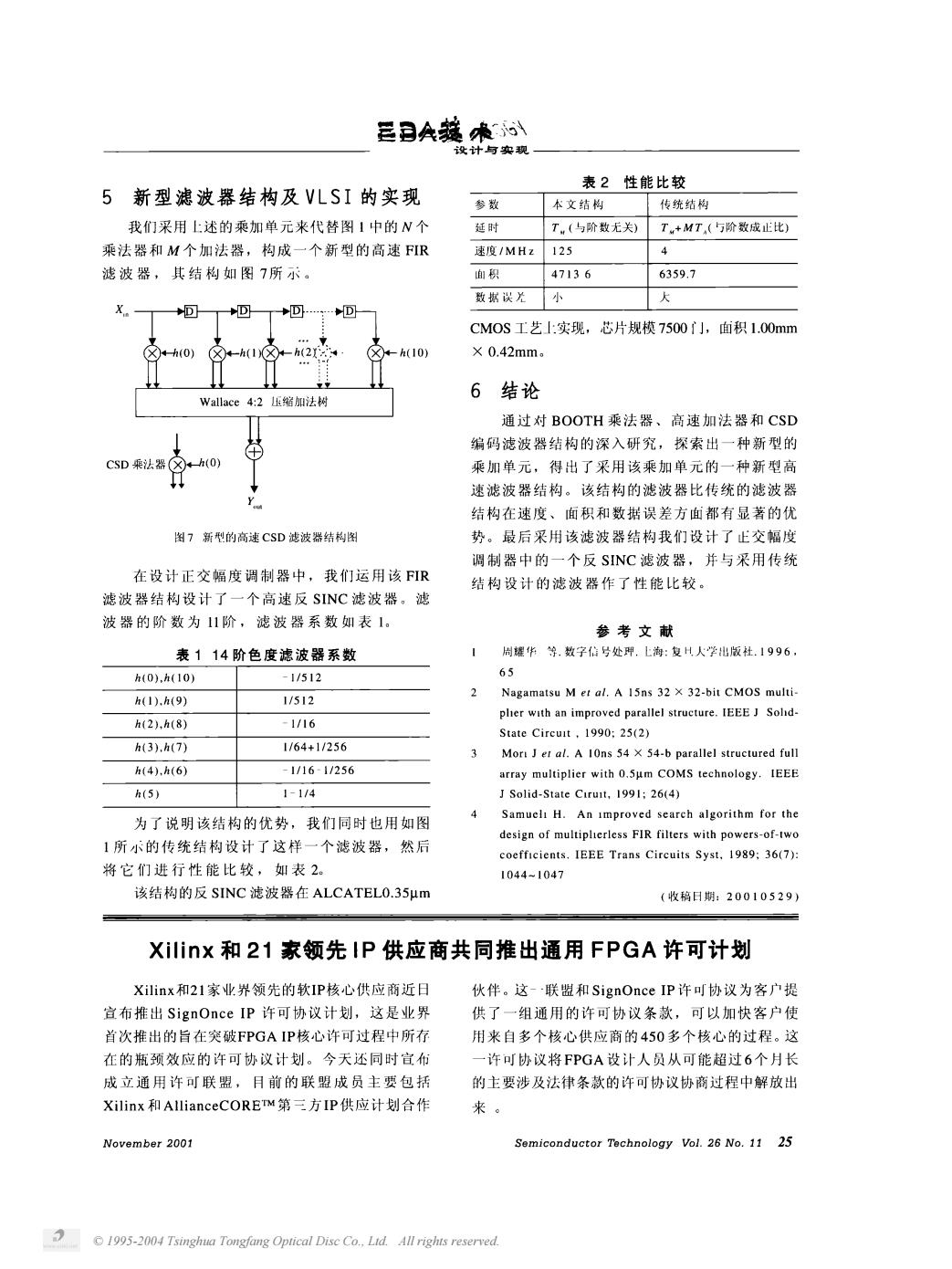

三目A接来\ 设计句实现 表2性能比较 5新型滤波器结构及VLSI的实现 参数 本文结构 传统结构 我们采用上述的乘加单元来代替图1中的N个 延时 T(马阶数无关) T+MT,(与阶数成止比) 乘法器和M个加法器,构成一个新型的高速FIR 速度1MHz 125 4 滤波器,其结构如图7所示。 血积 47136 6359.7 数据误片 小 D D CMOS工艺上:实现,芯片规模7500J,面积1.00mm h(0) h(2 h(10) ×0.42mm。 Wallace4:2压缩加法树 6结论 通过对BOOTH乘法器、高速加法器和CSD 编码滤波器结构的深入研究,探索出一种新型的 CSD乘法器 乘加单元,得出了采用该乘加单元的一种新型高 速滤波器结构。该结构的滤波器比传统的滤波器 结构在速度、面积和数据误差方面都有显著的优 图7新型的高速CSD滤波器结构图 势。最后采用该滤波器结构我们设计了止交幅度 调制器中的一个反SINC滤波器,并与采用传统 在设计正交幅度调制器中,我们运用该FIR 结构设计的滤波器作了性能比较。 滤波被器结构设计了一个高速反SINC滤波器,滤 波器的阶数为1阶,滤波器系数如表1。 参考文献 表114阶色度滤波器系数 1 周耀华等.数字信号处弹,上海:复H人学出版社.1996, h(0).h(10) -1/512 65 2 Nagamatsu M et al.A 15ns 32 X 32-bit CMOS multi- h(1).h(9) 1/512 phier with an improved parallel structure.IEEE J Sold- h(2),h(8) -1/16 State Circuit,1990;25(2) h(3),h(7) 1/64+1/256 3 Mort J er al.A 10ns 54 X 54-b parallel structured full h(4),h(6) -1/16-1/256 array multiplier with 0.5um COMS technology.IEEE h(5) 1-1/4 J Solid-State Ciruit,1991;26(4) 4 为了说明该结构的优势,我们同时也用如图 SamuelI H.An improved search algorithm for the design of multiplierless FIR filters with powers-of-two 1所小的传统结构设计了这样一个滤波器,然后 coefficients.IEEE Trans Circuits Syst,1989;36(7): 将它们进行性能比较,如表2。 1044-1047 该结构的反SINC滤波器在ALCATEL0.35μm (收稿日期:20010529) Xilinx和21家领先IP供应商共同推出通用FPGA许可计划 Xilinx和21家业养领先的软IP核心供应商近日 伙伴。这-~联盟和SignOnce IP许可协议为客户提 宣布推出SignOnce IP许可协议计划,这是业界 供了一组通用的许可协议条款,可以加快客户使 首次推出的旨在突破FPGA IP核心许可过程中所存 用来自多个核心供应商的450多个核心的过程。这 在的瓶颈效应的许可协议计划。今天还同时宣布 一许可协议将FPGA设计人员从可能超过6个月长 成立通用许可联盟,月前的联盟成员主要包括 的主要涉及法律条款的许可协议协商过程中解放出 Xilinx和AllianceCORETM第三方IP供应计划合作 来。 November 2001 Semiconductor Technology Vol.26 No.11 25 1995-2004 Tsinghua Tongfang Optical Disc Co..Lid.All rights reserved.© 1995-2004 Tsinghua Tongfang Optical Disc Co., Ltd. All rights reserved