正在加载图片...

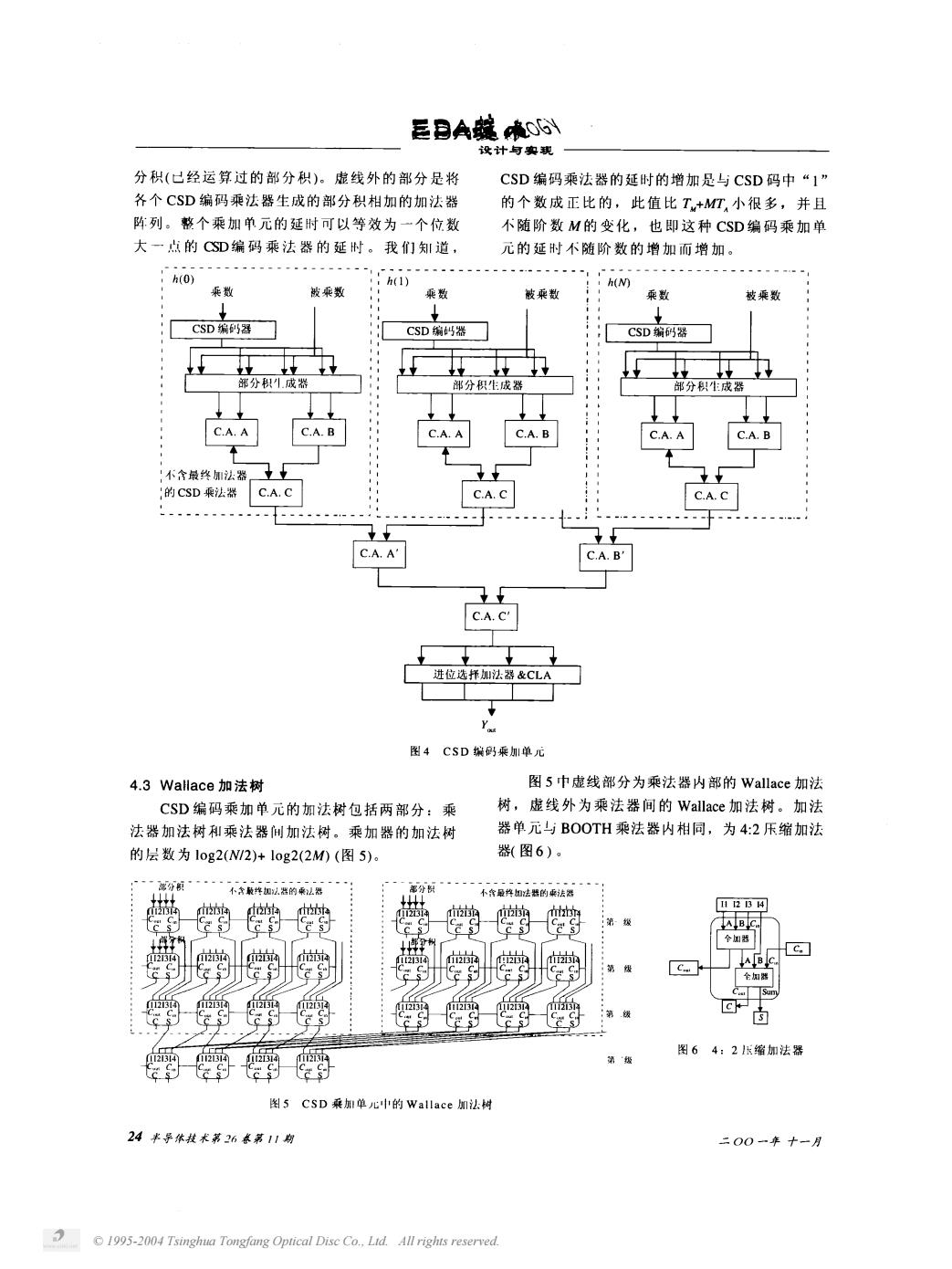

邑BA罐\ 设计与实现 分积(已经运算过的部分积)。虚线外的部分是将 CSD编码乘法器的延时的增加是与CSD码中“1” 各个CSD编码乘法器生成的部分积相加的加法器 的个数成正比的,此值比T+MT,小很多,并且 阵列。整个乘加单元的延时可以等效为一个位数 不随阶数M的变化,也即这种CSD编码乘加单 大一点的CSD编码乘法器的延时。我们知道, 元的延时不随阶数的增加而增加。 h(0) :h(1) h(N) 乘数 被乘数 乘数 被乘数 乘数 被乘数 CSD编码器 CSD编码器 CSD编码器 部分积1成器 部分积生成器 部分!生成器 C.A.B C.A.A 不含最终加法器 ,的CSD乘法器 C.A.C CA.B 进位选择加法器&CLA 图4CsD编码乘加1单元 4.3 Wallace加法树 图5中虚线部分为乘法器内部的Wallace加法 CSD编码乘加单元的加法树包括两部分:乘 树,虚线外为乘法器间的Wallace加法树。加法 法器加法树和乘法器间加法树。乘加器的加法树 器单元与B00TH乘法器内相同,为4:2乐缩加法 的层数为1og2(N/2)+1og2(2M)(图5)。 器(图6)。 ·部分积 不含敲加以器的乘器 部分积 不含最抖加法器的乘法器 H234 第级 全加器 c. 1234 学 全加器 Sam 123 1234 123 12 图6 4:2压缩加法器 112I314 1234 第 图5CSD乘加!单儿中的Wallace加让树 24半导体技术第26春第11期 二O0一年十一月 1995-2004 Tsinghua Tongfang Optical Disc Co..Ltd.All rights reserved.© 1995-2004 Tsinghua Tongfang Optical Disc Co., Ltd. All rights reserved