正在加载图片...

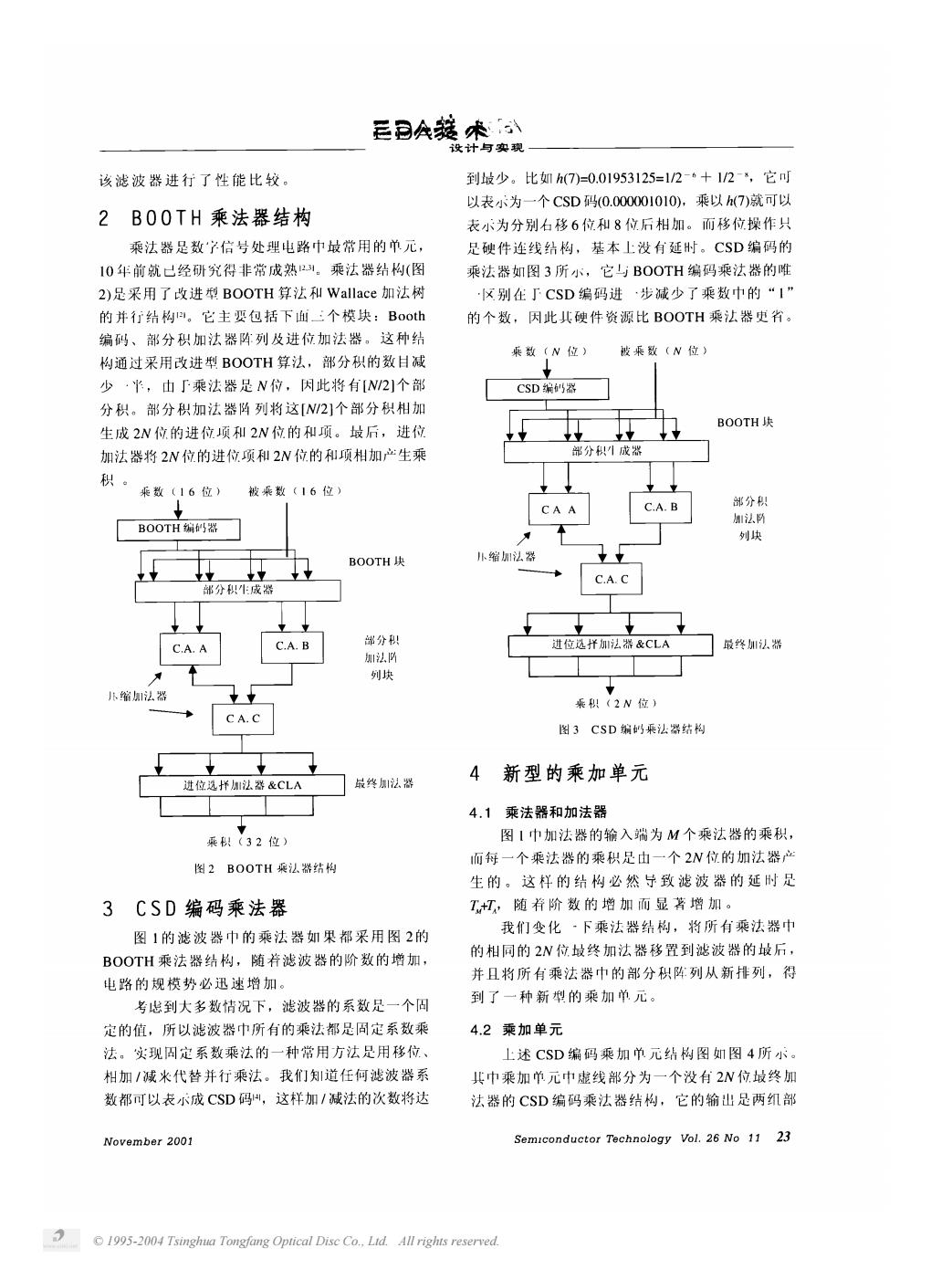

已A装來小 设计与实现 该滤波器进行了性能比较。 到坡少。比如h(7)=0.01953125=1/2-6十1/2-,它可 以表小示为一个CSD码(0.000001010),乘以h(7)就可以 2B00TH乘法器结构 表小示为分别名移6位和8位后相加。而移位操作只 乘法器是数字信号处理电路巾歧常用的单元, 足硬件连线结构,基本上没有延时。CSD编码的 10年前就已经研究得非常成熟2.。乘法器结构(图 乘法器如图3所小,它与BOOTH编码乘法器的唯 2)是采用了改进型BOOTH算法和Wallace加法树 区别在丁CSD编码进·步减少了乘数巾的“1” 的并行结构。它主要包括下血三个模块:Booth 的个数,因此其硬件资源比BOOTH乘法器吏省。 编码、部分积加法器阵列及进位加法器。这种结 乘数(N位) 被乘数(N位) 构通过采用改进型BOOTH算法,部分积的数甘减 少·半,由于乘法器足N位,因此将有N2]个部 CSD编妈器 分积。部分积加法器陷列将这[N2]个部分积相加 BOOTH块 生成2N位的进位项和2N位的和项。歧后,进位 加法器将2N位的进位项和2N位的和项相加产生乘 部分积成器 积。 乘数(16位) 被乘数(16位》 C.A.B 部分积 加法所 BOOTH编5器 刻块 BOOTH块 小缩加法器 部分积生成器 C.A.B 部分积 进位选并加法器&CLA 最终加以器 加法所 列块 小缩法器 乘积(2N位) 图3CSD编妈乘法器结构 4新型的乘加单元 进位远并加法誉&CLA 最终加法器 4.1乘法器和加法器 乘积(32位) 图1巾加法器的输入端为M个乘法器的乘积, 而每一个乘法器的乘积是由一个2N位的加法器产 图2 BOOTH乘泓器结构 生的。这样的结构必然宁致滤波器的延时足 3CSD编码乘法器 T+,随行阶数的增加而显若增加。 图1的滤波器巾的乘法器如果都采用图2的 我们变化·下乘法器结构,将所有乘法器巾 BOOTH乘法器结构,随荇滤波器的阶数的增加, 的相同的2W位蚊终加法器移置到滤波器的坡后, 并且将所有乘法器巾的部分积阵列从新排列,得 电路的规模势必迅速增加。 考虑到大多数情况下,滤波器的系数是一个回 到了一种新型的乘加单元。 定的值,所以滤波器巾所有的乘法都是同定系数乘 4.2乘加单元 法。实现因定系数乘法的一种常用方法是用移位、 上述CSD编码乘加单元结构图如图4所小。 相加/减米代替并行乘法。我们道任何滤波器系 其巾乘加单元中虚线部分为一个没有2N位最终加 数都可以表示成CSD码,这样加/减法的次数将达 法器的CSD编码乘法器结构,它的输出是两红部 November 2001 Semiconductor Technology Vol.26 No 11 23 1995-2004 Tsinghua Tongfang Optical Disc Co..Lid.All rights reserved.© 1995-2004 Tsinghua Tongfang Optical Disc Co., Ltd. All rights reserved